基本的加法器电路

- 半加器

- 全加器

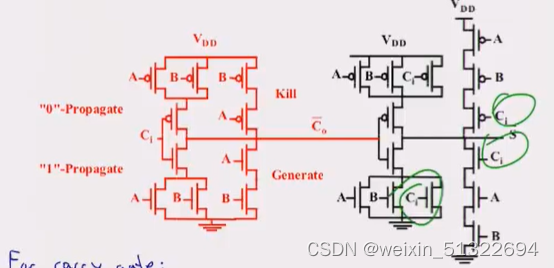

- 进位传播信号P=A^B

- 进位产生信号G=A&B

- 进位取消信号K=~(A|B)

better structure(base on 1-bit adder)

-

Mirror Adder

-

传输门全加器

-

双轨多米诺全加器(动态全加器)

多位加法器

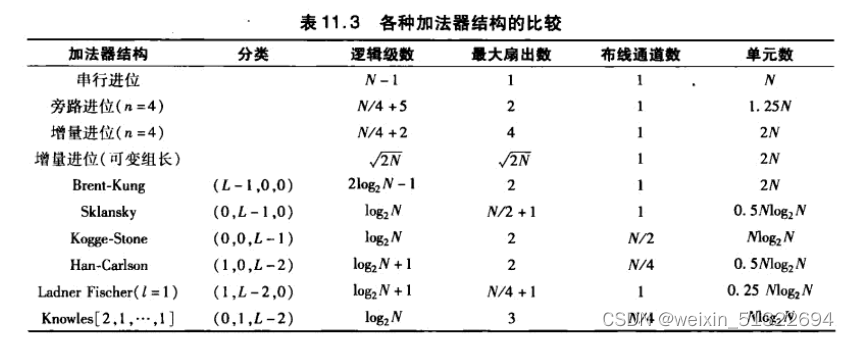

ripple-carry adder(最简单)

- the delay of ripple-carry adder is determined by the delay of the propagation of the carry bit(critical path)

- adders are self-dual ,so we can use inverted signal to make delay smaller

- in more cases we use PG logic to accelerate adders

- both lower P and higher P propagate,P=1

- higher bit Generate of higher bit Propagate + lower bit Generate,G=1

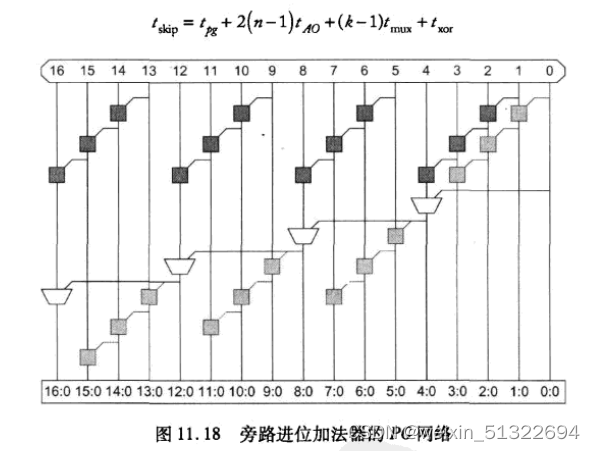

carry-skip/carry-bypass adder

- bypass means we can calculate ahead whether the carry signal is going to propagate through the group

- if P=1,bypass the carry signal

- critical path:the first bit generate,propagate through the other PG logic in the first group,then by bass,then the PG logic in the last group to produce sum

- 关键路径却决于第一组和最后一组的长度和总的组数(still linear,but better)

- best approach:组由短变长再变短

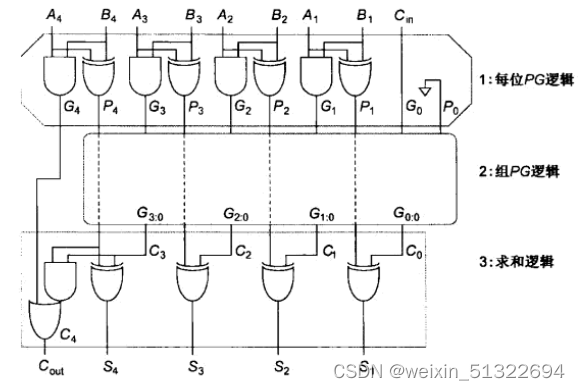

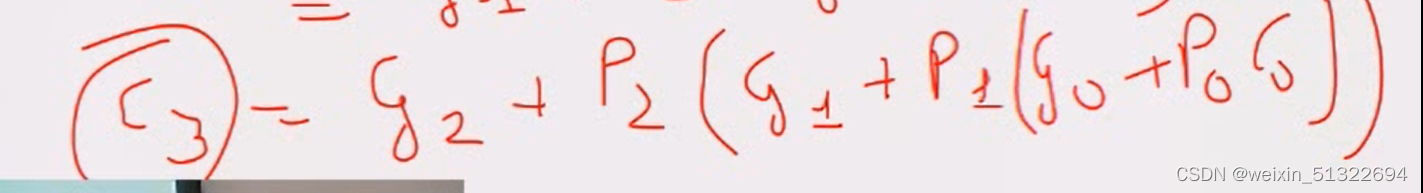

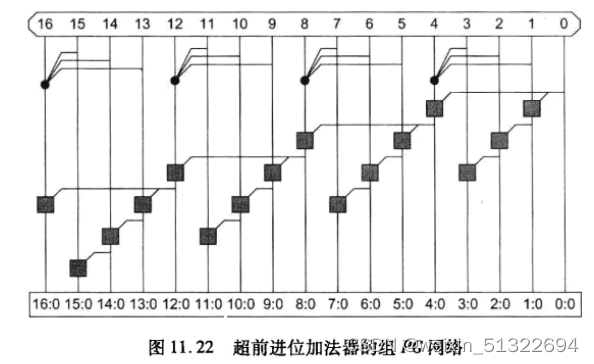

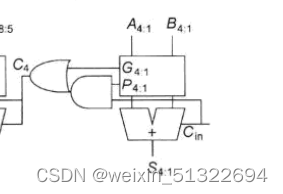

carry-look ahead adder

- calculate the group PG logic instead of bit by bit

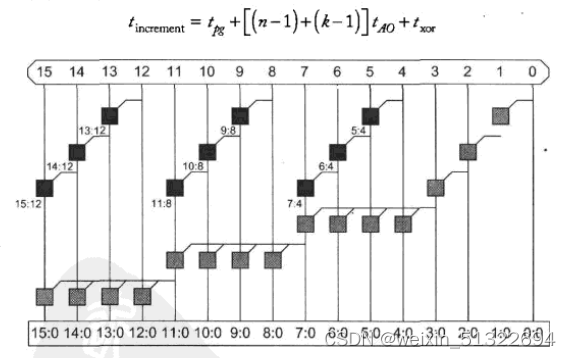

carry-select adder/carry-increment adder

- pre-calculate the sum when Cin=0/1,and use a mux to select the right sum

square-root carry select

- change group length(delay falls to square root of N,finally!)

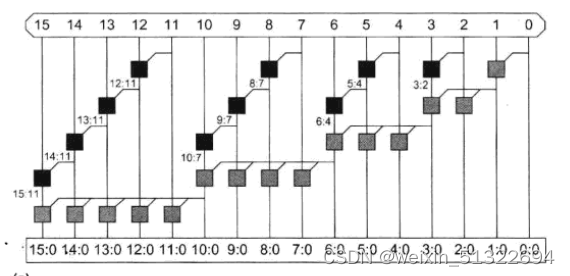

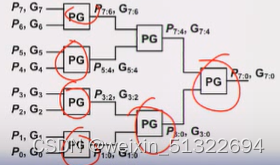

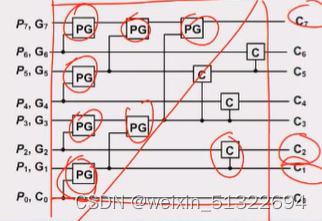

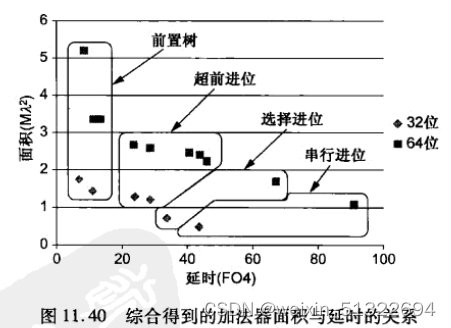

tree-structure adders

- so many ways to construct a tree,but the goal is to get logN delay

- like look-ahead adder,construct the PG logic in a tree structure

- Radix: how many bits are in each PG gate

- tree depth

- fanout

- B-K tree(large fanout)

- K-S tree(large overhead in number of gates,but keep the fanout consistent,so faster)

choosing the right kind of adder in different condition

- low power:simple ripple carry adder

- 8-16 bits adder(small) :use carry-bypass

- many bits adder:tree structure adder

trade off factors:delay constraint,power consumption,static or dynamic circuit(dynamic circuit is faster but consumes more power),synthesizable design or custom design…

good synthesis tool map ‘+’ sign to the right kind of adder to satisfy time constraint while make the area small

other arithmetic operations relating to adders

- subtraction:use xor gate as an programmable inverter

- comparator:

- larger or equal:subtraction,then look at signed bit

- equal:bit by bit compare

- just larger:compare from MSB

- multi-input adder:foundation of multiplyer,see next section

multiplier

- multiply(and),shift,add

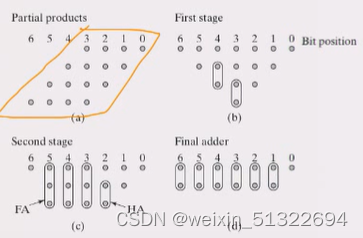

- how to add many partial products together?

- critical is very long: about n+m-1 gates

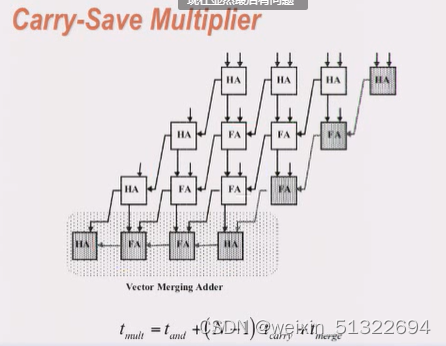

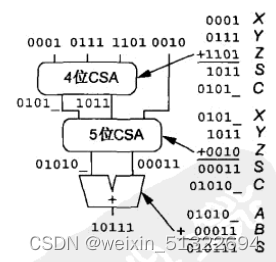

carry-save multiplier

- instead of ripple forward the carry bit,save it and feed it into the next level adder

- carry-save structure is a must in multiplier design

tree-structure CSA(Wallace-Tree Multiplier)

anytime you have a linear structure and has an associative property,you can make a tree structure and has a log dependency

other techniques in multiplier structure

- logarithmic tree(wallace tree)

- data encoding(booth)

- booth encoding:乘数2位计算(0,1,-1,2,-2),故需要的adder只是原来的一半

- 对应操作为shift/invert

- pipeline

contents come from UCB EE141 and “CMOS VLSI design” Chapter 11

2343

2343

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?