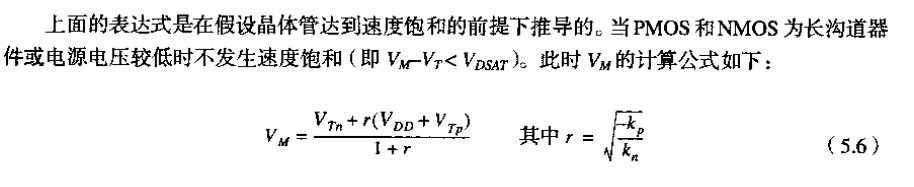

1. 开关阈值

对于长沟道晶体管器件:

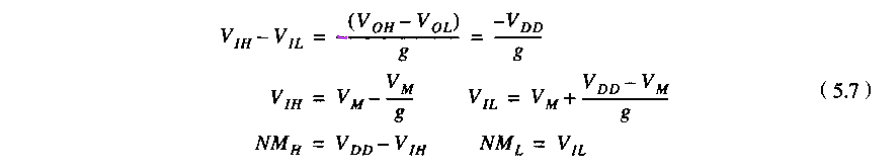

2. 噪声容限

对VTC进行线性近似,过渡区看作直线,增益为在开关阈值Vm处的增益

——器件参数变化对门的阈值影响很小

——对于固定的晶体管尺寸比,Vm近似正比于Vdd,但太低的电压对性能有影响

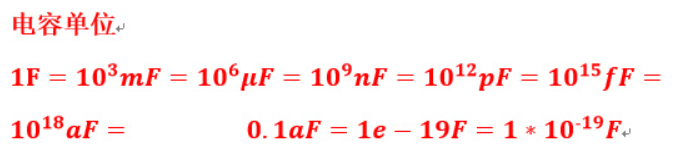

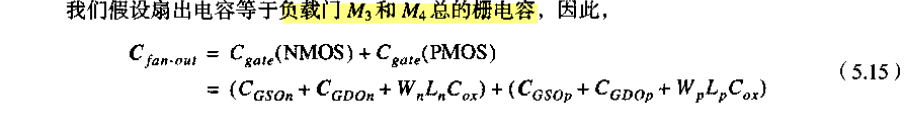

3. 动态特性 —— 电容

使CL尽可能小是实现高性能CMOS电路的关键 :

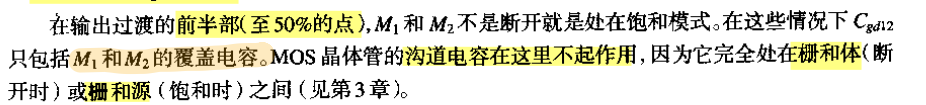

- 珊漏电容Cgd12 —— 覆盖电容

- 扩散电容Cdb1 Cdb2

- 连线电容 Cw

- 扇出的栅电容Cg3 Cg4

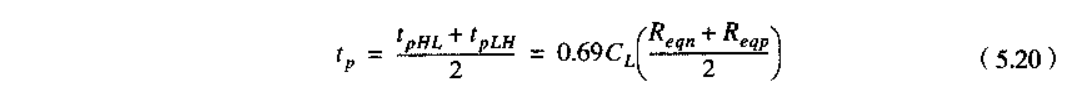

4. 动态特性 —— 传播延时

τ = RC为电路的时间常数,到达50%的时间是** t = ln(2)τ = 0.69τ **,10%到90%的为 t = ln(9)τ = 2.2τ

通过使Rn = Rp,来让上升下降传播延时相同。W/L可以控制R

通过使Rn = Rp,来让上升下降传播延时相同。W/L可以控制R

分析:

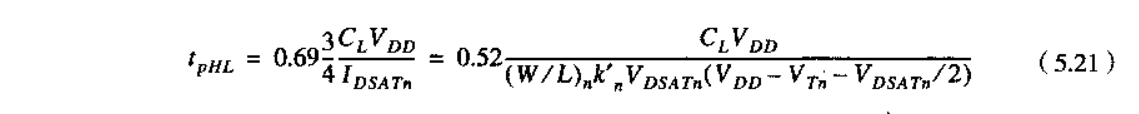

通过把tp展开,得到:

延时对于大的Vdd不敏感,但当Vdd接近2Vt的时候看到延时开始迅速增加

5. 传播时延优化分析

由上图可以得知,减少CL、增大W/L、提高VDD为优化时延的方法,下面进行分析

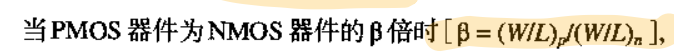

1. NMOS和PMOS之间尺寸的比

PMOS的尺寸增加因充电电流改善了tLH,但是因为电容变大影响了tHL

2.考虑反向器尺寸

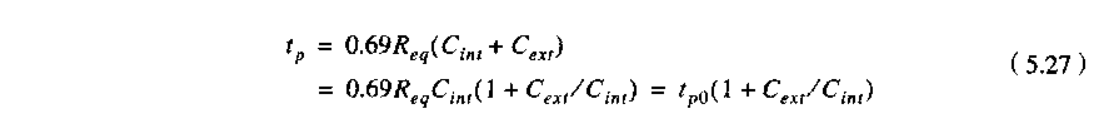

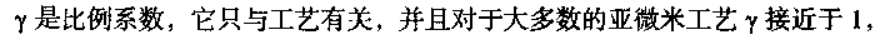

反向器也就是buffer由两个延迟决定,一个是本征Cint,一个是外部Cext

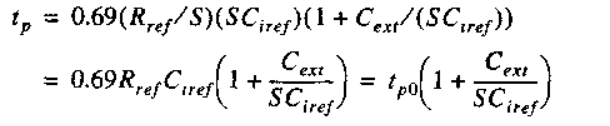

当反向器变化尺寸系数S的时候

3. 考虑整体 —— 反向器链

虽然S变大有助于减少单个反向器的时延,但是S会增大输入电容

输入栅电容Cg与本征输出电容Cint之间的关系为:

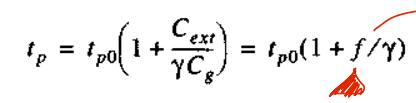

等效扇出:

有长连线的时候:

Cint和Cfan分别为本征电容和扇出电容

6. 动态功耗

对CMOS电路功耗起支配作用的是 由充电放电电容引起的动态功耗

EVDD为电源功耗,EC为电容功耗

同时还有直流通路引起的功耗为:

9265

9265

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?