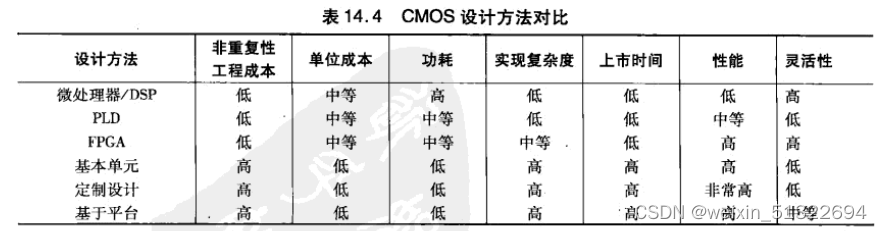

the following methodologies are arranged by their prices.

- microprocessor/DSP

- the most practical way is to use ready-to-use microprocessor or (for signal-intensive problems) DSP.

- development in software,very flexible

- programmable logic

- faster than general microprocessor,cheaper than ASIC

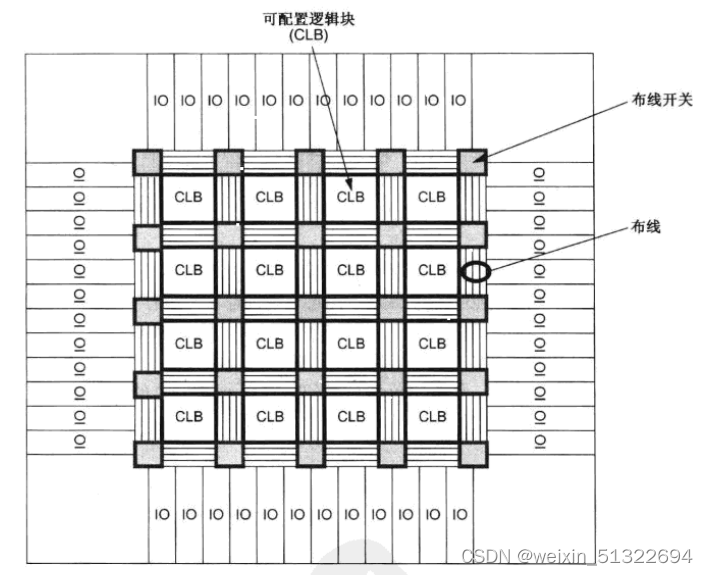

- PLA,FPGA

gate arrays/SOG(sea-of-gates)

- gate array pre-place gates and require routing in the design

- SOG pre-place NMOS and PMOS and require routing in the design

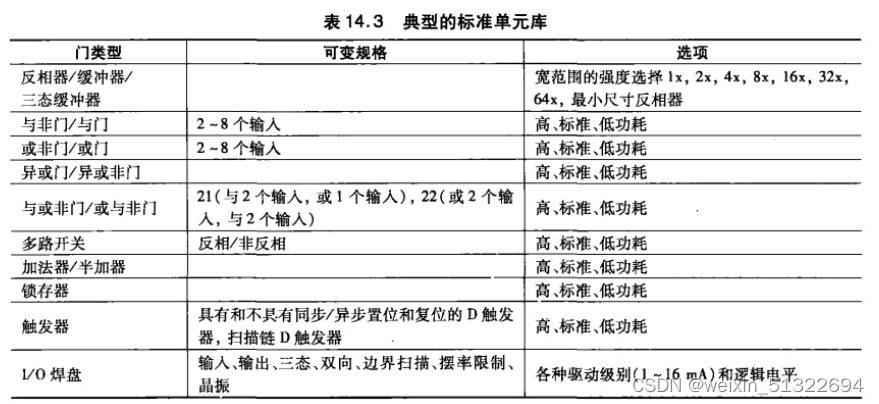

standard-cell based design

- smaller area,faster,lower power than above method but higher NRE,thus often used in large-scale production

- standard cell has fixed heights and configurable width,so we can put power rails on the top and bottom of them

- we can also routing the clock tree and power,ground

full-custom design

in standard-cell based design era,most of digital CMOS IC do not use full-custom design,but analog and RF design still use full-custom methodology.

- in speed full-custom design microprocessor is many times faster than standard-cell based ones,the situation is the same in power consumption

- but with better EDA tools and better standard cell library,we can gradually close the performance gap.

707

707

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?