1、Why need DFT

1.1、DPM(Defective parts per million)

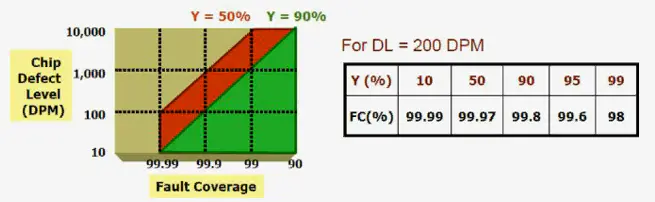

测试后的缺陷率:Defect level(DL)

测试覆盖率:Fault coverge(FC)

生产过程良率:Process Yield(Y)

DL = 1 -

Y

(

1

−

F

C

)

Y^{(1-FC)}

Y(1−FC)

对于VLSI芯片,200 DPM对于一般应用是可以接受的,更低表示高品质。

2、What is DFT

2.1、Boundary Scan

利用TCK、TMS、TDO、TDI、TRST(Optional)等信号进行Bscan测试。

2.2、BIST

2.2.1、MBIST(Memory BIST)

MBIST只用于存储器测试,典型的MBIST包含测试电路用于加载,读取和比较测试图形。

2.2.2、LBIST(Logic BIST)

LBIST通常用于测试随机逻辑电路,一般采用一个伪随机测试图形生成器来产生输入测试图形,应用于器件内部机制;而采用多输入寄存器(MISR)作为获得输出信号产生器。

2.2.3、Analog BIST

Analog BIST则用于模拟电路的自我测试。基于各种算法生成多种测试向量,每种有不同针对的电路错误类型。

2.3、Scan

2.3.1、Stuck_At Fault(单固定型故障模型)

2.3.2、Transition Delay Model(跳变延时故障模型)

2.3.3、Path Delay Model(路径延时故障模型)

2.3.4、Bridge(桥接故障模型)

桥接故障模型通俗的讲就是两根不应该接到一起的信号线意外的连接到了一起。最常见的桥接故障就是两根信号线短路。

桥接故障可分为三种类型:输入桥接故障,反馈桥接故障,非反馈桥接故障。

好的Routing可以有效的减少桥接故障,两根信号线如果Routing比较远的话,就不会发生桥接故障,如果距离近,就有可能发生。

2.4、IDDQ(Integrated Circuit Quiescent Current)

测试条件:

- Reset Bar拉低,芯片处于Reset状态;

- DFT test mode处于IDDQ mode;

- 各个Power Pin连接相应的Power上;

- 普通IO处于Floating状态或输入测试Pattern??

2133

2133

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?