在模块化原理图时,PCB也需要做一个模块.mdd文件。这时需要先画好图纸然后再制作模块化文件。

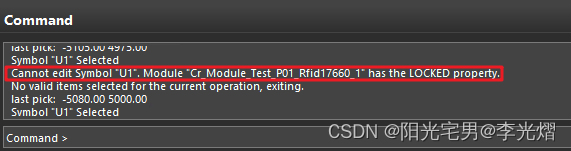

修改文件时会发现模块化器件报错,无法编辑模块内部器件和走线,器件和走线都被LOCKED,如下所示报错内容:

Symbol "U1" Selected

Cannot edit Symbol "U1". Module "Cr_Module_Test_P01_Rfid17660_1" has the LOCKED property.

No valid items selected for the current operation, exiting.

Cannot edit Connect Line "N01376, Etch/Top". Module "Cr_Module_Test_P01_Rfid17660_1" has the LOCKED property.

No element found.

那怎么怎么解除呢?

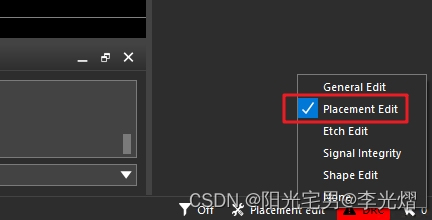

首先选择编辑模式为Placement Edit模式。

选择Groups

订阅专栏 解锁全文

订阅专栏 解锁全文

2107

2107

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?