I2C 通信总线是电子设计中常见的总线之一,由于 I2C 的硬件芯片内部为开漏输出,所以要求在外部增加一个上拉电阻,总线上拉电阻的选取受多个因素的影响,因此如何计算 I2C 总线的上拉电阻阻值成为硬件工程师在使用 I2C总统时需要关注的话题。

从本质上讲: I2C 总线电容和上升时间和总线电容决定上拉电阻的最大值, I2C器件开漏接口导通电阻决定上拉电阻的最小值。

I2C状态分析

总线由低到高

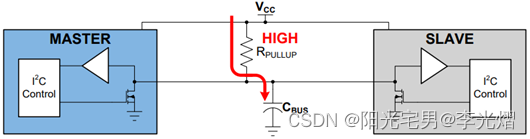

由于 I2C 器件的硬件结构为开漏,所以当 IIC 总线电平由低到高时,I2C 器件(同一时刻,可以是 I2C 主机,也可以是 I2C 从机)释放总线电平,即内部的 MOSFET 关闭。此时Vcc 经过上拉电阻对 I2C 总线寄生电容充电,直至到达 Vcc。

在文章【通信专题】I2C通信硬件概述我们说到I2C总线电容Cbus由很多因素,如各器件的寄生电容、走线寄生电容等。这些寄生电容共同组成 I2C 总线的电容,I2C 主机和从机越多,I2C 总线上的电容就越大。

本文详细介绍了I2C通信中上拉电阻的选择与计算方法,包括上拉电阻最大值和最小值的确定,以及与总线电容、通信速度和功耗的关系。通过对I2C总线电平变化的分析,阐述了上拉电阻对通信性能的影响,并给出了实际的计算案例。

本文详细介绍了I2C通信中上拉电阻的选择与计算方法,包括上拉电阻最大值和最小值的确定,以及与总线电容、通信速度和功耗的关系。通过对I2C总线电平变化的分析,阐述了上拉电阻对通信性能的影响,并给出了实际的计算案例。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

437

437

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?