GENERAL DESCRIPTION:

AD9910是一种直接数字合成器(DDS),具有集成的14位DAC,并支持高达1 GSPS的采样率。AD9910采用先进的专有DDS技术,可以在不影响性能的情况下显著降低功耗。DDS/DAC组合形成了一种数字可编程、高频、模拟输出合成器,能够在高达400 MHz的频率范围内生成频率敏捷的正弦波形。

用户可以访问控制DDS的三个信号控制参数: 频率、相位和幅度。DDS使用32位累加器提供快速频率跳变和频率调谐分辨率。在1 GSPS采样率下,调谐分辨率约为0.23 Hz。DDS还具有快速相位和幅度切换能力。

通过串行I/O端口编程其内部控制寄存器,即可控制AD9910。AD9910包括一个集成的静态RAM,以支持各种频率、相位和/或幅度调制组合。AD9910还支持用户定义的数字控制数字斜坡模式操作。在此模式下,可以线性地随时间变化频率、相位或幅度。为了实现更高级的调制功能,AD9910还包括一个高速并行数据输入端口,以实现直接频率、相位、幅度或极性调制。

引脚:

操作原理:

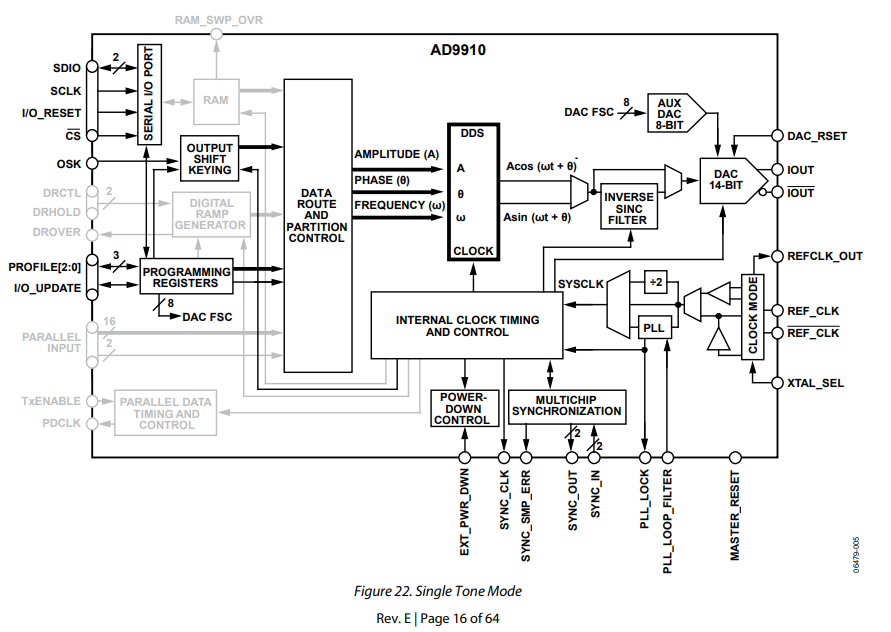

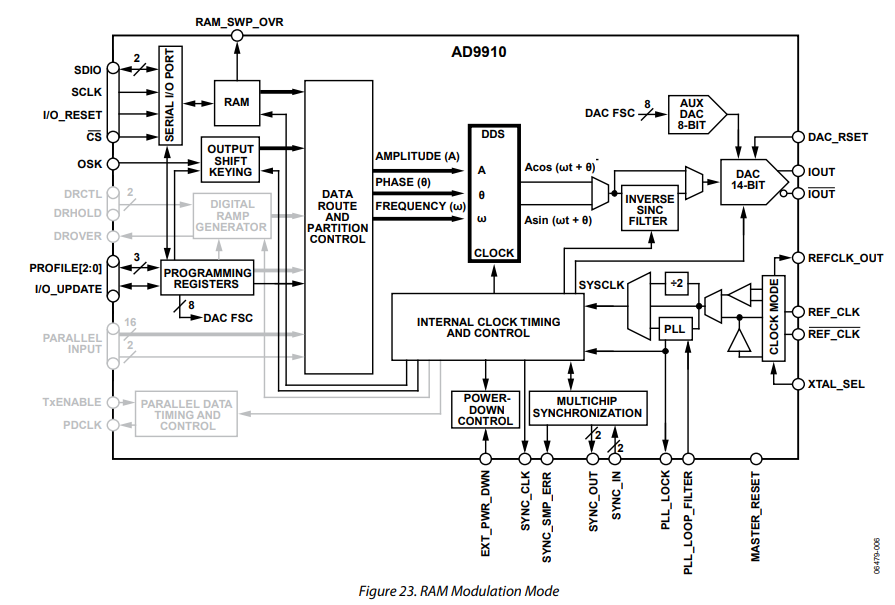

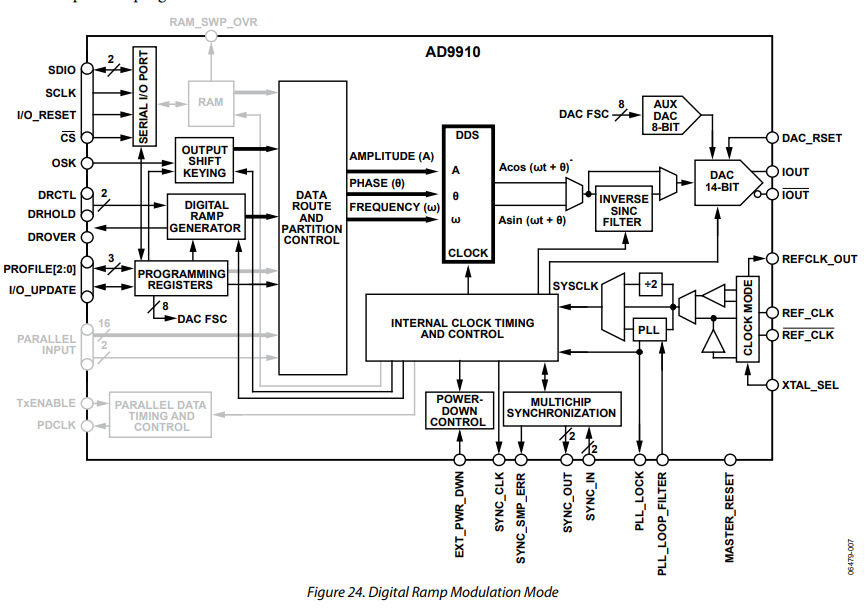

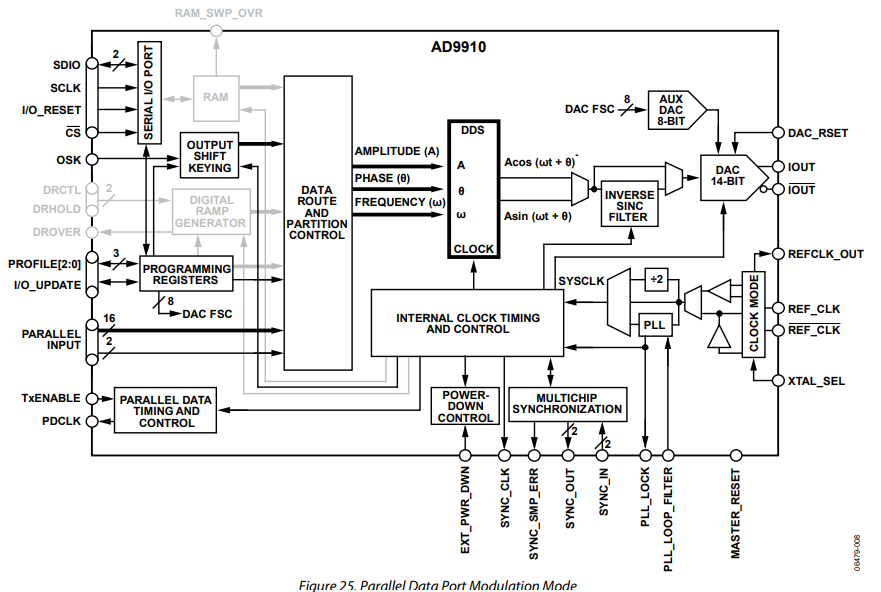

AD9910有四种操作模式。 • 单频 • RAM调制 • 数字斜坡调制 • 并行数据端口调制

这些模式与用于提供DDS信号控制参数(频率、相位或幅度)的数据源相关联。根据模式和/或特定的控制比特,自动地将数据分割成不同组合的频率、相位和幅度。

在单频模式下,DDS信号控制参数直接来自与串行I/O端口相关联的编程寄存器。在RAM调制模式下,DDS信号控制参数存储在内部RAM中,并在命令下回放。在数字斜坡调制模式下,DDS信号控制参数由数字斜坡发生器提供。在并行数据端口调制模式下,DDS信号控制参数直接驱动到并行端口。

各种调制模式通常只对DDS信号控制参数中的一个进行操作(在极性调制格式的情况下为两个)。未调制的DDS信号控制参数存储在其相应的编程寄存器中,并根据所选的模式自动路由到DDS。

此外,还提供了独立的输出移相键控(OSK)功能。该功能使用一个单独的数字线性斜坡发生器,仅影响DDS的幅度参数。OSK功能优先于其他可以驱动DDS幅度参数的数据源。因此,在启用OSK功能时,没有其他数据源可以驱动DDS的幅度参数。

虽然各种模式(包括OSK功能)被独立描述,但它们可以同时启用。这为产生复杂的调制方案提供了前所未有的灵活性。但是,为了避免多个数据源驱动同一DDS信号控制参数,该设备具有内置的优先协议(请参见模式优先级部分中的表5)。

单频模式:

在单频模式下,DDS信号控制参数直接从编程寄存器中提供。一个profile是一个独立的寄存器,包含DDS信号控制参数。共有八个profile寄存器。每个profile都是独立可访问的。使用三个外部profile引脚(PROFILE[2:0])选择所需的profile。当profile引脚状态改变并与SYNC_CLK上升沿同步时,DDS将使用所选profile指定的参数进行更新 。

。

RAM调制模式:

RAM调制模式(参见图23)通过RAM启用比特和I/O_UPDATE引脚(或profile更改)的断言来激活。在此模式下,DDS调制信号控制参数直接从RAM中提供。RAM由32位字组成,深度为1024个字。与复杂的内部状态机配合使用,RAM提供了一种非常灵活的方法来生成任意的、时间相关的波形。可编程定时器控制从RAM中提取字进行传递到DDS的速率。因此,可编程定时器建立了32位样本被供应到DDS的采样率。

RAM调制模式中,用作RAM样本目标的特定DDS信号控制参数的选择也是通过八个独立的RAM profile寄存器可编程实现的。使用三个外部profile引脚(PROFILE[2:0])来选择一个特定的profile。当profile引脚状态改变并与SYNC_CLK上升沿同步时,选中的RAM profile将被激活。在RAM调制模式中,生成时间相关的幅度、相位或频率信号的能力使得可以调制控制DDS载波信号的任何参数之一。此外,还提供了极性调制格式,将每个RAM样本分为幅度和相位两个部分;16位分配给相位,14位分配给幅度。

数字斜坡调制模式:

在数字斜坡调制模式(参见图24)下,调制的DDS信号控制参数直接从数字斜坡发生器(DRG)提供。斜坡生成参数通过串行I/O端口进行控制。斜坡生成参数允许用户控制斜坡的上升和下降斜率。斜坡的上界和下界、上升部分的步长和步速,以及下降部分的步长和步速都是可编程的。

斜坡以32位输出分辨率数字生成。DRG的32位输出可以编程表示频率、相位或幅度。当编程表示频率时,使用所有32位。然而,当编程表示相位或幅度时,仅使用16位MSB或14位MSB。

斜坡方向(上升或下降)由DRCTL引脚进行外部控制。另外一个引脚(DRHOLD)允许用户挂起斜坡发生器在其当前状态下的运行。

并行数据端口调制模式:

在并行数据端口调制模式(参见图25)下,调制的DDS信号控制参数直接从18位并行数据端口提供。数据端口分为两个部分。16个MSB组成16位数据字(D[15:0]引脚),2个LSB组成2位目标字(F[1:0]引脚)。目标字定义了如何将16位数据字应用于DDS信号控制参数。表4定义了目标位、16位数据字的分区以及数据目标(按DDS信号控制参数计)之间的关系。无论目标如何,16位数据字的格式都是无符号二进制。

当目标位指示数据字作为DDS频率参数时,16位数据字用作FTW寄存器中32位频率调谐字的偏移量。这意味着必须以某种方式将16位数据字与FTW寄存器中的32位字正确对齐。这是通过编程寄存器中的4位FM增益字来实现的。FM增益字允许用户对16位数据字应用加权因子。在默认状态下(0),16位数据字和FTW寄存器中的32位字LSB对齐。每次FM增益字值的增加将使16位数据字相对于FTW寄存器中的32位字向左移动,将16位数据字对FTW寄存器定义的频率的影响增加了两倍。FM增益字有效地控制由数据字跨越的频率范围。

并行数据时钟(PDCLK):

AD9910在PDCLK引脚上生成一个时钟信号,该信号以DAC采样率的1/4运行(并行数据端口的采样率)。PDCLK作为并行端口的数据时钟。默认情况下,PDCLK的每个上升沿用于将18位用户提供的数据存储到数据端口中。可以通过PDCLK反转比特更改边沿极性。此外,可以使用PDCLK启用比特关闭PDCLK输出信号。但是,即使关闭了输出信号,它仍然在内部使用内部PDCLK定时捕获并行端口上的数据。请注意,PDCLK在禁用时为逻辑0。

表4.并行端口目标位

| F[1:0] | D[15:0] | 参数 | 备注 |

|---|---|---|---|

| 00 | D[15:2] | 14位幅度参数(无符号整数) | 幅度范围从0到1-2^(-14),D[1:0]未使用。 |

| 01 | D[15:0] | 16位相位参数(无符号整数) | 相位偏移范围为0到2π(1-2^(-16))弧度。 |

| 10 | D[15:0] | 32位频率参数(无符号整数) | 通过编程寄存器中的4位FM增益字控制16位数据字与32位频率参数的对齐。 |

| 11 | D[15:8] D[7:0] | 8位幅度参数(无符号整数) 8位相位参数 | 数据字幅度的MSB与DDS 14位幅度参数的MSB对齐。DDS幅度参数的6个LSB被分配给ASF寄存器的Bits[5:0]。结果的14位字将幅度缩放从0到1-2^(-14)。 D[7:0]是8位相位参数,其MSB与DDS 16位相位参数的MSB对齐。DDS相位参数的8个LSB从POW寄存器的Bits[7:0]分配。结果的16位字使相位偏移从0到2π(1-2^(-16))弧度。 |

传输使能信号(TxENABLE):

AD9910还接受应用于TxENABLE引脚的用户生成信号,该信号作为用户提供数据的门控。默认情况下,TxENABLE被认为是逻辑1为真,逻辑0为假。然而,可以使用TxENABLE反转位来反转此引脚的逻辑行为。当TxENABLE为真时,设备会在预期的PDCLK边沿(基于PDCLK反转位)上将数据锁存到设备中。当TxENABLE为假时,即使PDCLK可能继续操作,设备也会忽略提供给端口的数据。此外,当TxENABLE引脚保持为假时,设备会内部清除16位数据字,或者保留TxENABLE切换到假状态之前数据端口上存在的最后一个值(基于数据组合器保留最后一个值位的设置)。

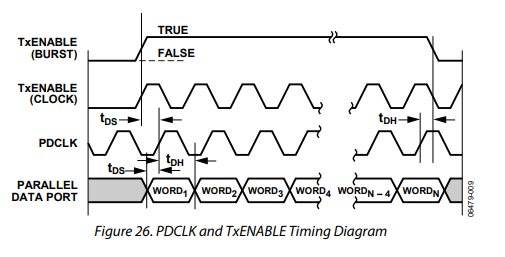

作为TxENABLE引脚的替代,用户可以使用以并行端口数据速率运行的时钟信号来驱动TxENABLE引脚,而非将其作为门控。当由时钟信号驱动时,从假状态到真状态的转换必须在每个周期上满足所需的建立时间和保持时间,以确保正确操作。 TxENABLE和PDCLK的时序如图26所示。

"模式优先级":

三种不同的调制模式会产生频率、相位和/或幅度数据,用于控制DDS信号的参数。此外,开关键控(OSK)功能会生成用于DDS的幅度数据。每个这些功能可通过串行I/O端口使用适当的控制位独立调用。

独立激活每个功能使得多个数据源尝试驱动相同的DDS信号控制参数成为可能。为了避免冲突,AD9910具有内置的优先级系统。表5总结了每个DDS信号控制参数的优先级。表5的行按优先级递减的顺序列出了特定DDS信号控制参数的数据源。例如,如果RAM和并行端口都启用,并且两者都被编程为将频率作为目标,则DDS频率参数由RAM驱动而不是并行数据端口。

| 优先级 | DDS信号控制参数 | 频率数据源条件 | 相位数据源条件 | 幅度数据源条件 |

|---|---|---|---|---|

| 最高优先级 | RAM | RAM已启用且数据目的地为频率 | RAM已启用且数据目的地为相位或极形 | - |

| OSK发生器 | OSK已启用(自动模式) | - | - | |

| DRG | DRG已启用且数据目的地为频率 | DRG已启用且数据目的地为相位 | DRG已启用且数据目的地为幅度 | |

| ASF寄存器 | OSK已启用(手动模式) | - | - | |

| 并行数据端口和FTW寄存器 | 并行数据端口已启用并且数据目的地为频率 | 并行数据端口已启用并且数据目的地为相位 | - | |

| 第二优先级 | RAM | - | - | RAM已启用且数据目的地为幅度或极形 |

| FTW寄存器 | RAM已启用且数据目的地为相位、幅度或极形 | - | - | |

| 并行数据端口和POW寄存器LSB串联 | - | - | 并行数据端口已启用并且数据目的地为极形 | |

| 第三优先级 | DRG | - | DRG已启用且数据目的地为相位或幅度 | DRG已启用且数据目的地为频率或幅度 |

| FTW处于活动单音调配置寄存器中 | DRG已启用且数据目的地为相位或幅度 | DRG已启用且数据目的地为频率或幅度 | - | |

| POW寄存器 | RAM已启用且数据目的地为频率或幅度 | - | RAM已启用且数据目的地为频率或幅度 | |

| 并行数据端口 | 并行数据端口已启用并且数据目的地为幅度 | 并行数据端口已启用并且数据目的地为相位、幅度或极形 | 并行数据端口已启用并且数据目的地为幅度 | |

| 第四优先级 | FTW在活动单音调配置寄存器中 | POW在活动单音调配置寄存器中 | - | 并行数据端口已启用并且数据目的地为极形 |

| ASF在活动单音调配置寄存器中 | - | - | 并行数据端口已启用并且数据目的地为相位、幅度或极形 | |

| POW在活动单音调配置寄存器中 | - | - | - | |

| 最低优先级 | 无 | 无 | 无 | 无 |

"功能模块细节":

DDS CORE(“数据分发服务核心)

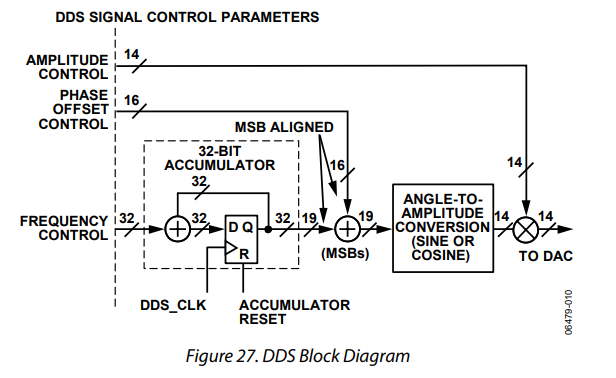

直接数字合成器(DDS)块生成一个参考信号(基于CFR1 [16],选择DDS正弦输出位)。参考信号的参数(频率、相位和幅度)被应用于DDS的频率、相位偏移和幅度控制输入,如图27所示。

AD9910的输出频率(fOUT)是由DDS的频率控制输入处的频率调谐字(FTW)所控制的。fOUT、FTW和fSYSCLK之间的关系可以用以下公式表示:

fOUT = (FTW × fSYSCLK)/(2^32) (1)

其中,FTW是一个32位整数,它的取值范围为0到2^32-1,fSYSCLK是DDS系统时钟的频率。这个公式表明,通过控制FTW值,可以实现对输出频率fOUT的精确控制,从而实现高精度的频率合成。

为了生成一个所需的输出频率fOUT,可以通过解方程1得到所需的FTW值,具体计算公式如下(即方程2):

FTW = round((fOUT × 2^32) / fSYSCLK)

其中,round(x)函数将参数x四舍五入到最接近的整数。这是因为FTW必须是一个整数值。例如,对于fOUT = 41 MHz和fSYSCLK = 122.88 MHz,则FTW = 1,433,053,867(0x556AAAAB)。

如果编程的FTW大于2^31,则会产生混频图像,它出现的频率由下式给出:

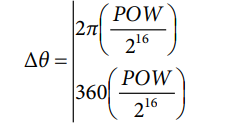

DDS信号的相对相位可以通过16位相位偏移字(POW)进行数字控制。在DDS核心内部的角度到幅度转换块之前,会应用相位偏移。相对相位偏移(Δθ)由下式给出:

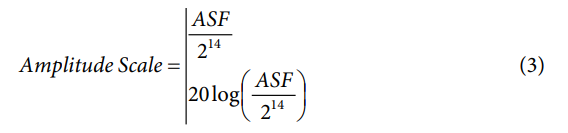

DDS信号的相对幅度可以通过14位幅度缩放因子(ASF)进行数字缩放,相对于全幅度而言。幅度缩放值应用在DDS核心内部的角度到幅度转换块的输出端。幅度缩放由以下公式给出:

上述公式中,上面的量是以弧度为单位表示相位偏移,下面的量是以度数表示相位偏移。要找到产生任意Δθ所需的POW值,可以通过解方程式求得POW,并舍入结果(类似于之前描述的找到任意FTW的方法)。

上述公式中,上面的量是相对于完全幅度的幅度表达为分数,下面的量则表示以分贝为单位相对于完全幅度。要找到特定缩放因子所需的ASF值,可以通过解方程3得到ASF,并舍入结果(类似于之前描述的找到任意FTW的方法)。

当AD9910被编程以调制任何DDS信号控制参数时,最大调制采样率为1/4 fSYSCLK。这意味着调制信号会在¼ fSYSCLK的倍数处产生图像。在使用该器件作为调制器时,必须考虑这些图像的影响。

14-BIT DAC OUTPUT:("14位数模转换器输出")

AD9910集成了一个14位电流输出DAC。该输出电流通过两个输出以平衡信号的形式传递。采用平衡输出可减少DAC输出处存在的共模噪声数量,从而提高信噪比。连接在DAC_RSET引脚和AGND之间的外部电阻(RSET)建立参考电流。DAC的满量程输出电流(IOUT)是参考电流的缩放版本(参见Auxiliary DAC部分)。建议使用10 kΩ的RSET值。应注意负载终端以保持输出电压在指定的合规范围内;超出此范围产生的电压会导致过度失真并可能损坏DAC输出电路。

Auxiliary DAC("辅助数字模拟转换器)

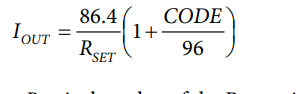

一个8位的辅助数字模拟转换器(Auxiliary DAC)控制主DAC(IOUT)的满量程输出电流。存储在适当的寄存器映射位置中的8位代码字根据以下公式设置IOUT:

其中,RSET是RSET电阻的值(单位为欧姆),CODE是提供给辅助DAC的8位值(默认值为127)。例如,当RSET = 10,000Ω且CODE = 127时,则IOUT = 20.07 mA。

INVERSE SINC FILTER("反Sinc滤波器")

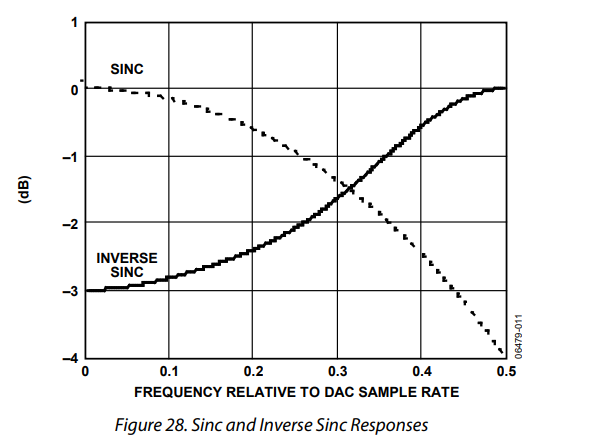

采样的载波数据流是集成在AD9910中的数字模拟转换器(DAC)的输入。由于与DAC生成的信号相关的零阶保持效应,DAC输出频谱被特征sin(x)/x(或sinc)包络所塑造。由于其形状已知,因此可以对Sinc包络进行补偿。这个包络恢复函数由位于DAC之前的反Sinc滤波器提供。反Sinc滤波器实现为数字FIR滤波器。它的响应特性几乎与Sinc包络的反响应完全匹配。反Sinc滤波器的响应曲线如图28所示(与Sinc包络进行比较)。

反Sinc滤波器可以通过CFR1[22]进行启用。滤波器的系数在表6中给出。该滤波器通过在到达DAC之前对数据进行扭曲,以补偿会扭曲频谱的Sinc包络而运行。

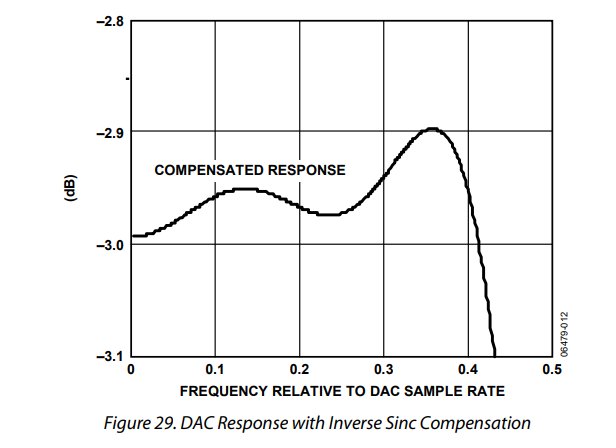

当启用反Sinc滤波器时,它会引入约3.0 dB的插入损耗。反Sinc补偿对于输出频率高达DAC采样率的40%左右是有效的。

表6. 反Sinc滤波器的滤波器系数

| 序号 | 系数值 |

|---|---|

| 1, 7 | -35 |

| 2, 6 | +134 |

| 3, 5 | -562 |

| 4 | +6729 |

在图28中,Sinc包络会引入频率依赖的衰减,在奈奎斯特频率(DAC采样率的一半)处最多可达到4 dB。如果没有反Sinc滤波器,则DAC输出会受到Sinc包络的频率依赖下降的影响。反Sinc滤波器有效地将下降幅度平坦至±0.05 dB以内,如图29所示,该图显示启用反Sinc滤波器的校正后Sinc响应。

-------------------------------------------23页--------------------------------------------------------------

2154

2154

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?