前言

使用FPGA与DS18B20进行通信,显示温度信息处理过程。

一、DS18B20简介

这里主要介绍一下所使用的单总线协议和使用的操作流程。关于DS18B20详细信息可查阅相关手册进行了解。

单总线协议

单总线协议适用于单个主机系统,能够控制一个或多个从机设备。

**硬件结构:**设备(主机或者从机)通过一个漏极开路或三态端口,连接至数据线,这样允许设备在不发送数据时释放数据总线,以便总线被其它设备所使用。

命令序列典型的单总线命令序列如下:

1.初始化。

2.ROM命令

3.功能命令

访问单总线器件,必须严格遵守这个命令序列,如果出现混乱,单总线器件则不会响应主机。

信号方式:单总线器件要求采用严格的通信协议,以保证数据完整性,该协议定义了几种信号类型:复位脉冲、应答脉冲、写0、写1、读0和读1.除了应答脉冲外,都由主机发出同步信号,并且是低位先发。

1.初始化序列:复位和应答脉冲

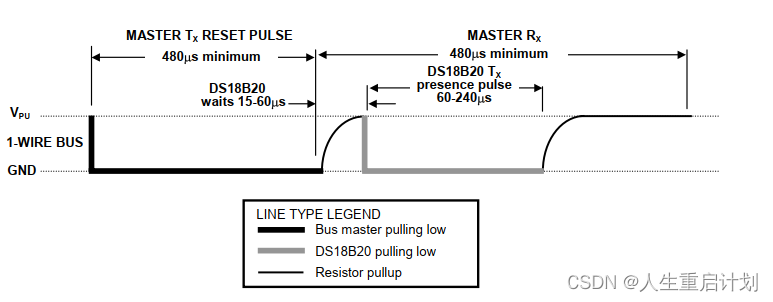

单总线上所有的通信都是以初始化序列开始:主机发出复位脉冲及从机的应答脉冲,如下图所示。在主机初始化过程中,主机通过拉低单总线至少480us,以产生复位脉冲。接着,主机释放总线,并进入接收模式,总线释放后,5上拉电阻会将单总线拉高。在单总线器件检测到上升沿后,延时15-60us,接着从机拉低总线60-240us产生应答脉冲。

2.读/写时隙

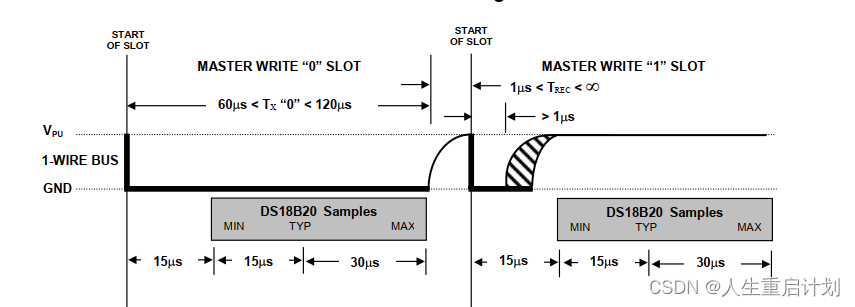

写时隙:写‘1’和‘0’。 主机采用写1时隙向从机写入1,而采用写0时隙向从机写入0。所有写时隙至少需要60us,且在两次独立的写时隙之间至少需要1us的恢复时间。两种写时隙均起始于主机拉低总线如下图所示。

产生写1时隙的方式:主机在拉低总线后,接着必须在15us内释放总线,由上拉电阻将总线拉至高电平。

写0时隙:主机拉低总线后,只需要在整个时隙期间保持低电平即可(至少60us)。

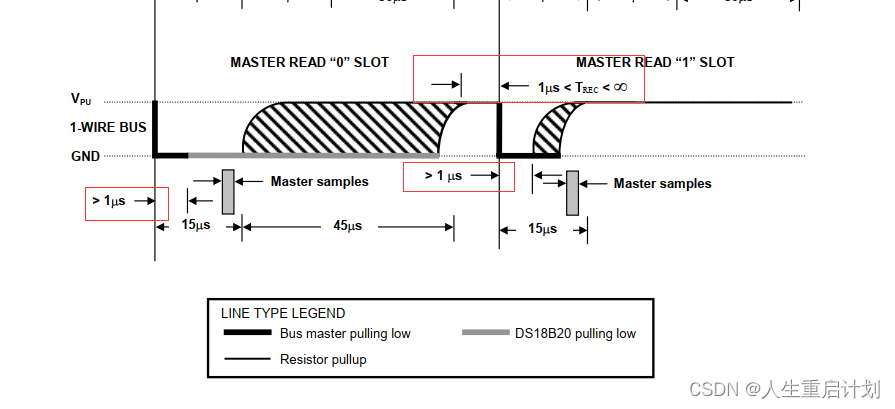

读时隙:单总线器件仅在主机发送读时隙时,才向主机传输数据,因此主机发出读数据命令后,必须马上产生读时隙,以便从机能够传输数据。所有读时隙至少需要60us,且在两次独立的读时隙之间至少需要1us的恢复时间。每个读时隙都由主机发起,至少拉低总线1us。如下图所示

若从机发送1,则保持总线为高电平;若发送0,则拉低总线。当发送0时,从机在该时隙结束后释放总线,由上拉电阻将总线拉回至空闲高电平状态。从机发出的数据在起始时隙之后,保持有效时间15us,因而,主机在读时隙期间必须释放总线,并且在时隙起始后的15us之内采样总线状态。

3.ROM指令。

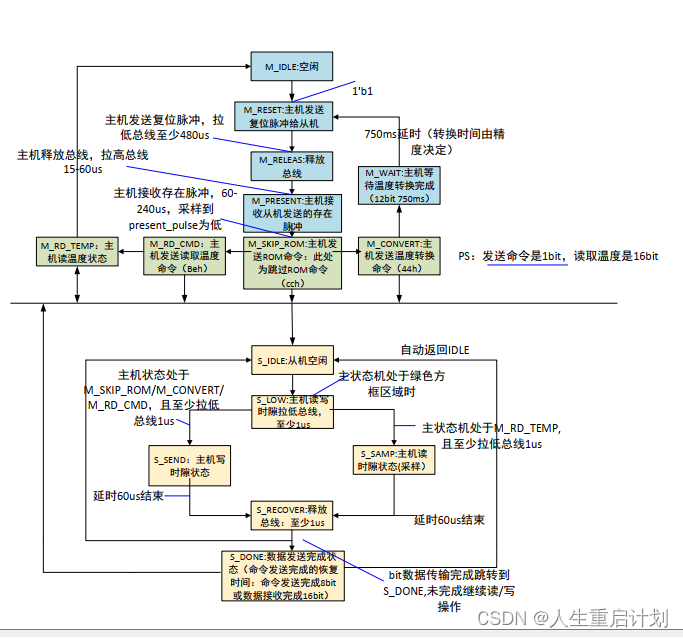

本次主要使用了跳过ROM命令(cch)、温度转换ROM命令(44h),和读取温度命令(beh)。详细的命令功能可查阅手册。

二、读取温度实现

1.状态划分

本次设计使用主从状态机描述系统工作流程。如下图

将整个流程弄清楚之后,后面实现基本也就水到渠成了。

总结

整个项目整体难度不大,主要就是手册的阅读,掌握整个流程的时序。这里单纯记录自己的学习过程,仅供参考。

3071

3071

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?