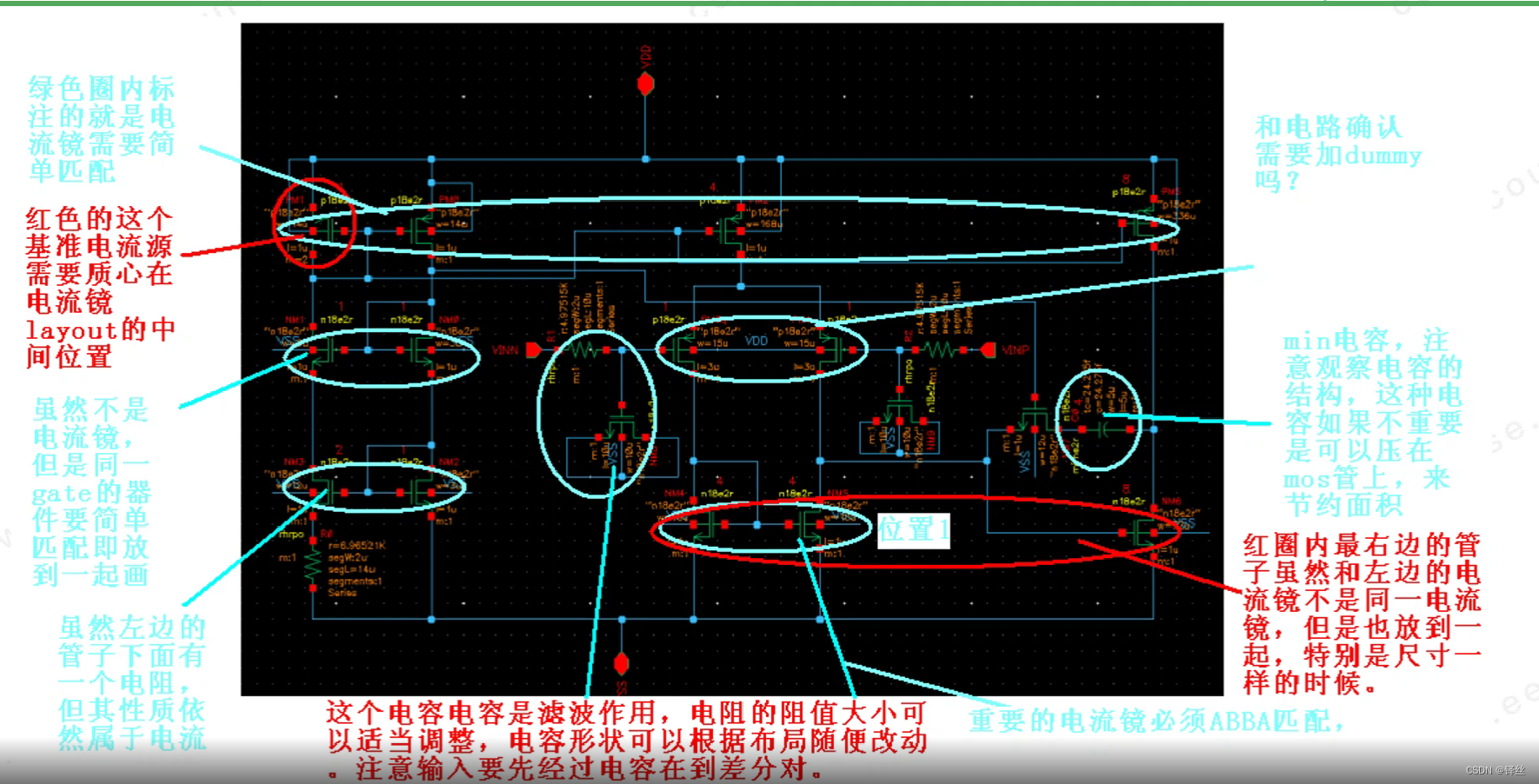

一、分析comp(op)的电路图

以layout的眼光分析电路,找到画版图时需特殊处理的地方,如匹配,大电流管子(﹥10uA),噪声隔离,敏感线保护等。

op的电路图分析结果:

1.需要匹配的电流镜:

差分上的电流镜很重要,如果是一个mos(不是指管子的个数)就不能放到两边

2.需要匹配的差分对:与电路讨论

3.可任意改变电容形状,但位置需要考虑

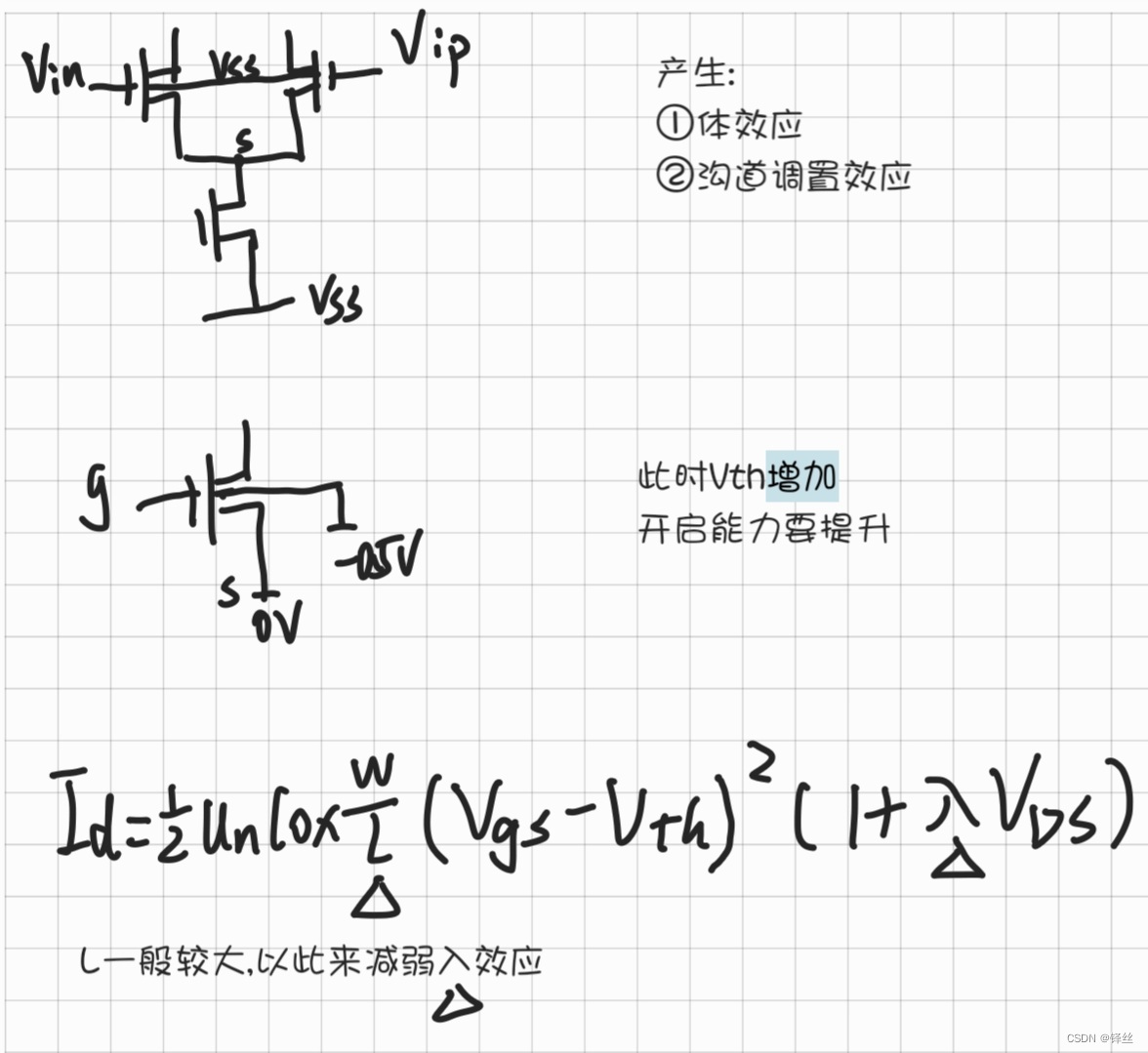

衬底和源不在一起时,阈值电压会增加

注意:①体效应②沟道调置效应

二、初始Floorplan和概念理解

概念和规律:

1.Floorplan即布局,用layout调出后,按电路的要求大致把器件摆在一起

2.其时间占整个cell layout时间一半左右,好的布局可减少走线线道,减少面积和布线时间,DRC、LVS的工作也会减少

3.规律性 先放重“要地方,按上到下布局,再从左往右。尽量pmos一排,nmos一排。能合并则合并。电源地线总线都为直线

实际layout操作:

1.用XL调出器件

2.按电路简单排版,

3.Align可快速把相同器件排列(一般不用)

4.可用XL的Reinitialize Floorplan功能简单集中(一般不用)

5.由上到下,按PMOS电流镜到差分对,到NMOS电流镜进行细化布局

三、优化Floorplan

1.先把固定单元画好,如差分对、三极管,可提高Floorplan的准确性,和提高后续修改,优化布局的操作性。

2.任何一个cell中都会存在一些只要关键数值(w,电阻值,电容值等)和电路对应上,个数、形状随意的器件。利用好电容,如差分对的滤波电容

3.细节处理,决定性能和面积的决定因素

图

PS:一般模拟模块外面打n环,里面打p环

好处:里面是安静模块,外面噪声进入时会被P环吸收走,

数字模块外面打p环,里面打n环

好处:里面是波动模块,P环就近吸收

四、连线

五、DRC LVS验证

六、优化layout

文章详细分析了电路图中的关键点,包括需要匹配的电流镜和差分对,以及电容的位置和形状设计。Floorplan的重要性被强调,良好的布局可以减少走线,提高效率,并影响DRC和LVS验证。文章还提到了模拟和数字模块的环形布局策略,用于噪声管理和优化。

文章详细分析了电路图中的关键点,包括需要匹配的电流镜和差分对,以及电容的位置和形状设计。Floorplan的重要性被强调,良好的布局可以减少走线,提高效率,并影响DRC和LVS验证。文章还提到了模拟和数字模块的环形布局策略,用于噪声管理和优化。

4157

4157

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?