引言

布局工具会在芯片上划出功能块、确定功能块之间的连接关系、确定 I/O 压焊块的位置、确定芯片大小,并反馈给设计者当下的布局在进行布线时的难易程度。比如一个大的数字芯片,可能会包含微处理器单元(MPU)、浮点单元(FPU)、RAM 块和 ROM 块等。对于 Floorplan 而言,人们更倾向于靠自己的经验去摆放这些 Macro,摆放它们时不仅要考虑面积、互联线长等传统问题,还需要考虑 Place 阶段 Macro 的摆放对于 Place 的影响,有时还要考虑供电和接地结构。总之一个好的布局会带来芯片性能的提升和面积的优化。

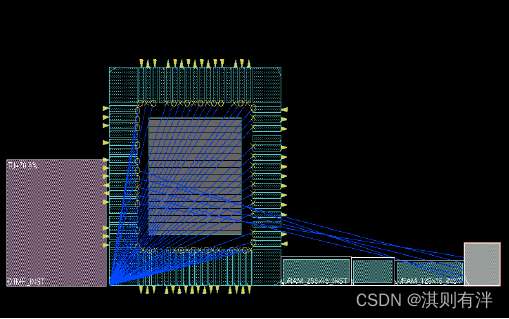

通常布局工具会显示从每一个模块连至 I/O 压焊块和其他模块的所有导线,称之为飞线(flightline)。飞线的连接情况是帮助我们布局的重要参考。

给定一个布局方案,可以衡量导线长度、数据流方向,也可以衡量 Macro、端口可访问性和相关时序(布局阶段延迟预估)。

初始化

在使用导入的网表和相应的库和工艺文件创建物理数据库后,第一步是确定 ASIC core 的宽度和高度。此外,还会创建标准单元行和 I/O 压焊块位置。

行的高度等于库中标准单元格的高度。如果库中有任何多个高度标准单元,它们将占用多行。

一般行是相互毗邻摆放的,如果布线拥塞也可以在行之间加入布线通道。

压焊块摆放

作为连接芯片内部信号与封装管脚的桥梁,I/O 单元的分配要综合考虑印制板走线、封装形式、供电情况以及内部模块结构,从而保证信号从芯片内部传递到外部时其路径最短,同时要求从 I/O 单元关键引线到封装点时,避免信号交叉,方便封装基板的制作,减少基板上的走线层数,从而降低封装的成本。当芯片为通用芯片时,需要参考现有的类似芯片的封装形式,从而方便产品的应用,如果芯片是专用于某个设计,则芯片的封装可以以印制板走线为基础,从而确定 I/O 单元的位置。

对于给定的 ASIC 设计,有三种类型的 I/O 焊盘:电源、接地和信号。细分为:数字输入单元、数字输出单元、数字双向输入输出单元

本文介绍了ASIC布局中的Floorplanning,包括初始化、压焊块摆放、电源规划和Macro摆放。良好的布局能优化芯片性能,降低布线难度。布局要考虑功能块的面积、互联线长、电源和接地结构,以及I/O单元的位置,以确保信号传输效率和成本效益。电源规划涉及全局电源定义和电源网格设计,以平衡电流分布,减少IR drop和电迁移问题。Macro的边缘摆放策略有助于优化空间利用和布线资源。

本文介绍了ASIC布局中的Floorplanning,包括初始化、压焊块摆放、电源规划和Macro摆放。良好的布局能优化芯片性能,降低布线难度。布局要考虑功能块的面积、互联线长、电源和接地结构,以及I/O单元的位置,以确保信号传输效率和成本效益。电源规划涉及全局电源定义和电源网格设计,以平衡电流分布,减少IR drop和电迁移问题。Macro的边缘摆放策略有助于优化空间利用和布线资源。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

608

608

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?