原文链接1:数字电路基础知识——锁存器与触发器的建立时间和保存时间(一)_摆渡沧桑的博客-CSDN博客_锁存器的建立时间和保持时间

原文链接2:数字电路基础知识——锁存器与触发器的建立时间和保存时间(二)_摆渡沧桑的博客-CSDN博客_数字电路tcq

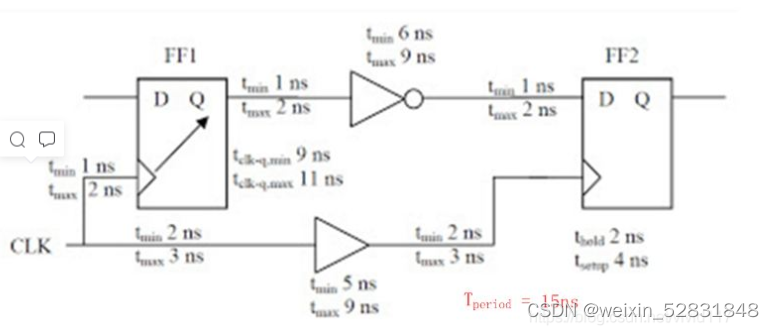

建立时间和保持时间的计算2——实际电路的Setup和Hold公式及violation(违反)分析

因为在不同的情形下,例如不同的温度,电压,loading等等,每一段电路的delay是不同的,所以对于同一段电路,其delay可以在如下范围中:

Min_delay<= Delay <= max_delay

一、原文

1. 建立时间

Tperiod - (Tc->q_FF1 + Tcomb_logic) + Tskew - Tsetup >= 0

Tskew = Tclk_delay_FF2 - Tclk_delay_FF1

即:

Tclk_delay_FF1 + Tc->q_FF1 + Tcomb_logic + Tsetup <= Tclk_delay_FF2 + Tperiod

应该满足:

MAX_data_path_delay + Tsetup <= MIN_clk_path_delay + Tperiod

才能保证电路是可靠的。所以在实际电路中:

Tdata_path_max + Tsetup <= Tclk_path_min + Tperiod

对应上图,该公式应该是:

2ns+ 11ns + 2ns + 9ns + 2ns + 4ns <= 2ns + 5ns + 2ns + Tperiod

所以: 30 <= 9 + 15.因为违反了该公式,所以该电路出现了setup violation。

2. 保持时间

Tc->q_FF1 + Tcomb_logic - Tskew - Thold >= 0

即:

Tclk_delay_FF1 + Tc->q_FF1 + Tcomb_logic –Thold>= Tclk_delay_FF2

应该满足:

MIN_data_path_delay – Thold >= MAX_clk_path_delay

才能保证电路是可靠的。所以在实际电路中:

Tdata_path_min - Thold >= Tclk_path_max

对应上图,该公式应该是:

1ns +9ns + 1ns + 6ns + 1ns – 2ns >= 3ns + 9ns + 3ns

所以: 16ns >= 15ns,满足公司要求,所以该电路无holdviolation。

在某些电路中,可以认为clk tree上面没有延迟,可以认为wire没有延迟,那么setup和hold公式就得到简化。

二、自己的理解

1. 建立时间

Tc->q_FF1 + Tcomb_logic - Tskew - Thold >= 0

Tperiod - (Tc->q_FF1 + Tcomb_logic) + Tskew - Tsetup >= 0

根据极限考虑

其中,寄存器输出延时和组合逻辑输出延时要取MAX

即(Tc->q_FF1 + Tcomb_logic)MAX=(11+2+9+2)=24ns

其中,Tskew = Tclk_delay_FF2 - Tclk_delay_FF1要去MIN

即:Tskew_MIN=2+5+2-2=7ns

对应上图,该公式应该是:

15 -24 + 7 - 4 >=0 即 -6 >= 0

因为违反了该公式,所以该电路出现了setup violation。

2. 保持时间

Tc->q_FF1 + Tcomb_logic - Tskew - Thold >= 0

根据极限考虑

其中,寄存器输出延时和组合逻辑输出延时要取MIN

即(Tc->q_FF1 + Tcomb_logic)MAX=(9+1+6+1)=17ns

其中,Tskew = Tclk_delay_FF2 - Tclk_delay_FF1要去MAX

即:Tskew_MIN=3+9+3-1=14ns

对应上图,该公式应该是:

17 - 14 -2 >= 0 即:1 >= 0

所以满足要求,所以该电路无holdviolation。

在某些电路中,可以认为clk tree上面没有延迟,可以认为wire没有延迟,那么setup和hold公式就得到简化。

————————————————

版权声明:本文为CSDN博主「摆渡沧桑」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/vivid117/article/details/101868356

665

665

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?