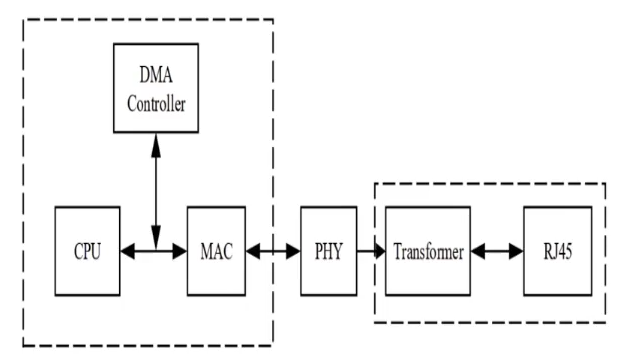

从硬件的角度来说,以太网接口电路主要由MAC(Media AccessControl:媒体访问控制)控制器和物理层接口PHY(Physical Layer,PHY)两大分构成。MAC指媒体访问控制子层协议,它和PHY接口既可以整合到单颗芯片内,也可以独立分开,MAC控制器由FPGA实现,PHY芯片指开发板板载的以太网芯片。

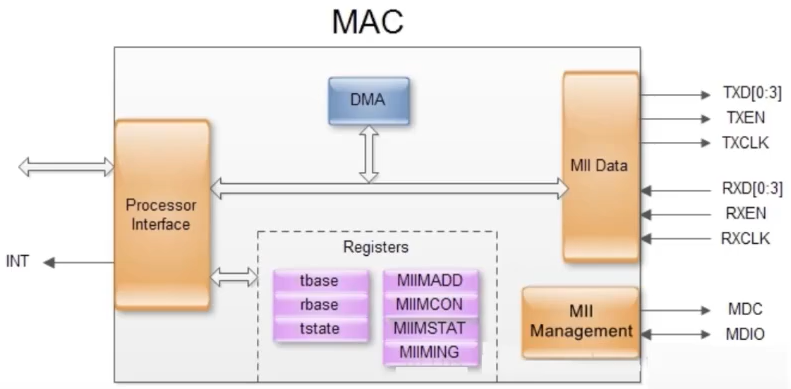

一、MAC控制器

MAC是Media Access Control的缩写,即媒体访问控制子层协议。该协议位于OSI七层协议中数据链路层的下半部分,主要负责控制与连接物理层的物理介质。在发送数据的时候,MAC协议可以事先判断是否可以发送数据,如果可以发送将给数据加上一些控制信息,最终将数据以及控制信息以规定的格式发送到物理层;在接收数据的时候,MAC协议首先判断输入的信息是否发生传输错误,如果没有错误,则去掉控制信息发送至LLC层。

MAC(Media AccessControl)媒体访问控制子层协议,MAC可以是一个硬件控制器,MAC通信以协议,该协议位于OSI七层协议中数据链路层。

二、PHY物理层接口

PHY芯片在发送数据时,首先将MAC发过来的并行据(FPGA发送出来的数据)转化为串行流数据,按照物理层的编码规侧测把数据编码转换为模拟信号(网钱上传输的差分信号)通过网口发送出去,接收数据的流程反之。PHY是物理接口收发器,它实现物理层。包括MII/GMII(介质独立接口)子层、PCS(物理编码子层)、PMA(物理介质附加)子层、PMD(物理介质相关)子层、MDI子层。

1、PHY物理层接口

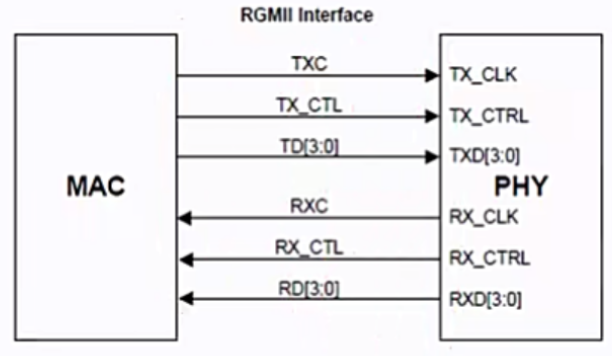

以太网的通信离不开物理层PHY芯片的支持,以太网MAC和PHY之间有一个接口,常用的接口有MII、RMII、GMII、RGMII等。在千兆以太网中,常用的接口为RGMII和GMII接口。

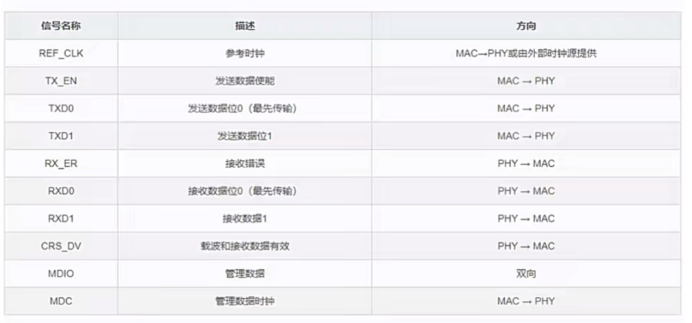

(1)MII(Medium Independent Interface,媒体独立接口)

MII支持10Mbps和100Mbps的操作,数据位宽为4位,在100Mbps传输速率下,时钟频率为25hz。“媒体浊立”表明在不对MAC硬件重新设计或替换的情况下,任何类型的PHY设备者都可以正常工作。MII接口一共有16根线。

(2)RMII(Reduced MII)

RMII是MII的简化板,数据位宽为2位,在100Mbps传输速率下,时钟频率为50MHz。RGMII接口的优势是同时适用于10M/100M/1000M6ps通信速率,同时占用的引脚数较少。但RGMII接口也有其缺点,就是在PCB布时需要尽可能对时钟、控制和喽数据线进行等长处理,且时序约束相对也更为严格。

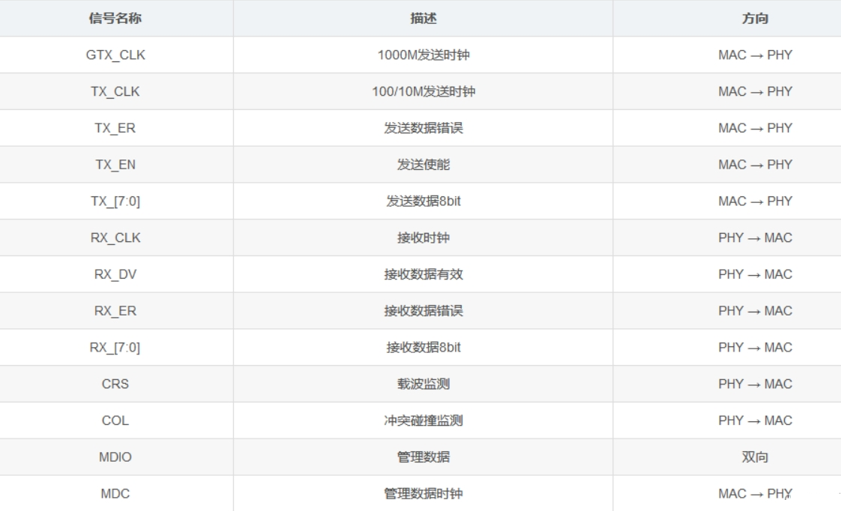

(3)GMII(Gigabit MII)

GMII接口向下兼容MII接口,支持10Mbps、100Mbps和1000Mbps的操作,数据位宽为8位,在1000Mbps传输速率下,时钟频率为125Hz。

(4)RGMII(Reduced GMII)

RGMII是GMII的简化版,数据位宽为4位,在1000Mbps传输速率下,时钟频率为125MHz,在时钟的上下沿同时采样数据。在100Mbps和10Mbps通信速率下,为单个时钟沿采样。

2、常用PHY芯片选择

| 公司 | 名称 | 速率 | MAC接口类型 | 封装大小 | 叠层类型 |

| Broadcom | BCM89610 | 10/100/1000Mbps | MII/RGMII | 10Base-T/100Base-TX/1000Base-T | |

| Marvell | 88Q1010 | 10/100/1000Mbps | MII/RGMII/RMII | QFN-60pin-6*6mm | 100Base-T1 |

| Marvell | 88E1512 | 10/100/1000Mbps | RGMII/SGMII | QFN-56pin- | 10Base-T/100Base-TX-1000Base-T/SFP/100Base-FX/1000Base-X |

| Marvell | 88Q211X | 10/100/1000Mbps | RGMII/SGMII | QFN-40pin- | 100Base-T1/1000Base-T1 |

| Atheros | AR8031 | 10/100/1000Mbps | RGMII/SGMII | QFN-48pin-6*6mm | 10Base-Te/100Base-TX/1000Base-T |

| NFP | TJA1001 | 100Mbps | RMII | HVQFN-32pin-6*6mm | 100Base-T1 |

| Microchip | KSZ8061 | 10/100Mbps | MII | LQFP-48pin-7*7mm | 10Base-T/100Base-TX |

| Microchip | KSZ9031 | 10/100/1000Mbps | GMII/MII | QFP-64pin-8*8mm | 10Base-T/100Base-TX/1000Base-T |

| TI | DP83848QSQ | 10/100Mbps | MII/RMII | WQFN-40pin-6*6mm | 10Base-T/100Base-TX/100 |

| Realtek | RTL8201 | 10/100Mbps | MII/7-wire SNI | LQFP-48pin | 10Base-T/100Base-TX/100Base-FX/100 |

三、网络变压器

- 滤除共模干扰,增强信号,传输更远;

- 隔离PHY端和RJ45端直流;外部干扰;

- 设备间为不同电平时,耦合交流信号,电平与PHY端一致,可保护PHY芯片;

四、RJ45以太网接口

1、信号灯

网口一般有两个信号灯,一个代表连接状态指示灯,另一个代表信号传输指示灯。

网口工作正常情况下的指示灯情况:

1、连接状态指示灯呈绿色并且长亮,不亮表示未连接成功。

2、信号指示灯呈黄色,并且会不停的闪烁。不亮或者不闪烁表示无信号传输。

以太网的分类有标准以太网(10Mbit/s),快速以太网(100Mbit/s)和千兆以太网(1000Mbit/s)。随着以太网技术的飞速发展,市场上也出现了万兆以太网(10Gbit/s)。部分以太网接口封装集成变压器,电路设计时不需要额外添加。

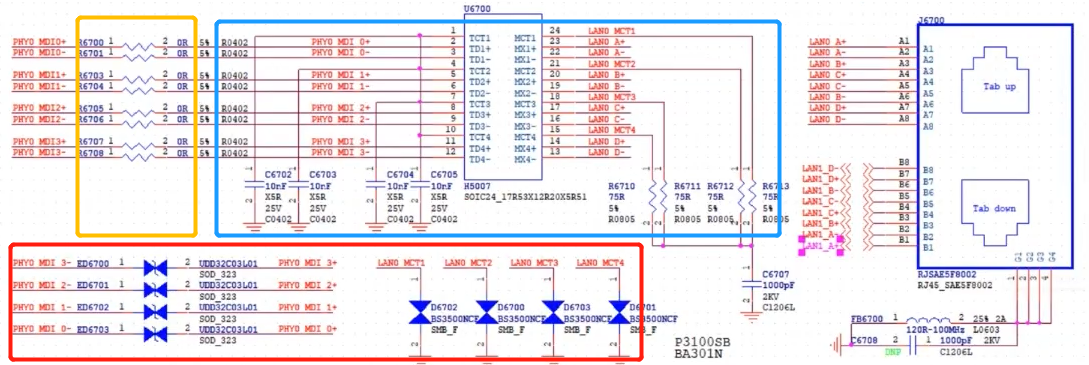

2、RJ45保护电路

ESD器件(红框):尖峰放电,保护后级电路,当网线很长时,长期耦合会有串扰信号,网线寄生电容很大,感性电路电压很高,需要ESD器件保护

变压器(蓝框):阻抗变换作用,部分电路变压器集成到RJ45接口内,网线接口电压等级幅度与后级电路不同;若没有变压器当打雷产生的雷击信号会直接传输到电路板上,从而损坏芯片

串联反射电阻(黄框):调节信号强度,调节信号反射(信号反射强烈,可加大电阻值;信号微弱,可减小电阻值)

四、PCB布局要求

1、常规走线要求

| 参数 | 要求 |

| 走线阻抗 | 单端50Ω±10% |

| (TXD{0-3},TXEN) to TXCLK等长 | <120mil |

| (RXD{0-3},RXEN) to RXCLK等长 | <120mil |

| 走线长度 | <5inchs |

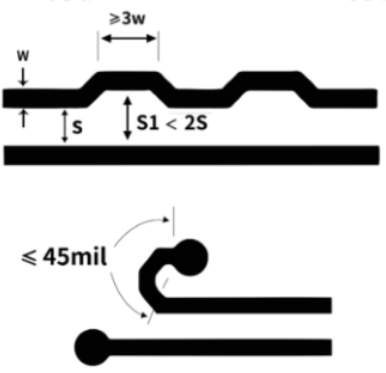

| 数据传输线增加间距 | 建议大于2倍数据传输线宽 |

| 数据传输线与其他信号线间距 | 建议大于3倍数据传输线宽 |

2、CLK需要全程包地处理,并在地线上打上地过孔,每150mil必须有一个过孔;且时钟的去耦电容必须靠近管脚放置。

3、RJ45和变压器之间的距离尽可能的短,器件布局的原则是通常按照信号流向放置,切不可绕来绕去;以太网转换芯片和变压器之间的距离应尽可能短,一般不超过5inch。

4、复位电路信号应当尽可能的靠近以太网转换芯片,并且若可能的话应当远离TX、RX和时钟信号

5、时钟电路应当尽可能的靠近以太网转换芯片,远离电路板边缘、其他高频信号、I/O端口、走线或磁性元件周围。

6、网口的差分尽量走表底层,差分对之间的间距至少4W以上,由于管脚分布、过孔、以及走线空间等因素存在,使得差分线长度不匹配,时序会发生偏移,还会引入共模干扰,降低信号质量,因此差分对内的等长约束为5mil,差分对之间不用进行等长,等长时注意符合差分等长规则。

7、RJ45接口区域内部所有层挖空处理。RJ45接口的G1,G2,G3和G4管脚的走线至少需要加粗至1mm以上,跨接电感和电容靠近接口放置,旁边多打地过孔。

8、变压器所有层挖空(只挖一半,另一半铺铜处理,均匀的打上地过孔,建议间隔50mil一个),变压器到接口部分不用控阻抗,走线加粗处理;变压器到PHY芯片差分走线,控制100Ω差分阻抗。

9、以太网芯片到CPU的RGMII接口线的发送部分和接收部分要分开布线,不要将接收和发送网络混合布线,线与线之间需要满足3W,发送和接收总线分别进行等长,等长范围100mil,

10、RJ45和变压器之间的距离尽可能的短;

11、芯片每个电源管脚放置一个0.luf小电容,每个电压应该最少有一个4.7uf的大电容

12、电源信号的走线应该短而宽。退耦电容上的过孔直径最好稍大一点。

13、变压器的两边最好是割地:如果不能,需要在变压器肚子的正下方所有层挖空,不能有任何走线。分割处理,就是为了达到初、次级的隔离;

14、接口接地隔离,我们用磁珠或者电容后,再接地。

15、差分对(Rx±、Tx±) 一般对内做5mil等长。四对差分线,组间为20mil。阻抗为100Ω。

16、RGMII接口线的TXD和RXD同组同层。TX要与RX之间的距离最好在4W以上,最好是不在同

一层走线。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?