FPGA开发第二弹:流水灯实验

流水灯的原理是开发板上的四盏灯交替亮起,按顺序循环往复产生流水的现象。

LED灯硬件原理图如下所示:

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存失败,源站可能有防盗链机制,建议将图片保存下来直接上传下上传(i94S7GpVYvqZ-1659582399078)(C:\Users\user\AppData\Roaming\Typora\typora-user-images\image-20220803144605337.png)(C:\Users\user\AppData\Roaming\Typora\typora-user-images\image-20220803144605337.png)]](https://img-blog.csdnimg.cn/8e7acc9f7a3747e6856a5cdc7e61c8a5.png)

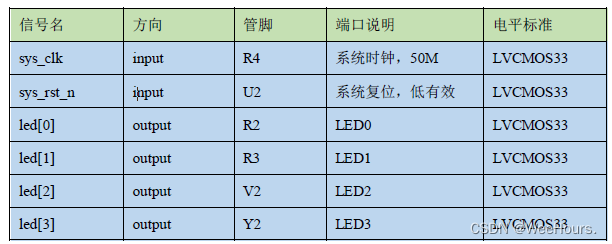

实验中的系统时钟、按键复位以及LED端口的管脚分配如下表所示。

对应的XDC约束语句如下所示:

create_clock -name clk -period 20 [get_ports clk]

set_property -dict {PACKAGE_PIN R4 IOSTANDARD LVCMOS33} [get_ports clk]

set_property -dict {PACKAGE_PIN U2 IOSTANDARD LVCMOS33} [get_ports rst]

set_property -dict {PACKAGE_PIN R2 IOSTANDARD LVCMOS33} [get_ports led[0]]

set_property -dict {PACKAGE_PIN R3 IOSTANDARD LVCMOS33} [get_ports led[1]]

set_property -dict {PACKAGE_PIN V2 IOSTANDARD LVCMOS33} [get_ports led[2]]

set_property -dict {PACKAGE_PIN Y2 IOSTANDARD LVCMOS33} [get_ports led[3]]

流水灯模块原理图如下图所示:

由于人眼的视觉暂留,流水灯状态变化间隔时间不能低于0.1s,否则的话实验效果就不明显。本实验我们设置流水灯间隔为0.2s一次,我们使用计数器累加计数来计时,计时达0.2s后计数器清零并重新开始计数,每0.2s就能让led的状态改变一次。

流水灯模块代码如下:

module flow_led(

input clk,

input rst,

output reg [3:0] led

);//定义输入端口时钟和清零,输出端口即LED

reg[23:0] counter;//定义一个计数器

always @(posedge clk or negedge rst)

begin

if(rst==0)

count<=24'd0;//根据计数的值进行规定位数

else if(counter<24'd1000_0000)//最多记到0.2s,这个是次数一个时钟周期设置为20ns

counter<=counter+1'b1;

else

counter<=24'd0;

end

always@(posedge clk or negedge rst)

begin

if(rst==0)//清零信号

led<=4'b0001;

else if(counter==24'd1000_0000)

led[3:0]<={led[2:0],led[3]};//0.2s变一次

else

led<=led;//其他时间保持不变

end

endmodule

测试代码testbench如下:

`timescale 1ns/1ns

module test();

parameter T=20;//一个时间周期

reg clk;

reg rst;

wire [3:0] led;

initial

begin

clk=1'b0;

rst=1'b0;

#(T+1) rst=1'b1;

end

always #(T/2) clk=~clk;//半个时间周期翻转

flow_led lh(

.clk(clk),

.rst(rst),

.led(led)

);

endmodule

仿真结果如下图所示:

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-8ZdfpUAw-1659582399083)(C:\Users\user\AppData\Roaming\Typora\typora-user-images\image-20220803145937047.png)]](https://img-blog.csdnimg.cn/822823335856424b8c4c4608b9c0c2c6.png)

最后下载验证,生成比特流,在FPGA开发板上进行开发。

具体操作可以参考FPGA开发第一弹:FPGA开发第一弹:Vivado软件安装、开发使用与工程建立_WeeHours.的博客-CSDN博客_vivado 设置顶层

以上就是我进行的流水灯实验,继续熟悉整个FPGA开发的流程,如果自己做的项目的话其实每一步基本都不能缺失,每一步都需要我们认真总结掌握,多练几次也就熟练了!欢迎大家私信我一同交流学习,也欢迎大家批评指正!

543

543

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?