从Verilog源代码到GDS 掩模输出,运行一个基于 GUI 的完整综合示例。

名词解释:GDS(Graphic Data System)是一种电子设计自动化(EDA)工具中的文件格式,主要用于存储和交换集成电路(IC)的物理设计数据。GDS 文件通常包含布局、层次结构和几何信息,以描述集成电路的版图和结构。--fromGPT

来源:

我的背景:

Ubuntu22.04 VMware

qflow 1.4.102

正文开始:

Verilog源文件下载

使用的Verilog源文件代码:http://opencircuitdesign.com/qflow/example/map9v3.v

map9v3.v :旧的芯片配置逻辑块,简单且无用,作为示例正正好。

能被前端仿真平台理解的Verilog代码是不包含时序信息的(这一点要与testbench 风格区别开来)

安装

1.下载qflow

2.创建一个工作目录

3.把前面那个示例map9v3.v 放到这个目录下,可以记录一下这个源文件地址

此处,我的目录是:

~/IC/EDA/QFLOW/qflowtestgui/source

运行

1.cd到前面创建的那个目录

2.运行:

qflow gui或者

qflow -T technology verilog_file

%比如

qflow -T osu035 ~/Downloads/map9v3.v这俩用哪个都行,反正GUI都能控制(后面有展示)

GUI窗口

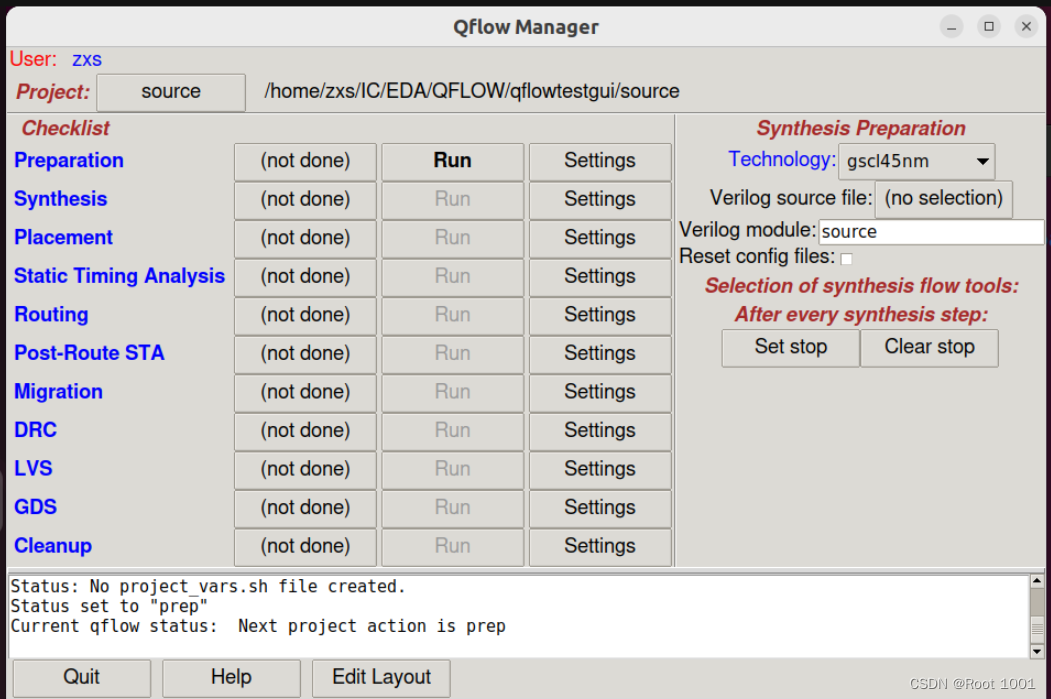

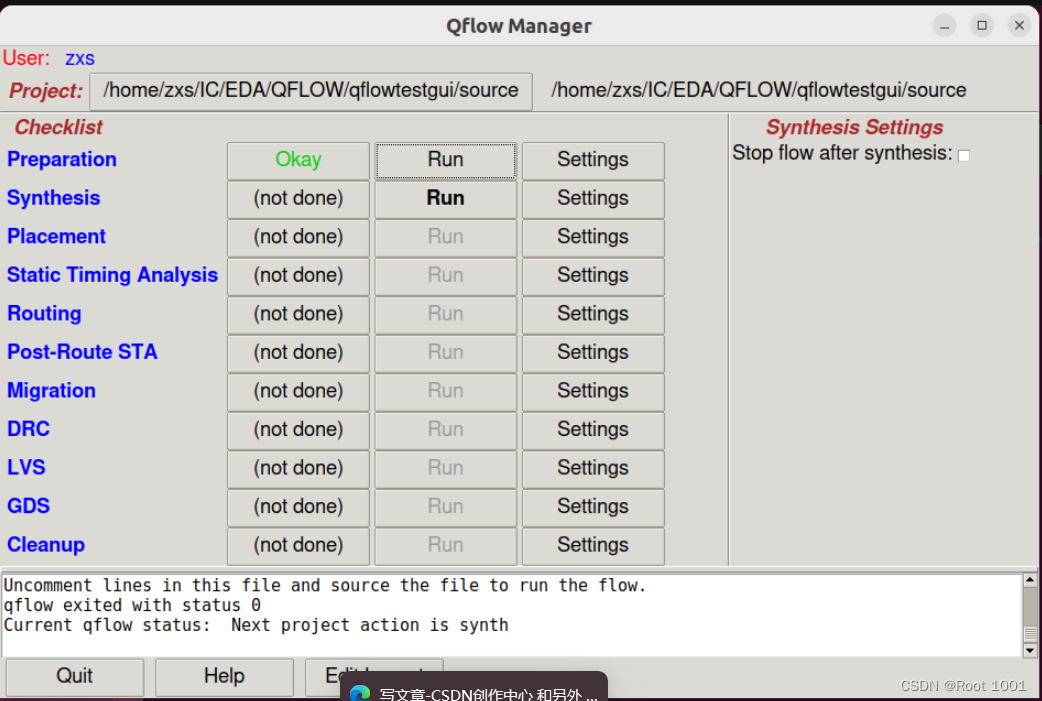

运行完上述代码,会出现这样一个gui窗口(未初始化):

图片解释:

"Project" :项目文件保存的地方;显示项目名字,不是顶层模块的名字;右边显示完整路径

"Checklist" :步骤罗列;

右边第一列显示状态:"(not done)" to "Okay" to "Fail",如果失败了可以点击然后显示log里面的解释;

中间列用于控制运行:"Run" 开始运行, "Stop"停止运行;灰色的点不了,得前面运行过了才能点。再次点击Run可以重复运行已经运行过的步骤。

Settings :查看任何步骤的设置情况。但是只能控制对应行的对应步骤的设置情况。任意设置随时可以调整,如果重新调整,需要重新run这个步骤才能生效。

综合的准备

"Synthesis Preparation":设置源文件输入,与使用的工艺。

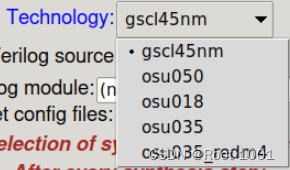

工艺technology:(“osu050”没有足够的金属层自动布置电源总线,“gscl45nm”没有运行完整教程所需的所有文件,第一次尝试完整流程建议选别的)

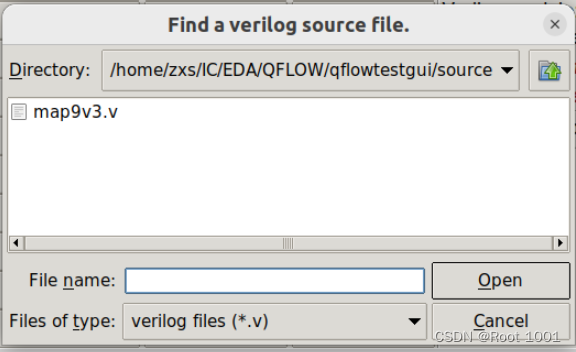

源文件Verilog source file:点击后显示这个,选文件,点open

运行各个步骤

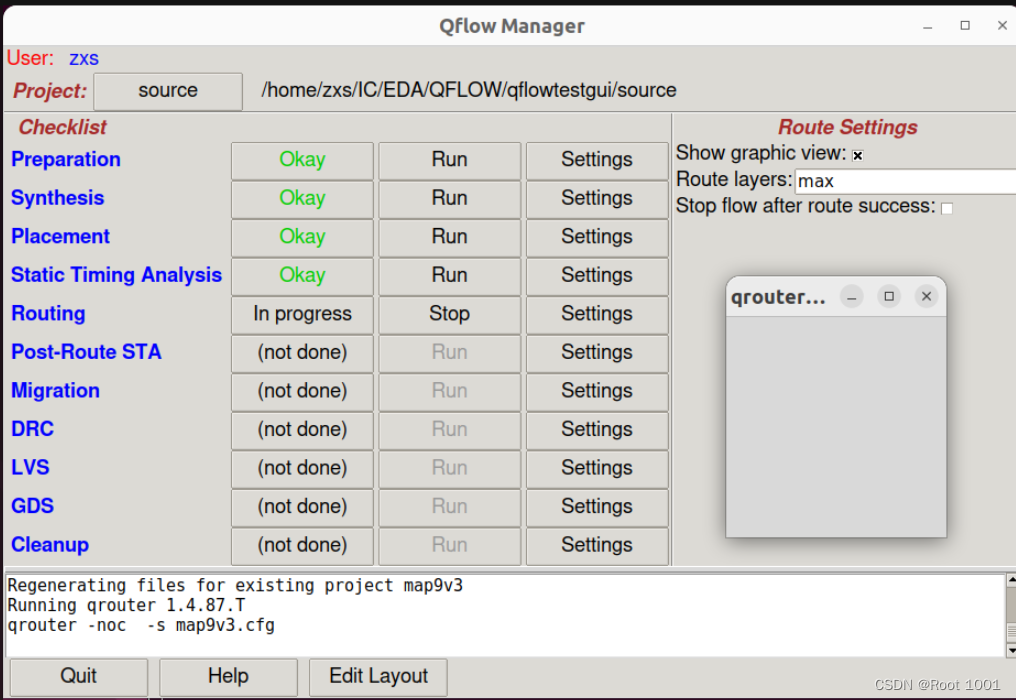

设置完前面的东西,开始Run:

点击Run,结果如下

继续Run

我在这一步卡住了

点开详细信息看了一下

果然逃避解决不了问题,我上次那个方法有后患。

难受,我继续搞这个问题去,解决了继续更新。。。

不过如果你没有我这个问题,应该是能正确输出结果的:

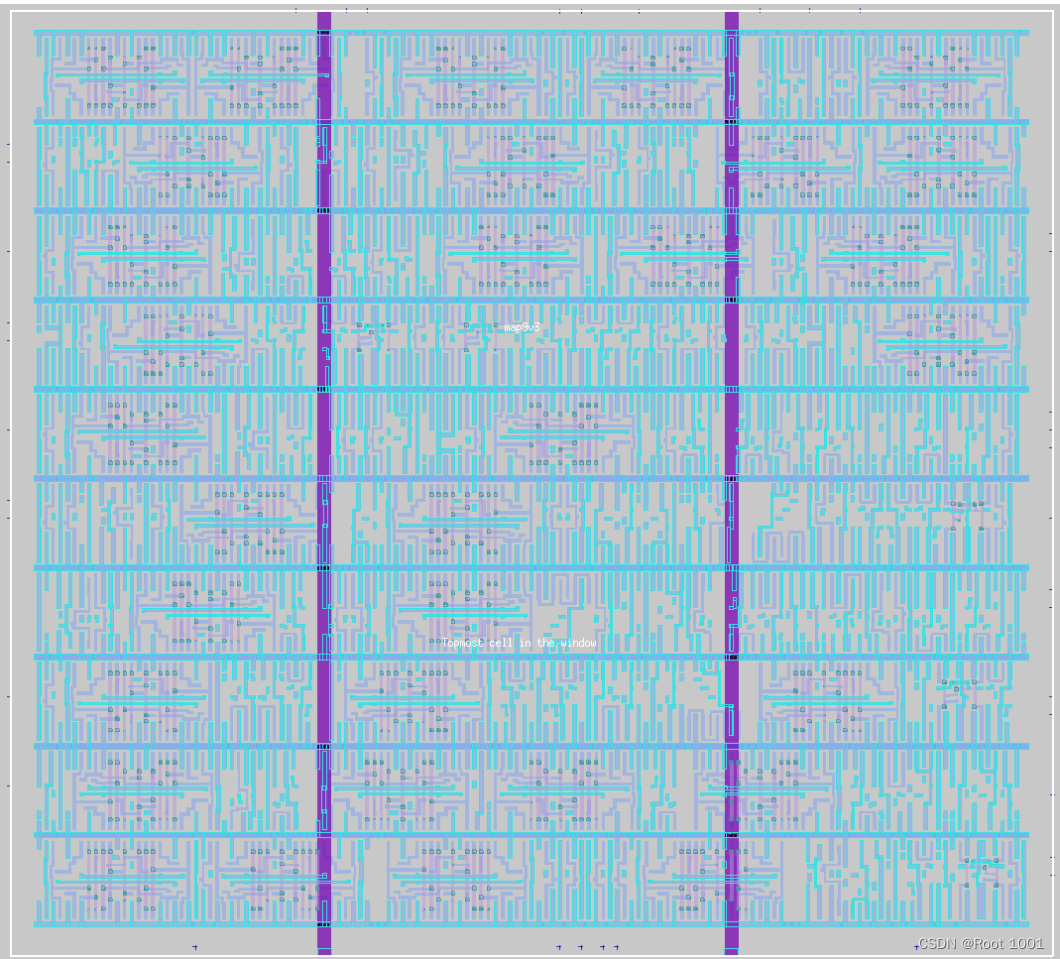

Placement运行完以后,点击Edit Layout就可以打开Magic 版图编辑器。最后一步完成后,可以显示LEF视图。不过Routing之前,不会布线。

可能的失败原因

大量组合逻辑导致引脚群密度过大,导致布线特别密集,导致布线失败。解决方法是在"Placement Settings"下,减少设计密度,在不同密度下多尝试运行几次,选择能成功运行的最高密度就行。

布线层数不足,选择三四层去布线基本都会失败。

引脚过度约束,比如引脚全部缩在一坨,

| email: |

|

Last updated: February 20, 2019 at 8:44pm

1654

1654

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?