常见的引脚分布规律

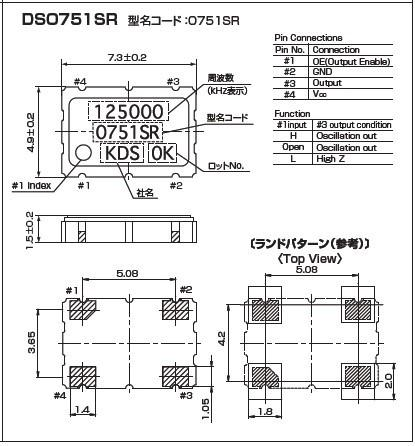

有标记的引脚作为起始引脚:许多有源晶振会在其中一个引脚上或者靠近该引脚的外壳位置做一个明显标记,比如打点、印一个小圆圈、有一个缺口等。这个有标记的引脚一般被定义为1脚。然后将有源晶振的引脚朝下,以正视的角度,按照逆时针方向依次为2脚、3脚和4脚。

基于封装外形的引脚识别:

正方的DIP-8封装:打点的是1脚,各引脚功能通常为:1脚一般为NC(空脚,不连接任何功能,在某些设计中也可能有特殊用途,但常规应用中悬空);4脚为GND(接地引脚,用于为晶振内部电路提供参考地电位,确保电路工作稳定,减少噪声干扰);5脚为Output(输出引脚,输出稳定的时钟信号,供其他电路使用);8脚为VCC(电源引脚,为晶振内部的振荡电路等提供工作电压,常见的工作电压有3.3V、5V等,不同型号的有源晶振工作电压有所不同)。

长方的DIP-14封装:同样打点的是1脚,其引脚功能一般为:1脚为NC(空脚);7脚为GND(接地);8脚为Output(输出时钟信号);14脚为VCC(电源输入)。

通用的引脚功能定义

电源引脚(VCC):此引脚接入直流电源,为有源晶振内部的晶体、晶体管以及阻容元件等构成的振荡电路提供电能,使其能够持续稳定地产生振荡信号。电源电压值需严格符合该型号有源晶振的规格要求,如TTL型的有源晶振一般使用5V电源,而HC型的则可支持3.3V或5V电源。如果接入的电源电压过高,可能会损坏晶振内部电路;电压过低,则晶振可能无法正常起振工作。

接地引脚(GND):接地引脚是整个电路的参考电位点,将晶振内部电路的低电位端与系统地相连,能够稳定电路工作,减少信号干扰。在电路中,良好的接地设计对于晶振输出稳定的时钟信号至关重要,若接地不良,可能会引入噪声,导致晶振输出的时钟信号出现抖动,影响使用该时钟信号的其他电路的正常工作。

信号输出引脚(OUT):这是有源晶振的关键引脚,经过内部振荡电路产生并处理后的稳定时钟信号从该引脚输出,以供其他电子元件或电路模块使用,比如为微控制器、数字信号处理器(DSP)等提供精确的时钟基准,确保它们能够按照既定的时序进行数据处理、指令执行等操作。输出信号的频率由晶振内部的石英晶体特性以及振荡电路决定,其频率精度和稳定性直接影响到整个系统的性能。

空脚(NC):空脚在多数常见应用中不连接任何电路,处于悬空状态。它的存在可能是出于晶振生产工艺、电气性能优化或者为未来可能的功能扩展预留的。不过在某些特殊的电路设计中,空脚也可能被赋予特定的功能,但这种情况相对较少。在一般的使用中,无需对空脚进行额外处理,但要注意避免其意外接触到其他带电引脚或受到外界干扰。

实际应用中,在使用有源晶振前,一定要仔细查阅该型号晶振的datasheet(数据手册),因为不同厂家生产的有源晶振,即使是相同的封装形式,其引脚定义和功能也可能存在差异。只有严格按照数据手册的说明进行引脚连接和电路设计,才能确保有源晶振正常工作,为整个电子系统提供稳定可靠的时钟信号。

2450

2450

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?