IR drop作为目前芯片设计中必不可少的检查,可以早期规避使用过程中发热,性能下降,甚至是功能失效的风险。

发热很好理解,局部功耗或者瞬态电流过大,自然会引起发热。这种情况通过物理降温的方式就可以弥补,比如加风扇,液冷等等..

引起功能失效和性能下降的原因多种多样,但是跟PA紧密相关的就是时序,时序与源漏电流大小相关,栅极电压减小到一定程度会使得器件delay增大,无法满足时序要求,从而引发电路异常。低性能,传统工艺设计风险相对较小;先进工艺,尤其是高性能芯片设计发生上述行为的风险日益剧增。如何规避呢?早先采用整体时序加严的方法确实有效,比如uncertainty,ocv等,但是全局的时序过约会导致功耗及面积的剧增,对于大规模的设计性价比过低,从而就衍生出关键路径反标仿真的方式。

具体的做法如何呢?PA动态drop仿真结果,在STA流程中进行一一反标,结合不同的电压库的delay进行插值,将drop的影响直接体现到时序,对于关键路径采用时序优化来抵消drop可能带来的时序风险。另外一种情况,项目后期dynamic drop的收敛遇到瓶颈,也可以采用上述的方式去鉴别风险从而采取合理的措施。

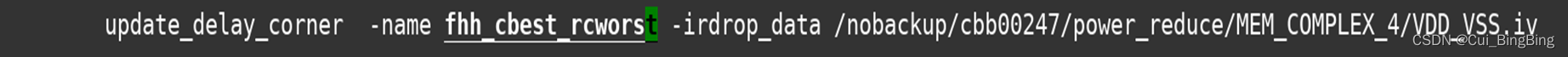

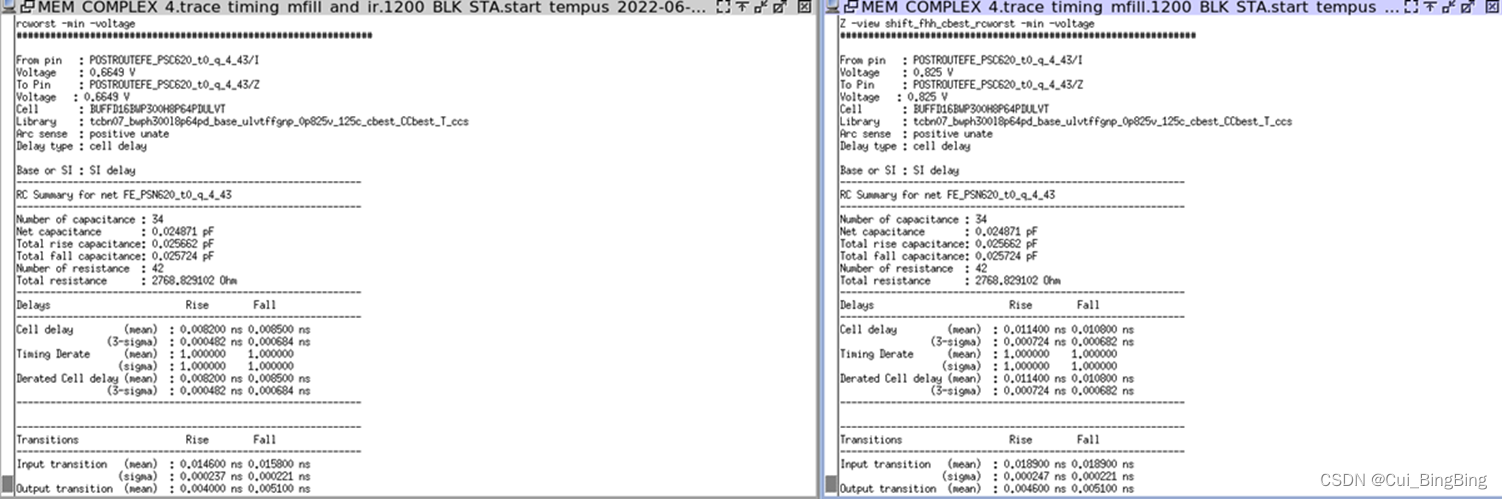

图:1-0

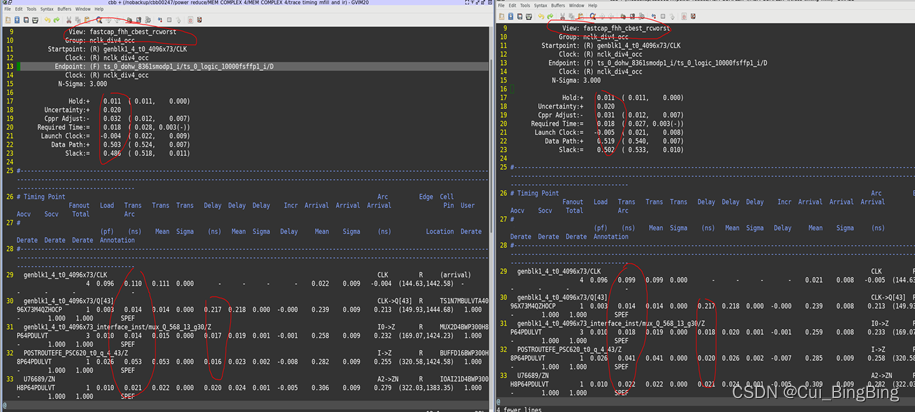

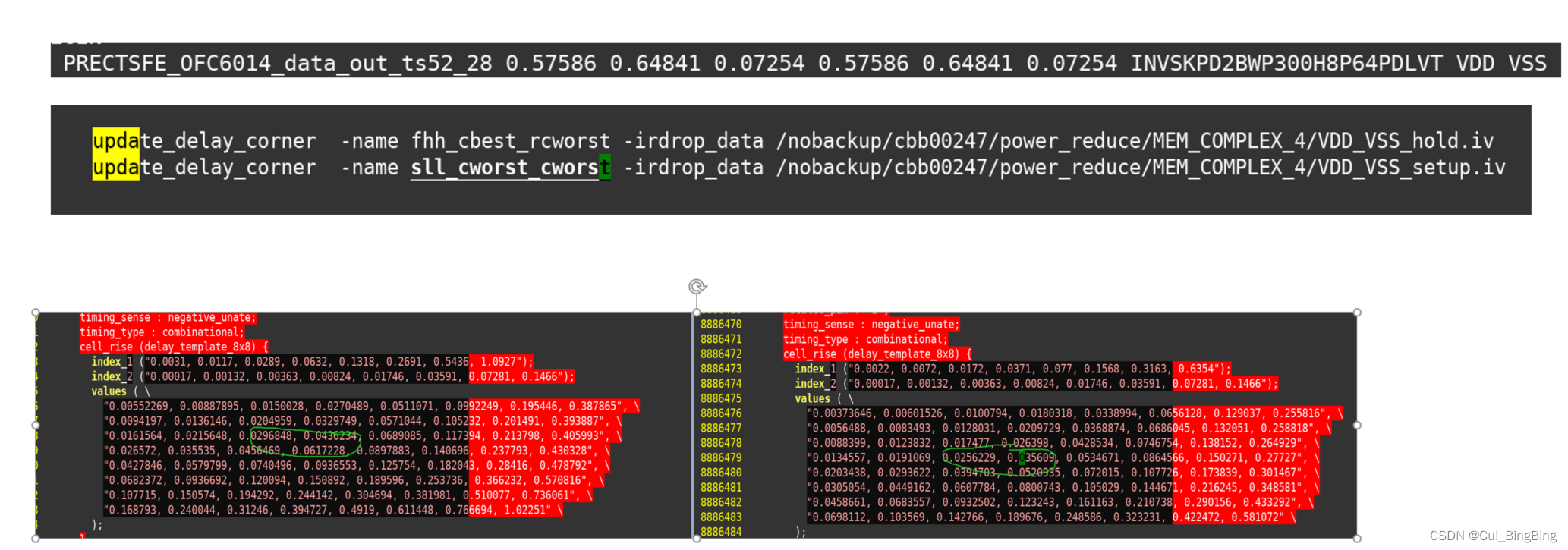

图:1-1

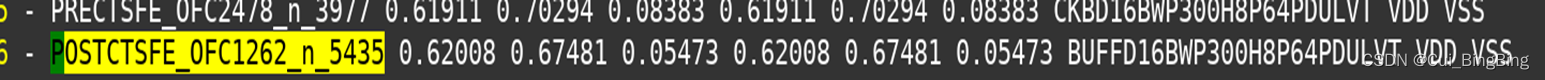

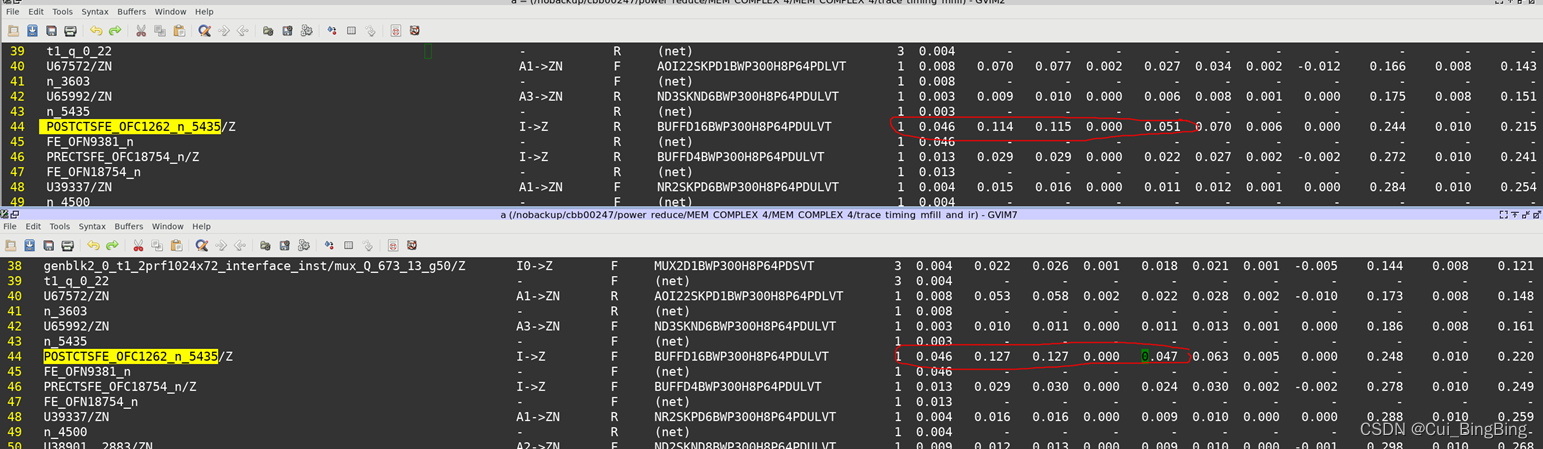

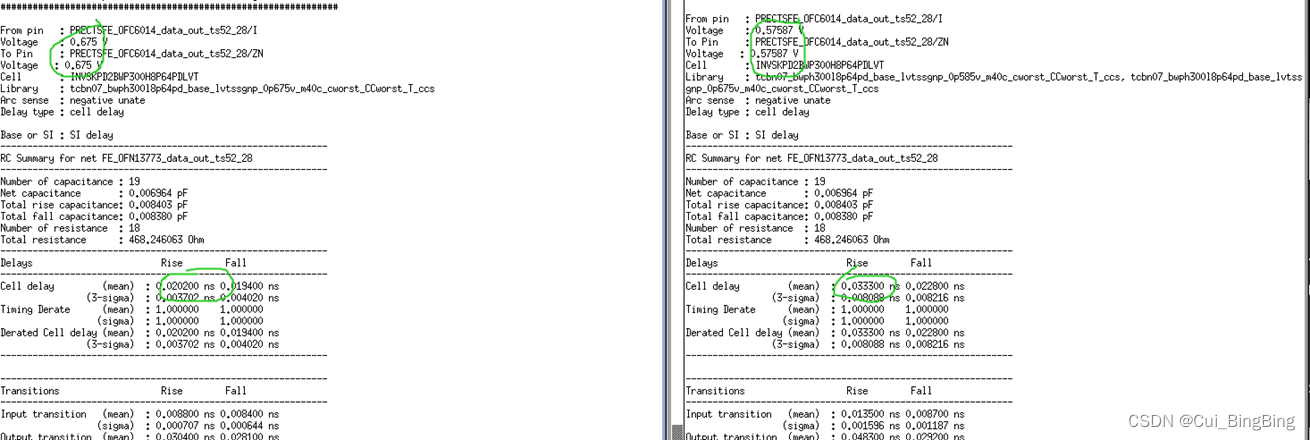

图:1-2

图1-0:将PA结果更新到STA流程

图1-1:合入动态drop前后结果对比

图1-2:合入动态drop后delay计算前后对比

针对不同的corner可以将不同的corner进行PA仿真,然后合入到对应的STA的流程观察具体的时序。将关键路径按照合入PA之后的时序结果进行优化,可以有效的预防使用过程电压过低带来的时序影响,尤其是对于不好处理的动态drop情况,可以通过时序的判断合理的放松收敛的策略。

5424

5424

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?