目录

一、数据手册下载

已经下载了数据手册的同学可以直接看第二节,读写时序都应按照芯片数据手册执行,数据手册免费下载方法:

1、电脑端

①推荐立创商城,可以免费下载数据手册,且芯片型号众多。

S29GL01GS11DHIV10_S29GL01GS11DHIV10采购信息-立创电子元器件商城 (szlcsc.com)

②半导小芯-芯片查询工具_芯片替代查询_数据手册查询_规格书查询_datasheet查询_IC查询 (semiee.com)

2、手机端

推荐APP半导小芯,可以直接在手机上查看数据手册,芯片型号众多。

二、bpi flash时序分析

数据手册我使用的是cypress的S29GL01GP,也是英飞凌-Infineon的S29GL01G,下载Infineon的S29GL01G也是一样的,为啥一样,感兴趣的同学可以百度一下。国产的bpi flash也大多是按照S29GL01来设计的。

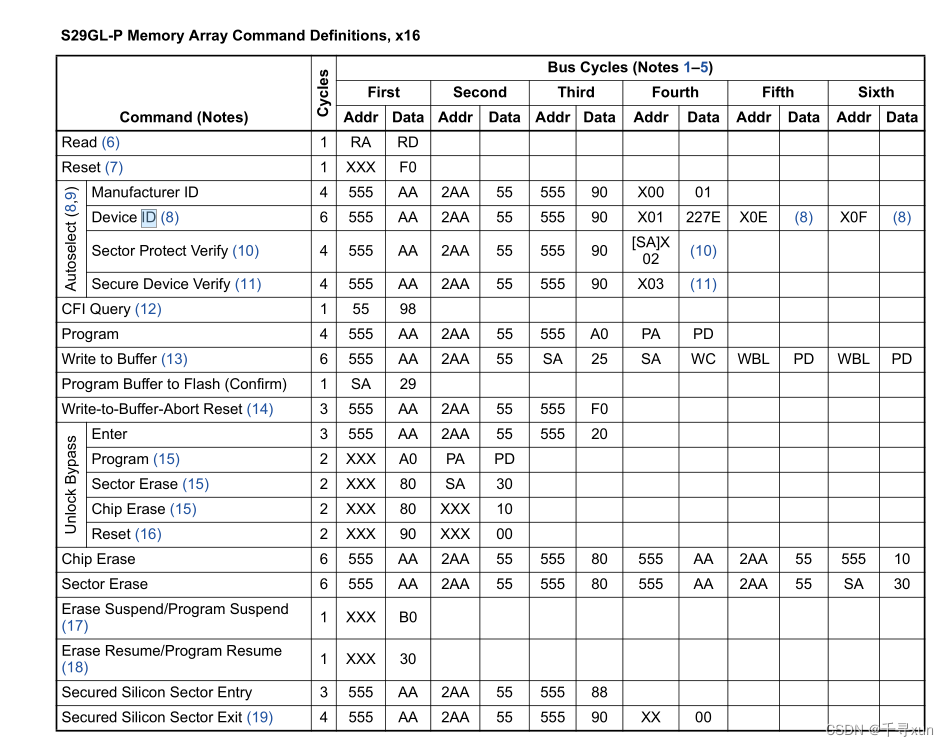

1、命令码介绍

现在的芯片功能都非常的多,也很复杂,都需要先发送正确的命令码,芯片才会执行相应操作,今天先讲解一下最简单的操作:读芯片ID号。

先找到数据手册中的这个命令表x16模式(x8模式的不一样,具体选择哪一个根据硬件连接来看,上一章有讲过),这上面说明了你想执行操作时需要发送的命令码。

先看看读ID需要发送那些指令。

第一个制造商ID :

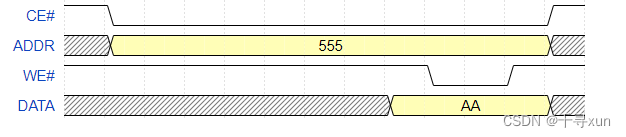

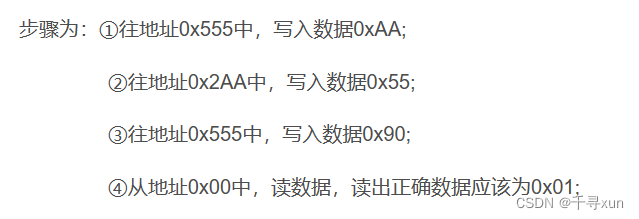

步骤为:①往地址0x555中,写入数据0xAA;

②往地址0x2AA中,写入数据0x55;

③往地址0x555中,写入数据0x90;

④从地址0x00中,读数据,读出正确数据应该为0x01;

具体的读和写时序我们也需要按照数据手册执行。

2、写入时序分析

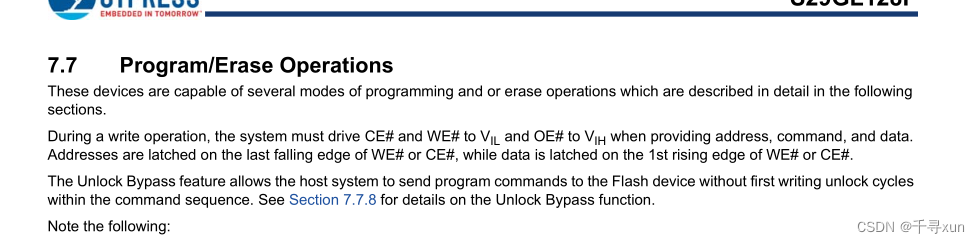

写入时序需要看数据手册的这些部分:

百度翻译一下:

这些器件能够进行多种编程和/或擦除操作模式,这些模式将在以下部分中详细描述。

在写入操作期间,当提供地址、命令和数据时,系统必须将CE#和WE#驱动到V IL,将OE#驱动到VIH。

地址被锁存在WE#或CE#的最后一个下降沿,而数据被锁存到WE#或CE的第一个上升沿。

解锁旁路功能允许主机系统向闪存设备发送程序命令,而无需在命令序列中首次写入解锁周期。有关解锁旁路功能的详细信息,请参见第7.7.8节

最重要的信息是:

地址被锁存在WE#或CE#的最后一个下降沿,而数据被锁存到WE#或CE的第一个上升沿。

地址在WE#或CE#的最后一个下降沿锁存,数据在WE#或CE的第一个上升沿锁存。

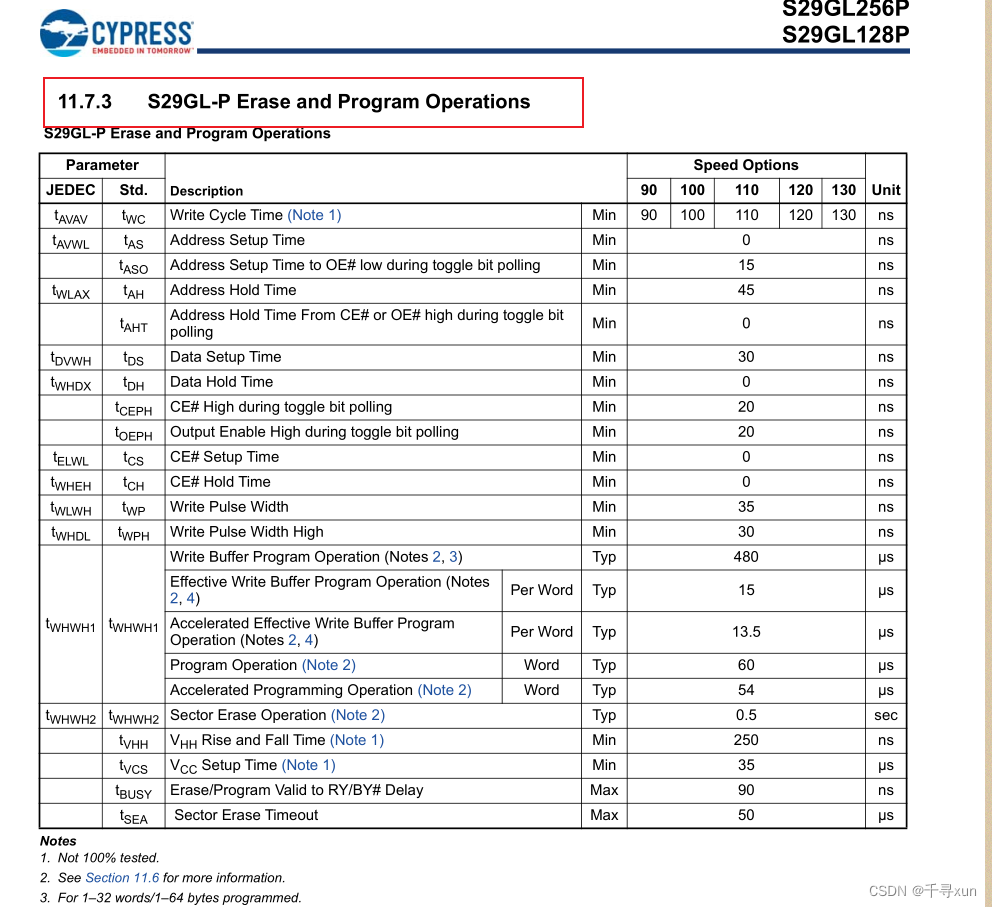

AC(交流)特性:

往后面滑,找到关于数据写入的时序,写入数据在flash中称为编程(program)

这一页为时序图中个参数的要求:

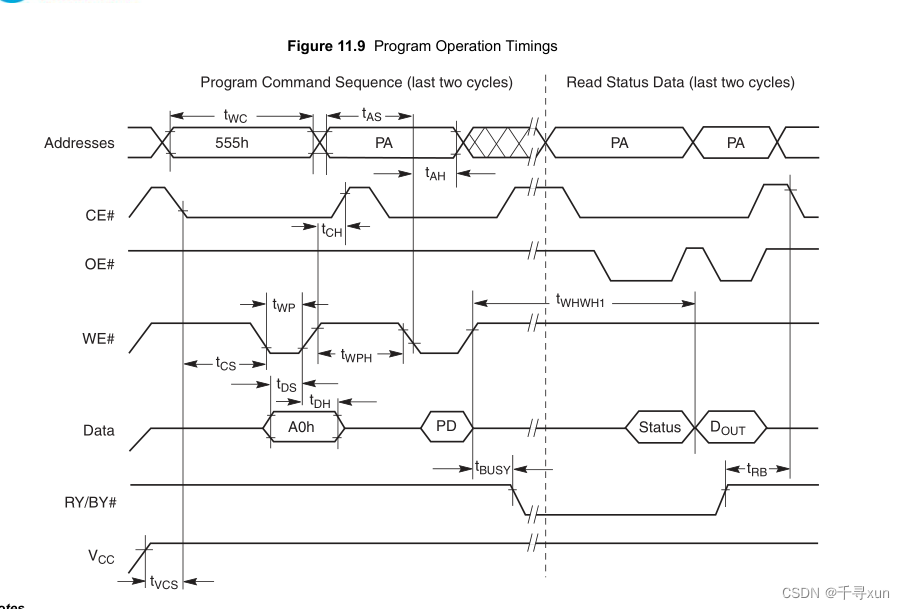

这一页为写时序波形图,图中参数应按照上图参数要求来进行设定:

写时序的时候不会用到OE#信号,这个信号让它一直为高电平(1);

上面写数据看似很复杂,但我们把它拆开一个一个数据对的来看就不复杂了。

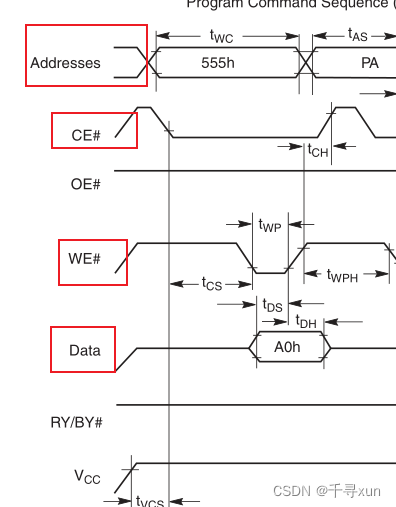

主要关注下面4个信号,写时序OE#让它一直为高。

这里需要关注的参数:Twc,Twp,tDS,Twph;使用FPGA设定这几个时序还是挺简单的,无硬件开发板时,可以仿真抓波形,有硬件开发板时,可以在线调试抓波形,再和数据手册中的时序波形进行对比,很容易看出是哪里出错了。

Tcs,Tch,Tdh在上面数据手册中写道min(最小)可以是0,我们就不用特别在意这几个参数,如果你的数据手册中这几个参数的最小值不是0,那就需要注意一下时序的设定了。

我们继续分析Twc,Twp,tDS,Twph:

Twc这个是写周期时间,和器件速度相关,我们选个中间值110吧,我们在设定时序Twc时应该大于等于110NS,意思就是这个芯片的写时序最快也要110ns才能发起一次,如果不按照数据手册的时序执行,那么很可能芯片就不会响应你的指令。

我们可以就把数据DATA的保持时间设定为大于等于110ns。就是在110ns内保证数据稳定,不能变化。

Twp就是WE#低电平脉冲的宽度,也是WE#低电平应该保持的时间,数据手册中写的是min最小35NS,我们设置的时候WE#低电平脉冲的宽度大于等于35NS就好了。

Twph:这个是WE#信号变为低电平后,重新返回高电平时的最低保持时间,最低是30ns.

Tds:这个是数据data的建立时间,意思就是在WE#的上升沿采样之前,数据应该保持稳定不变的时间,这个时间数据手册中最小为30NS,我们在设定时序时需要大于等于30ns。

建议:(这些参数都只给了最小值,建议在使用时没有对时间的要求,尽量将这些参数设置为2倍左右,因为器件在不同寿命,不同温度等条件下这些参数不是固定的,而且使用次数多了过后性能都会下降,这些参数就有可能会超出数据手册范围(几率很小),避免出现数据读取错误情况,若是对时间无特别高的要求,尽量将这些参数时间放宽一点。)

如果你看数据手册中的时序波形图不太明白,可以按照下面这个时序来进行设置,当然上面说的那些时间参数必须也要遵守。(这里没有OE#,按照上面说的,让它一直为高就好了)

上面是往555地址写入AA 的时序,记得之前读ID需要的命令码吗,这里相当于执行了第一步,第二、三步按照第一步的方法把地址数据换一下就可以了。

上面说的写时序就是整个FLASH的编程操作,只要数据手册中用到写操作的,都可以用上面这个时序。

读ID操作这样只剩下最后一步④了,下面简单说一下读时序吧。

2、读取时序分析

说一下数据手册中的描述吧,先使用单个地址读的方式,学会了单个读,页读也不难。

还是百度翻译吧:

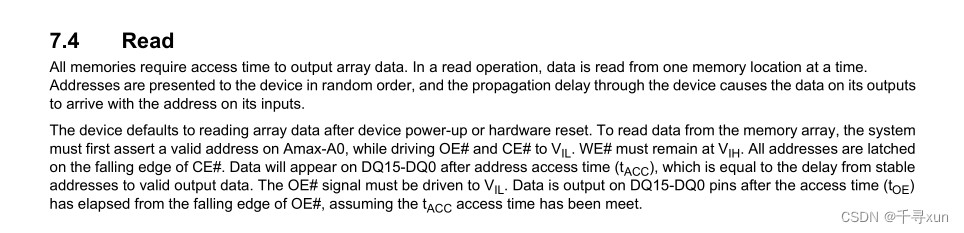

所有存储器都需要访问时间来输出阵列数据。在读取操作中,一次从一个存储位置读取数据。地址以随机顺序提供给设备,通过设备的传播延迟导致其输出端的数据与输入端的地址一起到达。

设备默认为在设备通电或硬件重置后读取阵列数据。要从存储器阵列读取数据,系统必须首先在Amax-A0上断言有效地址,同时将OE#和CE#驱动到V IL。WE#必须留在V IH。所有地址都锁存在CE#的下降沿。在地址访问时间(t ACC)之后,数据将出现在DQ15-DQ0上,该时间等于从稳定地址到有效输出数据的延迟。OE#信号必须驱动至V IL。假设已经满足t ACC访问时间,则在从OE#的下降沿经过访问时间(t OE)之后,在DQ15-DQ0引脚上输出数据。

个人理解的大概意思就是:

FALSH输出数据需要一定的时间,我们要按照数据手册中的要求,才能正确读出数据,具体的还是在后面时序分析上讲。

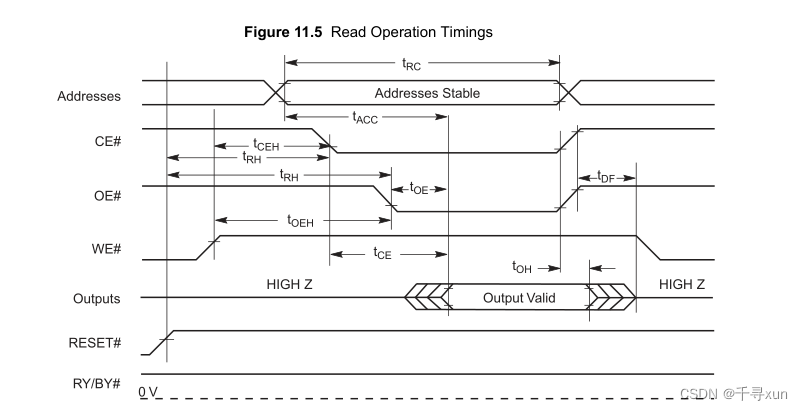

还是按照写入时序一样的讲吧,两张重要的图:

还是在交流特性这下面找:

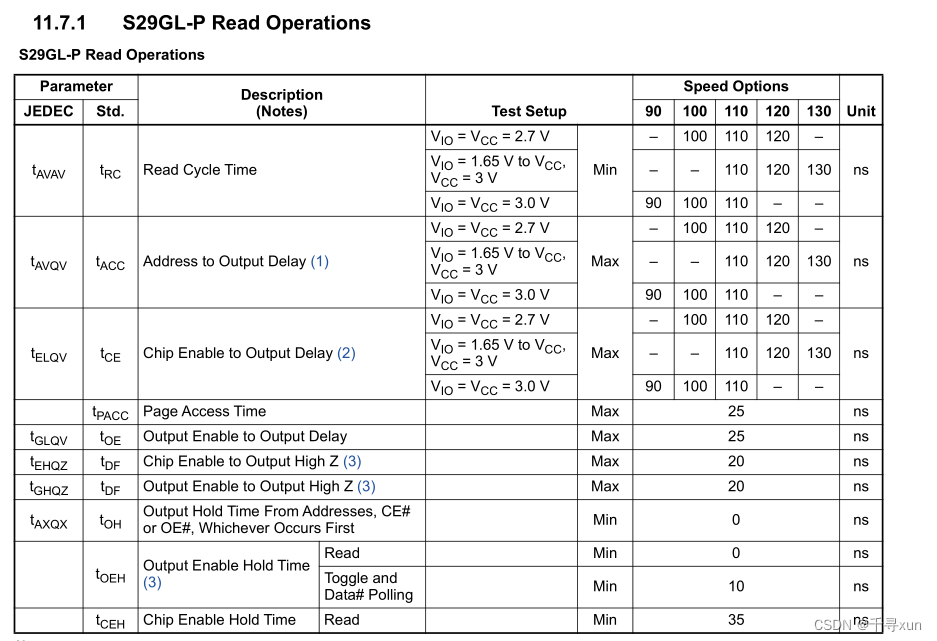

这个单个读时序需要特别关注的时间参数:Tacc,Trc,Toe,Tce;

其他参数按照上面说的设置便好,如Tceh,就是CE#高电平需要保持的最低时间,一般设置时CE#为高大于35NS后再拉低即可。

Trc:这个是读取周期,和写入周期差不多。就不多说了。

Tacc:这个是地址输出有效到输出数据有效的延时时间,简单来说就是地址保持时间,地址需要保持保持不变的最低时间,这个也是和器件相关,如果速度等级是110,大于等于110ns即可。

Tce:CE#使能(为低电平)时,数据输出有效的最低时间,就是ce#低电平保持时间。这个和Tacc一样,这两个参数我们就可以一起进行设置。

Toe:OE#使能(为低电平)时,数据输出有效的最低时间,就是oe#低电平保持时间。数据手册上这里最小是25NS,所有我们在设置OE时,低电平时间要打印等于25NS。

WE#信号在读取时,让它一直为高。

每次读写都必须满足上面的时间要求。

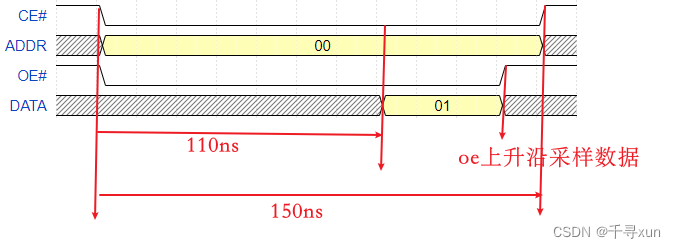

推荐刚开始使用者可以使用下面的时序:

同时将OE、CE拉低,地址进入保持状态,110NS过后数据就会输出到DATA上,数据采样可以在110ns之后,OE上升沿及之前,整个读取周期时间可以自己设置,下图只是举例。

这样就完成对flash ID的读取,能成功读取ID说明以及成功一半了,已经能和flash建立连接了。

总结:

主要需要学会看数据手册以及时序图,按照数据手册总的时序图建立时序,使用FPGA可以离线仿真以及在线仿真,对照着数据手册中的时序图进行分析,很容易看出自己写的代码哪里出问题了。

欢迎大家评论,以上若有错误之处,欢迎指正。

有人需要的话,后面再讲讲读、写、擦操作。

本文指导读者如何下载数据手册,重点解析了bpiflash的命令码介绍、写入和读取时序,包括S29GL01GP芯片的操作步骤和时序参数设置,强调了理解和遵循数据手册的重要性。

本文指导读者如何下载数据手册,重点解析了bpiflash的命令码介绍、写入和读取时序,包括S29GL01GP芯片的操作步骤和时序参数设置,强调了理解和遵循数据手册的重要性。

1739

1739

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?