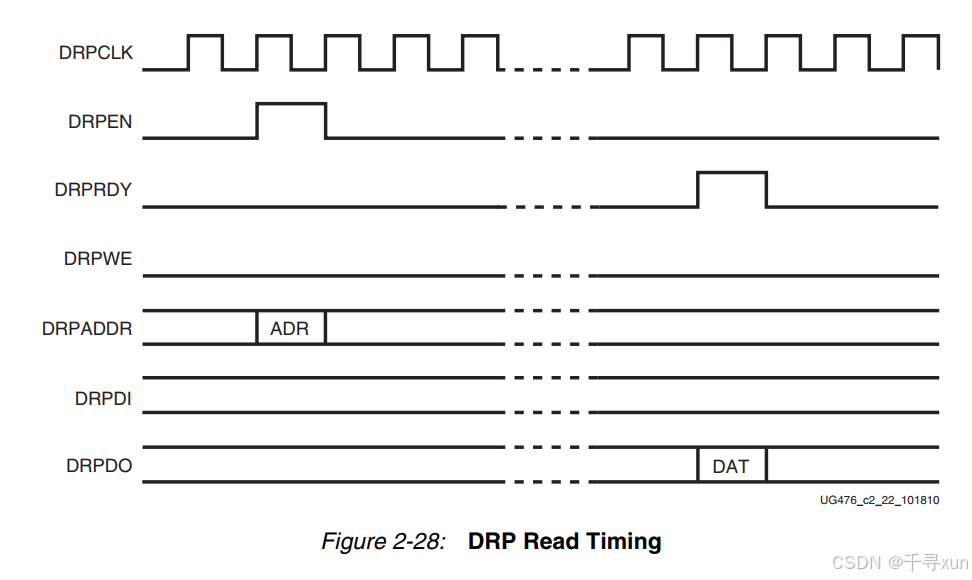

一、DRP读写时序

1、DRP写时序

2、DRP读时序

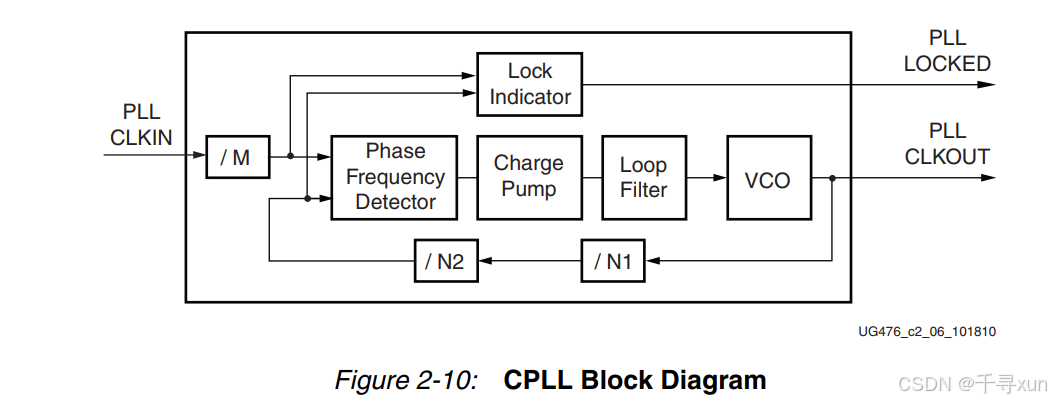

二、CPLL DRP配置方法

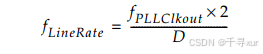

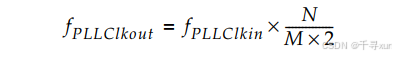

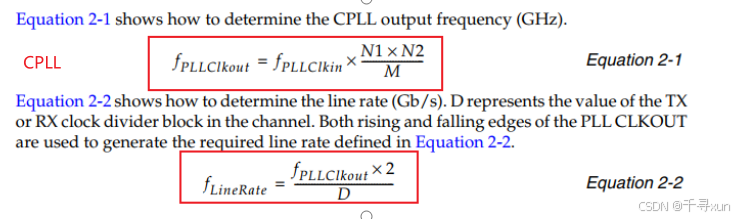

1、CPLL线速率计算公式:

根据箭头方向可以看出:PLLCLKIN/M=(PLLCLKOUT/N1)/N2;所以得到:

![]()

发送/接收端使用双沿(上升沿和下降沿)进行采样,双沿采样速率为2×fpllclkout 。

fpllclkout为CPLL输出频率,flinerate为线速率(如:1.25G、5G等)。GTX中CPLL范围为1.6 GHz到3.3 GHz。所以GTX中使用CPLL能达到最高线速率为6.6G。

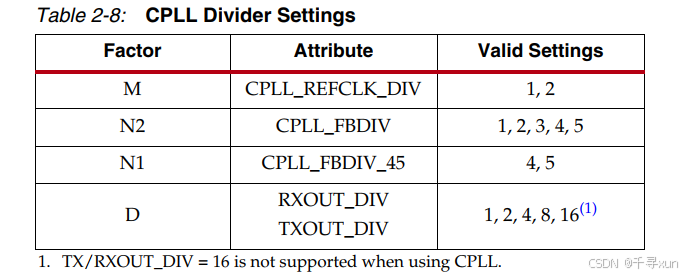

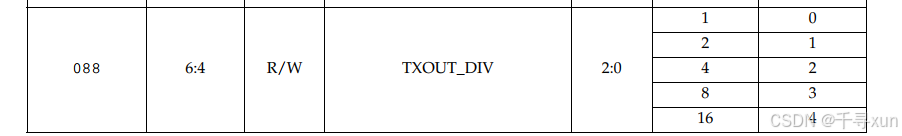

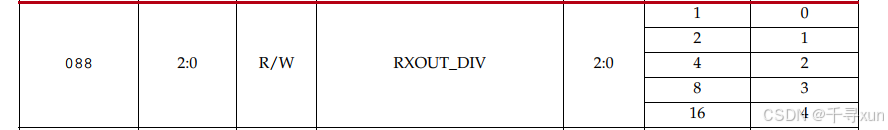

2、公式中各参数对应的寄存器

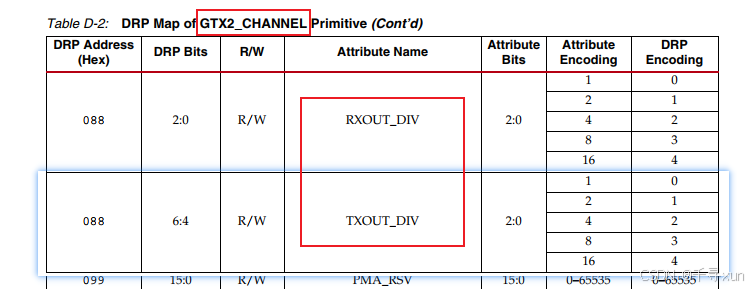

例如:配置参数M=1,N1=5,N2=4,D=1。实际往DRP寄存器中配置参数为CPLL_REFCLK_DIV=16,CPLL_FBDIV_45 =1,CPLL_FBDIV=2,TXOUT_DIV=RXOUT_DIV=0。

| 速率 | CPLL DRP配置 | ||||

| GT_REFCLK | line rate(Gb/s) | M | N1 | N2 | D |

| 125Mhz | 1.25 | 1 | 5 | 4 | 4 |

| 2.5 | 1 | 5 | 4 | 2 | |

| 3.125 | 1 | 5 | 5 | 2 | |

| 5 | 1 | 5 | 4 | 1 | |

| 6.25 | 1 | 5 | 5 | 1 | |

| 156.25Mhz | 1.25 | 1 | 4 | 4 | 4 |

| 2.5 | 1 | 4 | 4 | 2 | |

| 3.125 | 1 | 5 | 4 | 2 | |

| 5 | 1 | 4 | 4 | 1 | |

| 6.25 | 1 | 5 | 4 | 1 | |

速率配置过程中需对GTX进行复位,配置完后取消复位。

三、QPLL DRP配置方法

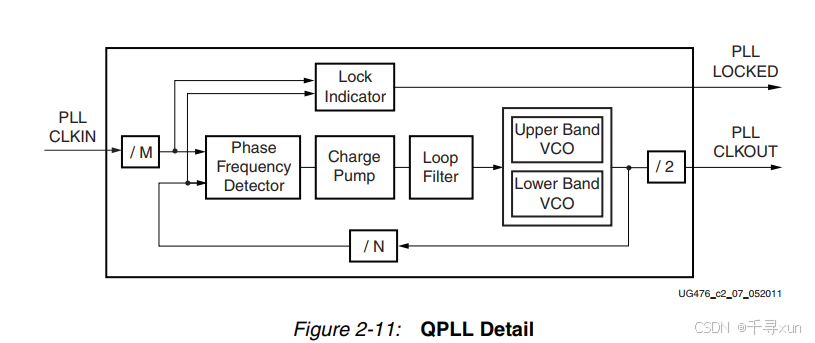

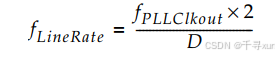

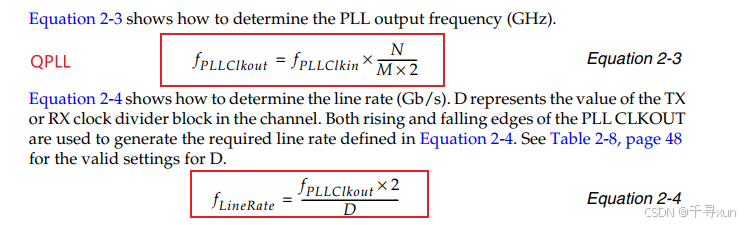

1、QPLL线速率计算公式:

根据箭头方向可以看出:PLLCLKIN/M=(2*PLLCLKOUT)/N;所以得到:

发送/接收端使用双沿(上升沿和下降沿)进行采样,双沿采样速率为2×fpllclkout 。

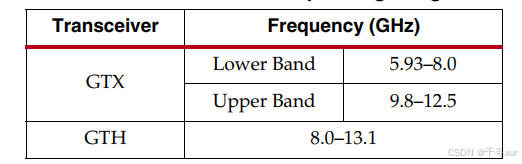

fpllclkout为QPLL输出频率,flinerate为线速率(如:1.25G、5G等)。GTX中QPLL范围如下:

根据公式计算GTX中最高线速率为25Gb/s(fpllclkout=12.5、D=1),最低线速率约为0.75Gb/s(fpllclkout=5.93、D=16)。所以在GTX中线速率超过6.6G时,只能选择QPLL。线速率低于6.6G时CPLL和QPLL都能选择。

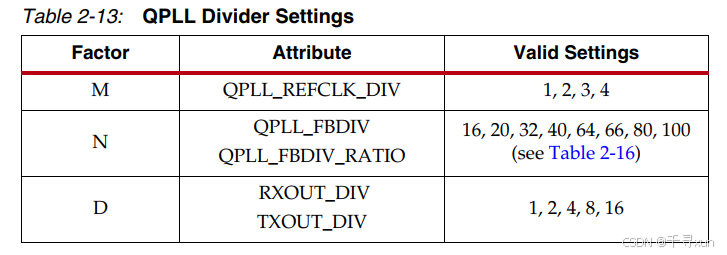

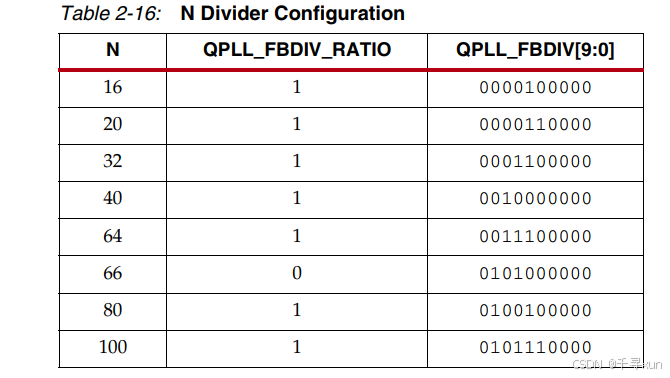

- 公式中各参数对应的寄存器

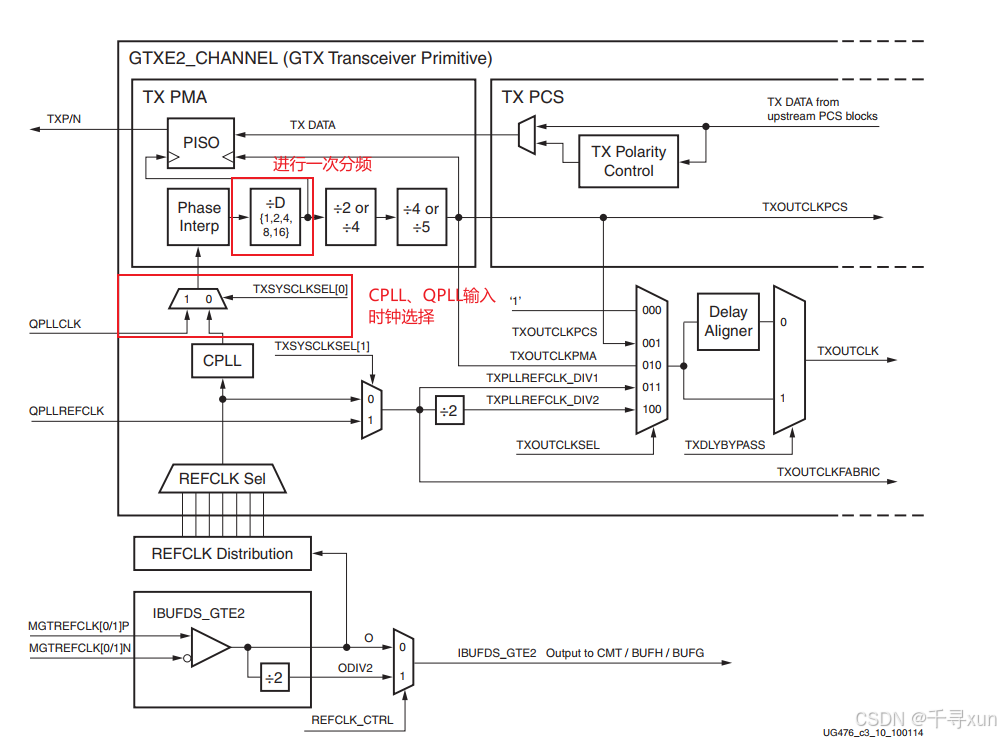

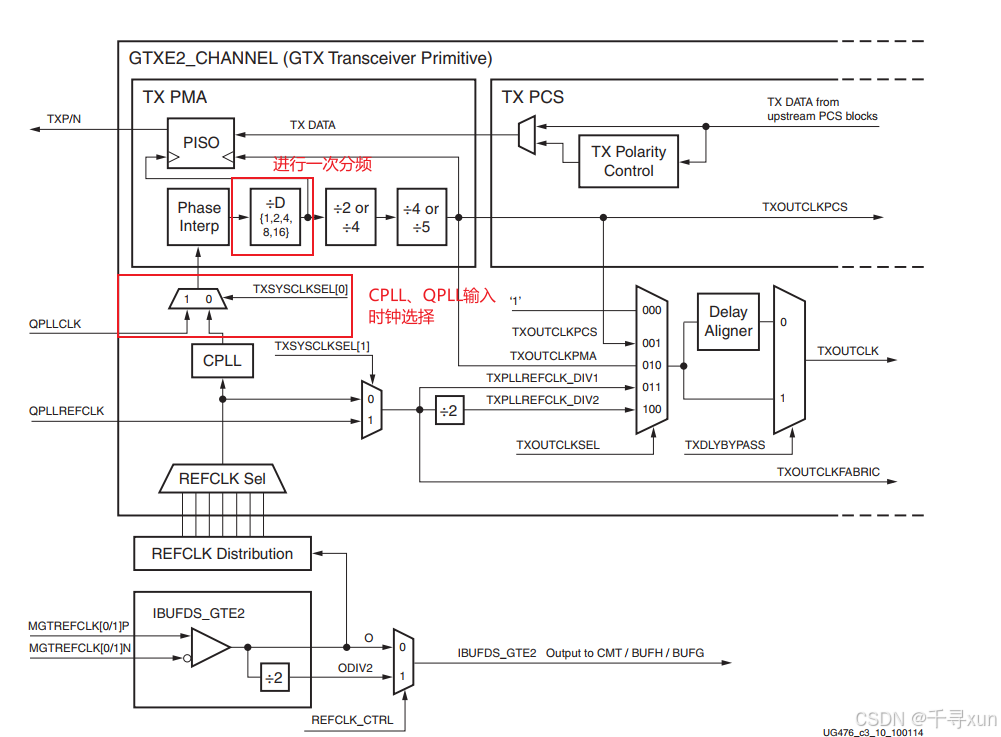

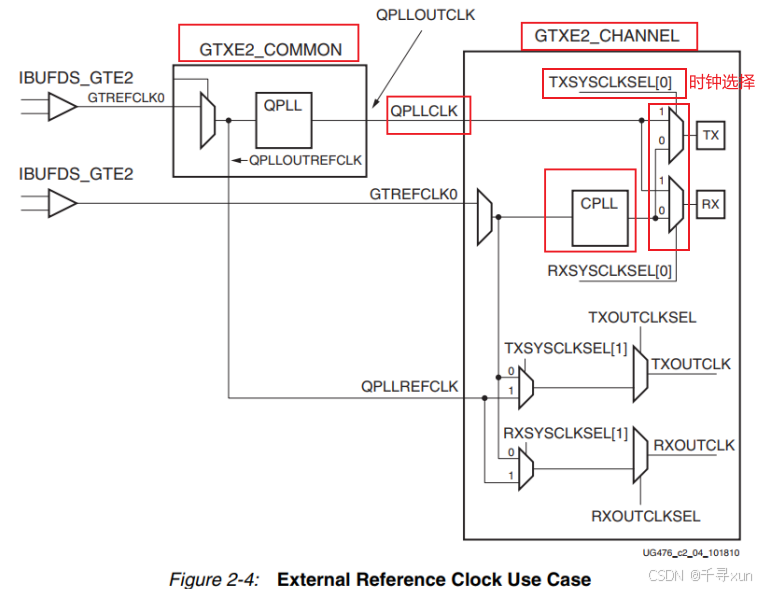

四、GTX时钟分析

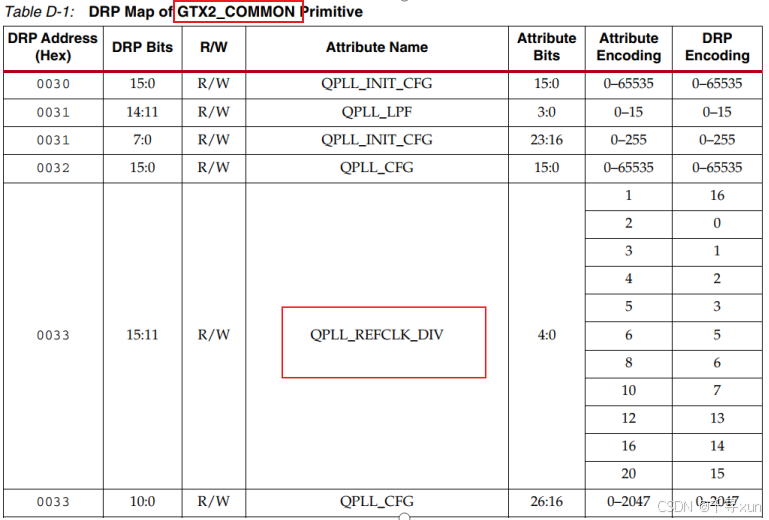

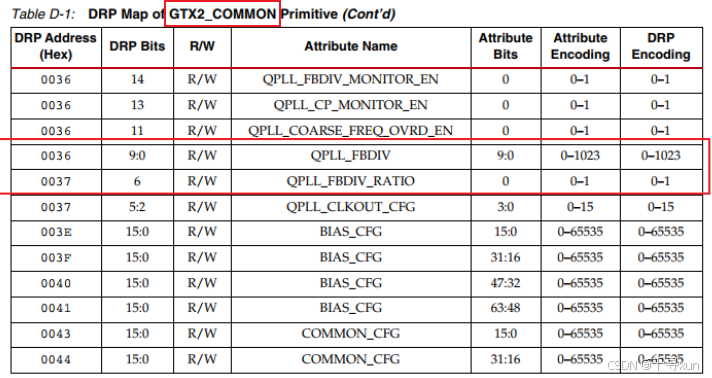

配置QPLL时需注意QPLL_REFCLK_DIV、QPLL_FBDIV、QPLL_FBDIV_RATIO在 GTX2_COMMON的DRP寄存器中进行配置,而TXOUT_DIV、RXOUT_DIV参数需在 GTX2_CHANNEL的DRP寄存器中进行配置。

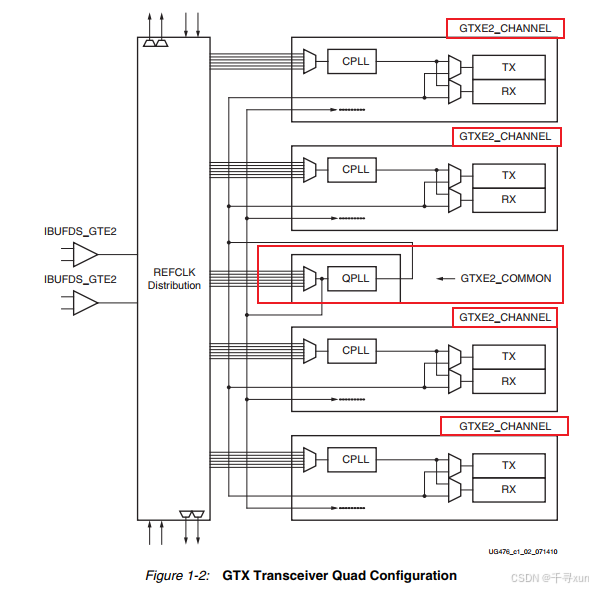

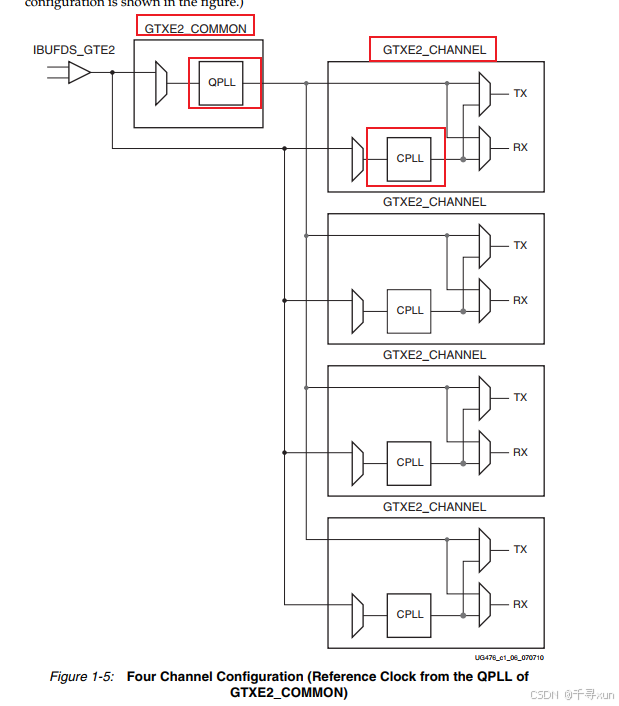

配置CPLL的参数都是在GTX2_CHANNEL的DRP寄存器中进行配置。具体原因与GTX结构相关:

一个GTX Quad(bank)中包含4个GTXE2_CHANNEL,1个GTXE2_COMMON。GTXE2_COMMON是4个GTXE2_CHANNEL共用的,所以需要单独配置,而不能在某一个GTXE2_CHANNEL中进行配置。QPLL资源是在GTXE2_COMMON中,CPLL资源是在GTXE2_CHANNEL中。

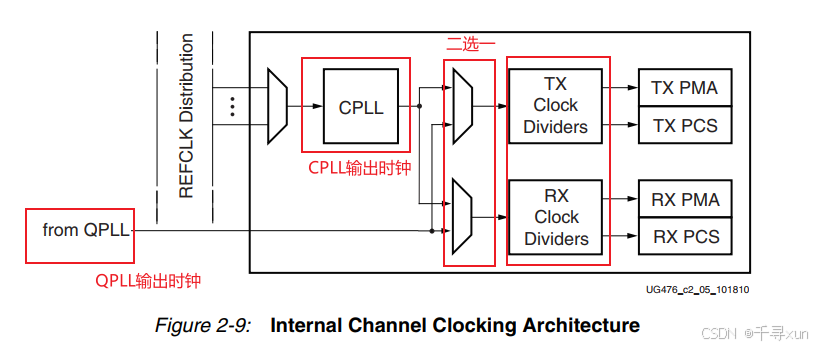

根据CPLL和QPLL计算速率公式中可以看出,计算线速率公式都是一样的,只有计算PLL输出频率公式不一致。

CPLL公式:

QPLL公式:

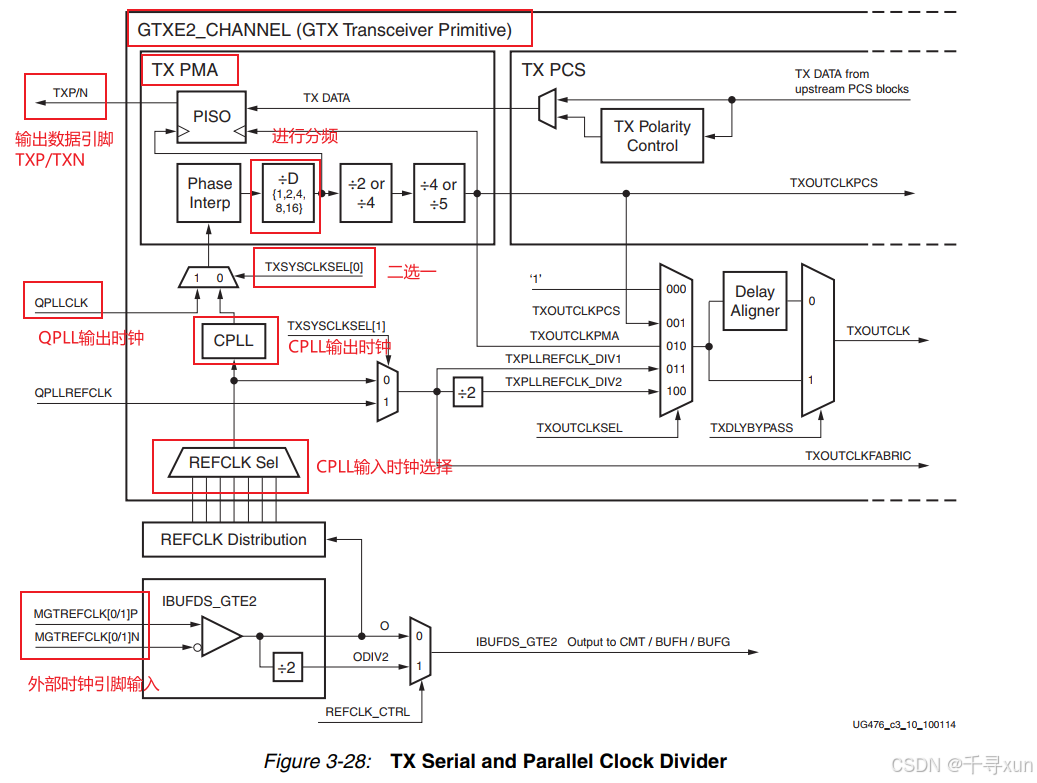

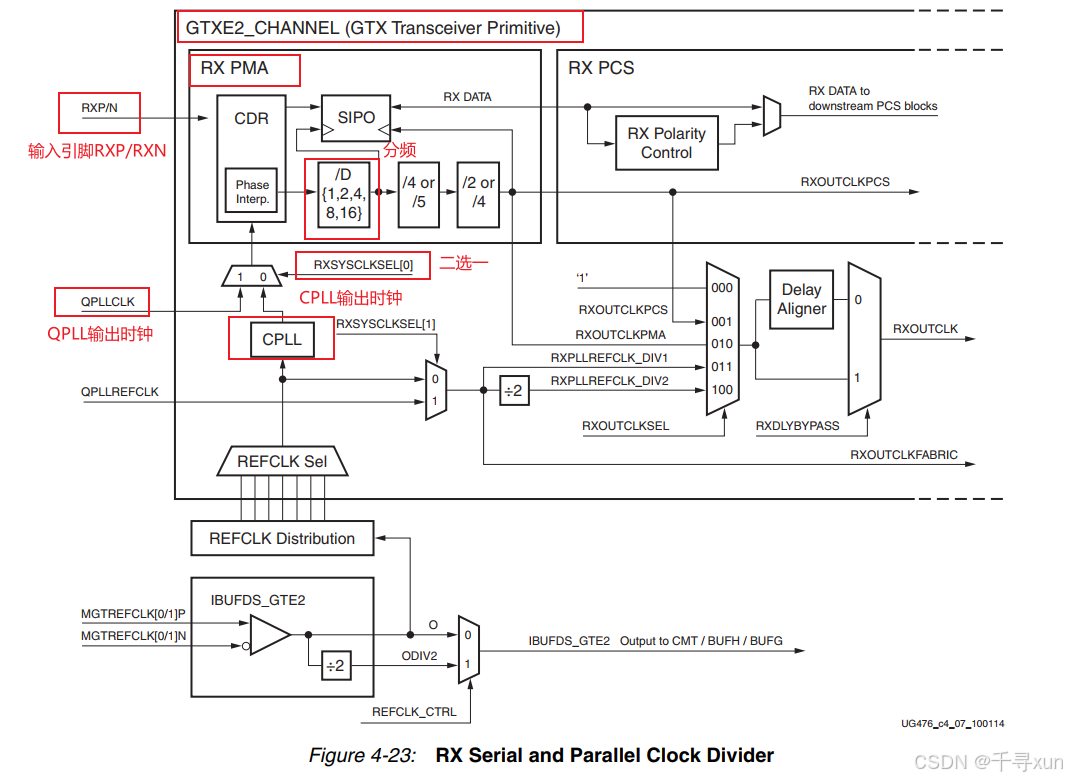

CPLL和QPLL计算线速率Flinerate相同原因在于输入TX/RX时会进行二选一,选择CPLL和QPLL输出频率中的一个,然后再进行一次分频,从而得到Flinerate。

GTX TX输出端时钟结构:

GTX RX输入端时钟结构:

1150

1150

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?