1.背景

目前FPGA已广泛应用于大规模、复杂系统设计中,尽管FPGA资源丰富,但是在大型系统中,单片FPGA资源远远不能满足一般设计应用的要求,或者说单颗顶配的FPGA可以满足资源相关需求,但是价格极高,对于成本敏感的企业,选择顶配FPGA并不是首选方案,因此多片FPGA集成使用成为了实用方案。多片FPGA级联使用,即将多个FPGA当做一个FPGA来用,今天来分享下把多个FPGA当做一个FPGA来用的硬件架构。

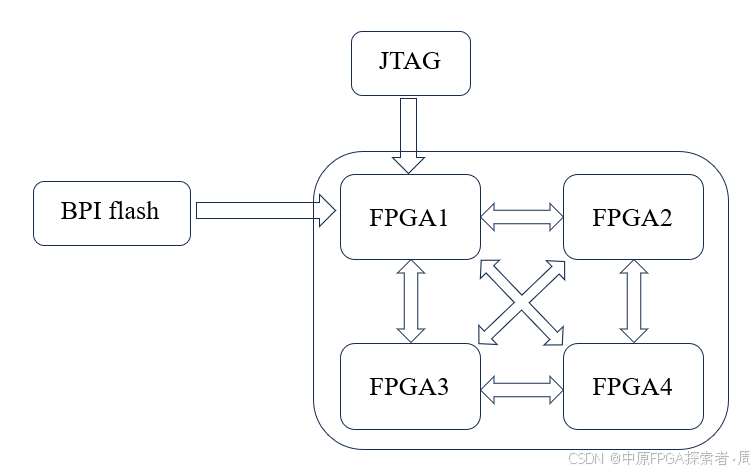

2.系统原理框图

多片FPGA级联设计原理框图如下:主要采用一片BPI Flash芯片配置多片FPGA,BPI Flash中存储了这些FPGA的配置程序。FPGA1为主FPGA,其余为从FPGA。FPGA与FPGA之间通过并行数据线连接,一般都是高速并行接口;BPI Flash和JTAG均与主FPGA连接,主FPGA配置方式为Master BPI模式;其余FPGA配置电路采用菊花链的连接方式,配置方式为Slave SelectMAP模式。

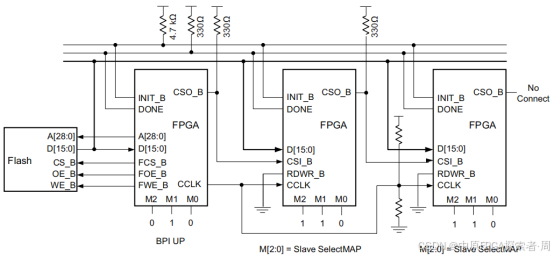

3.多片FPGA配置连接方式

多片FPGA的级联设计,配置连接方式如下图,主FPGA配置方式为Master BPI模式,M[2:0]=010;其余FPGA配置方式为Slave SelectMAP模式,M[2:0]=110,配置电路采用菊花链的连接方式。此种配置方案,仅仅通过一个JATG接口一次烧录即可完成多个FPGA的程序下载。烧录配置程序是由多个fpga的bit流文件生成的mcs文件。

具体Master BPI与Slave SelectMAP的详细连接电路,请参考xilinx ug470文档。

734

734

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?