EDA设计基础练习题 :

1、设计一个三输入或非门电路。

2、三输入三输出电路设计:

输入A为1时,对应输出为1,A为0时,输出为0;

输入B为1时,对应输出为0,B为0时,输出为1;

输入A、B、C有一个为1时,C对应输出为1。

3、十进制数编码电路:把0~9十个数编码成8421BCD码。

实验要求如下:

1、程序设计:编写完整实验程序;注明端口名称及意义;

2、仿真验证:编辑程序、编译、仿真。

| 编码对象 | 输入端口 | 输出端口 |

| I0、I1、I2、I3、I4、I5、I6、I7、I8、I9 | Q8、Q4、Q2、Q1 | |

| 0 | I0=1,其他为0 | 0000 |

| 1 | I1=1,其他为0 | 0001 |

| 2 | I2=1,其他为0 | 0010 |

| 3 | I3=1,其他为0 | 0011 |

| 4 | I4=1,其他为0 | 0100 |

| 5 | I5=1,其他为0 | 0101 |

| 6 | I6=1,其他为0 | 0110 |

| 7 | I7=1,其他为0 | 0111 |

| 8 | I8=1,其他为0 | 1000 |

| 9 | I9=1,其他为0 | 1001 |

| 其他情况 | 1111 |

代码

1、设计一个三输入或非门电路。

三输入或非门 —— 三个输入端,先或后非,即先进行三输入的或运算,再整体取非运算

三输入端或非门的裸机表达式如下:

![]()

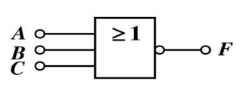

逻辑符号:

实体声明部分:定义三个输入端口A、B、C;一个输出端口output,变量类型都是std_logic

library IEEE;

USE IEEE.STD_logic_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_logic_unsigned.ALL;

-- 实体声明

ENTITY ShiYan6 IS

PORT(

A,B,C : IN std_logic;

output :out std_logic

);

END ShiYan6;

--结构体说明

ARCHITECTURE behave OF ShiYan6 IS

BEGIN

PROCESS (A, B, C)

BEGIN

--三输入或非门 描述

output <= NOT (A OR B OR C);

END PROCESS;

END behave;

2、三输入三输出电路设计:

输入A为1时,对应输出为1,A为0时,输出为0;

输入B为1时,对应输出为0,B为0时,输出为1;

输入A、B、C有一个为1时,C对应输出为1。

这个三输入三输出直接根据需求写对应代码

简单表达就是

- OUTA <= A;

- OUTB <= NOT B;

- OUTC <= A OR B OR C;

library IEEE;

USE IEEE.STD_logic_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_logic_unsigned.ALL;

-- 实体声明

ENTITY ShiYan6 IS

PORT(

A,B,C : IN std_logic;

OUTA :out std_logic;

OUTB :out std_logic;

OUTC :out std_logic

);

END ShiYan6;

--结构体说明

ARCHITECTURE behave OF ShiYan6 IS

BEGIN

PROCESS (A, B, C)

BEGIN

--三输入三输出 描述

OUTA <= A;

OUTB <= NOT B;

OUTC <= A OR B OR C;

END PROCESS;

END behave;

3、十进制数编码电路:把0~9十个数编码成8421BCD码。

编码电路,状态比较多,用case-when语句比较方便

-- 码转换 -case语句

library IEEE;

USE IEEE.STD_logic_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_logic_unsigned.ALL;

-- 实体声明

ENTITY ShiYan6 IS

PORT(

input : IN STD_logic_vector(9 downto 0);

output :out STD_logic_vector(3 downto 0)

);

END ShiYan6;

--结构体说明

ARCHITECTURE behave OF ShiYan6 IS

BEGIN

PROCESS (input)

BEGIN

--十进制数编码电路:把0~9十个数编码成8421BCD码

CASE input IS

WHEN "0000000001" => output <= "0000";

WHEN "0000000010" => output <= "0001";

WHEN "0000000100" => output <= "0010";

WHEN "0000001000" => output <= "0011";

WHEN "0000010000" => output <= "0100";

WHEN "0000100000" => output <= "0101";

WHEN "0001000000" => output <= "0110";

WHEN "0010000000" => output <= "0111";

WHEN "0100000000" => output <= "1000";

WHEN "1000000000" => output <= "1001";

when others => output <= "1111";

END CASE;

END PROCESS;

END behave;

附一个case-when语句用法

CASE 多值表达式 IS

WHEN 选择值 => 被赋值变量 <=赋值变量;

WHEN 选择值 => 被赋值变量 <=赋值变量;

WHEN 选择值 => 被赋值变量 <=赋值变量;

...

WHEN OTHERS =>被赋值变量 <=赋值变量;

END CASE总结

以上三种电路均采用了VHDL进行编程,体现了VHDL在电子设计自动化(EDA)中的灵活性和强大功能。每个电路都按照实验要求进行了程序设计,包括定义实体、端口映射以及内部逻辑实现。此外,还强调了仿真验证的重要性,尽管具体的仿真步骤未在此展示,但这是确保电路正确性的关键环节。

这些练习题覆盖了基本的组合逻辑电路设计,如或非门和编码器的设计,对于学习者来说是非常好的实践机会,可以加深对VHDL语言的理解,同时提高实际动手能力。在未来的课程中,建议进一步探索更复杂的电路设计,例如包含存储元件的时序电路,以及如何有效地使用仿真工具来进行测试和调试。

本代码纯自己手敲,拒绝白嫖!

本文介绍了EDA设计中的基础练习,包括三输入或非门电路的实现、三输入三输出电路的设计以及十进制数的8421BCD编码,通过实例展示了如何使用标准逻辑库并使用case-when语句进行电路编程和仿真。

本文介绍了EDA设计中的基础练习,包括三输入或非门电路的实现、三输入三输出电路的设计以及十进制数的8421BCD编码,通过实例展示了如何使用标准逻辑库并使用case-when语句进行电路编程和仿真。

265

265

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?