一、FIFO相关基础知识

1、 FIFO的全称是:First-in-first-out。

FIFO可分为同步FIFO和异步FIFO。

同步FIFO:数据写入FIFO的时钟和数据读出FIFO的时钟是同步的。

异步FIFO:数据写入FIFO的时钟和数据读出FIFO的时钟是异步的。

注:读写时钟有特定的相位关系也属于同步时钟。

同步FIFO的作用:一般用来当做交互数据的一个缓冲,即其主要作用就是一个buffer。

异步FIFO主要有两个作用:第一实现数据在不同时钟域传输,第二实现不同数据宽度的数据接口。

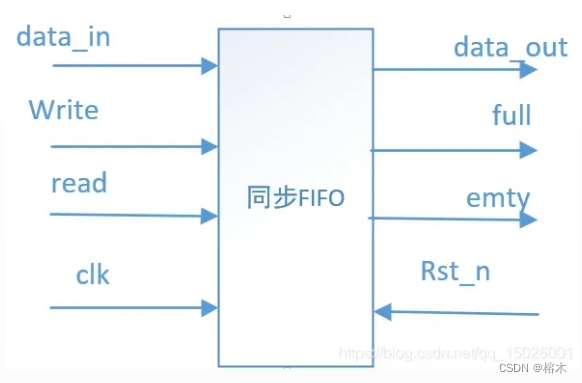

2、同步FIFO主要由三部分构成:(1)FIFO写控制逻辑:产生FIFO写地址、写有效信号、同时产生FIFO写满及写错等状态信号;(2)FIFO读控制逻辑:产生FIFO读地址、读有效信号、同时产生FIFO读空及写错等状态信号;(3)FIFO存储实体(如reg,memory)。

二、用Verilog实现同步FIFO

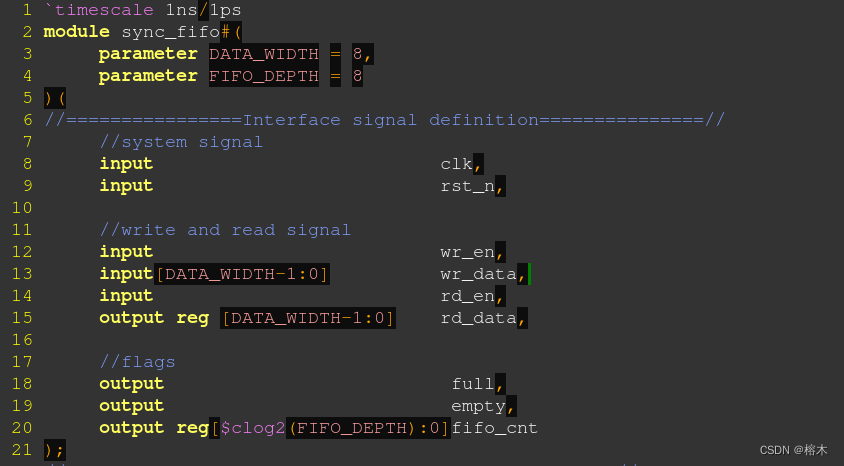

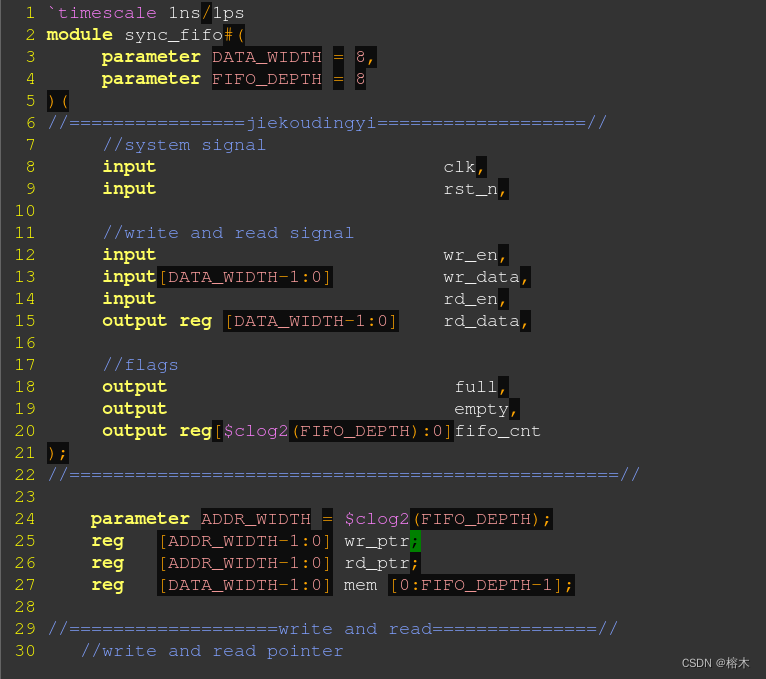

1、接口信号主要是:时钟(clk)、复位(rst_n)、写端口信号和读端口信号。尽可能参数化定义,便于使用时直接传参修改使用。

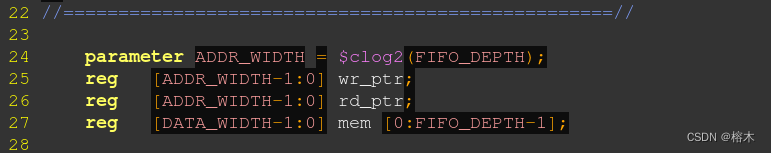

2、内部信号定义:写指针wr_ptr用于产生写地址,读指针rd_ptr用于产生读地址,用register定义memory。

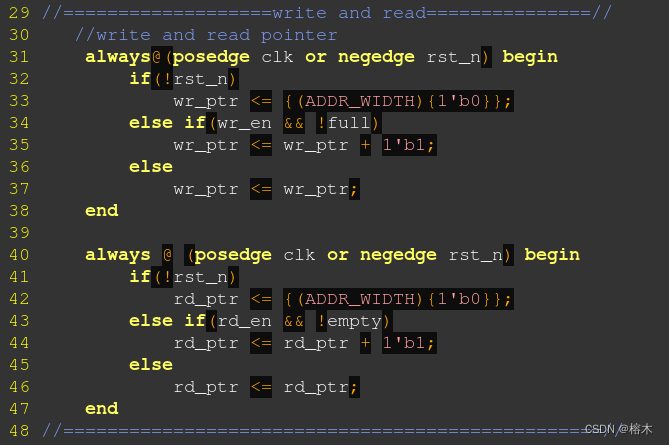

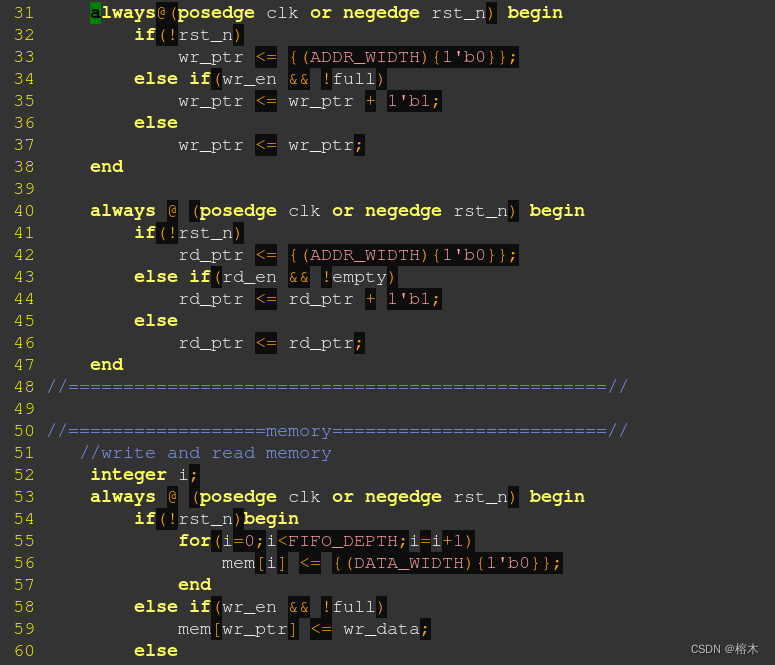

3、读写指针:当写使能到来,并且FIFO非满,写指针=写指针+1'b1;当读使能到来,FIFO非空,读指针=读指针+1'b1;读写指针有两个作用:第一用来产生读写数据memory,

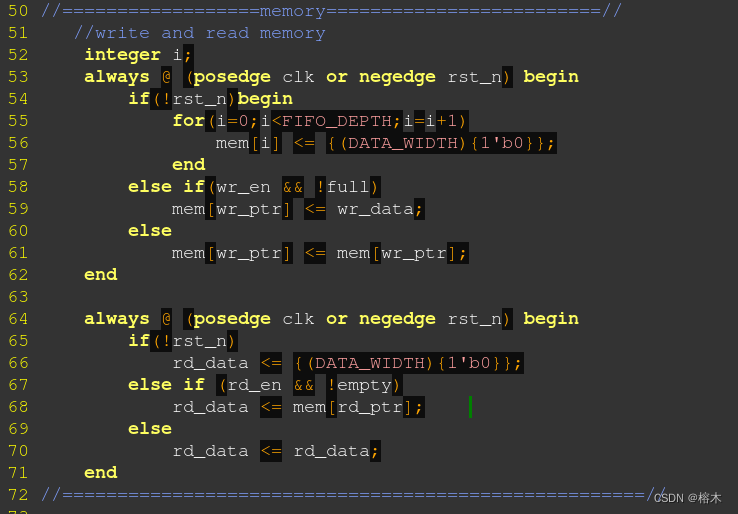

4、读写存储器memory,写入数据时,数组需要一位一位的索引,一位一位的赋值,因此在memory复位时采用了for循环进行复位,ps:for循环不耗时。通过读写指针控制memory是往memory里面写数据还是从memory里读数据。

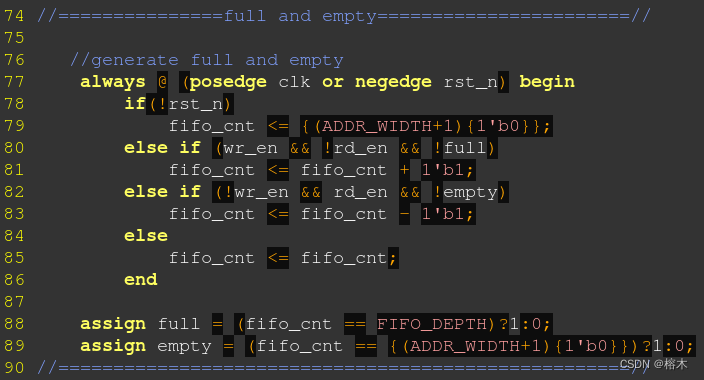

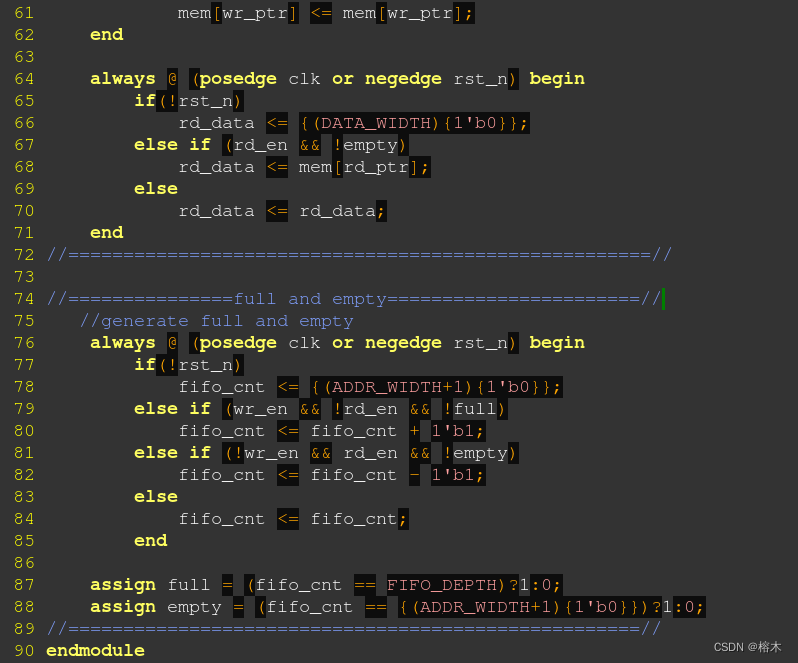

5、产生空满:空满信号由fifo_cnt产生。当写使能、非读并且非满的条件下fifo_cnt自加1'b1;当读使能、非写并且非空条件下fifo_cnt自减1'b1。

6、整体代码

三、同步FIFO测试

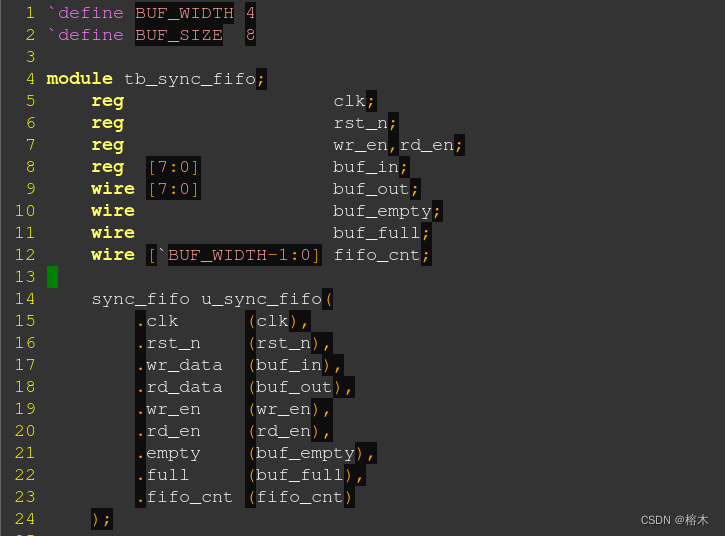

1、把所有输入端口信号改为reg,输出改为wire,以及实例化模块。

2、产生时钟并初始化。

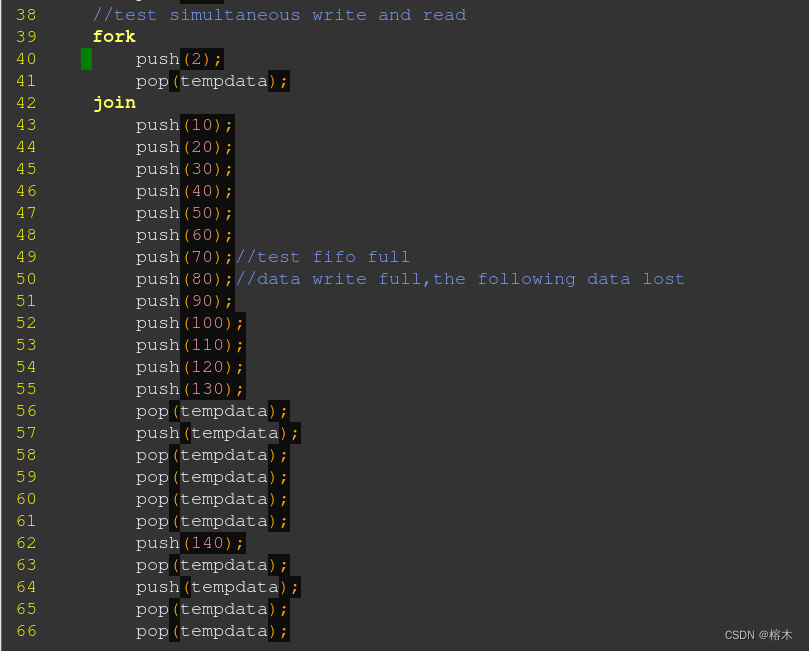

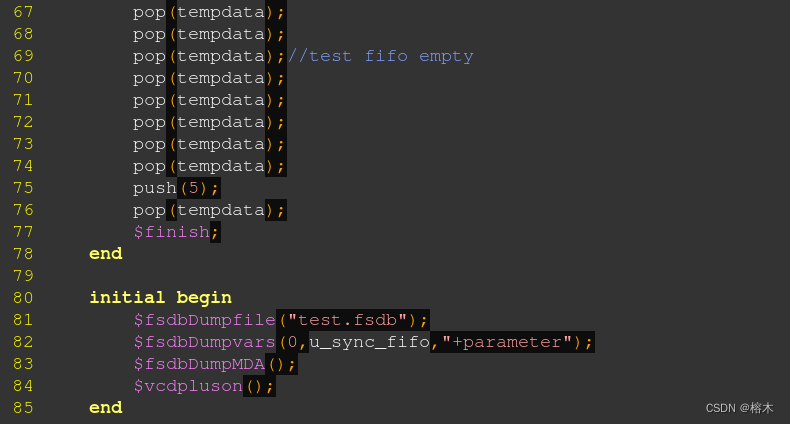

3、测试,调用task执行任务,task执行时间要在复位信号之后。

4、设计task。@(posedge clk)用于检测上升沿。

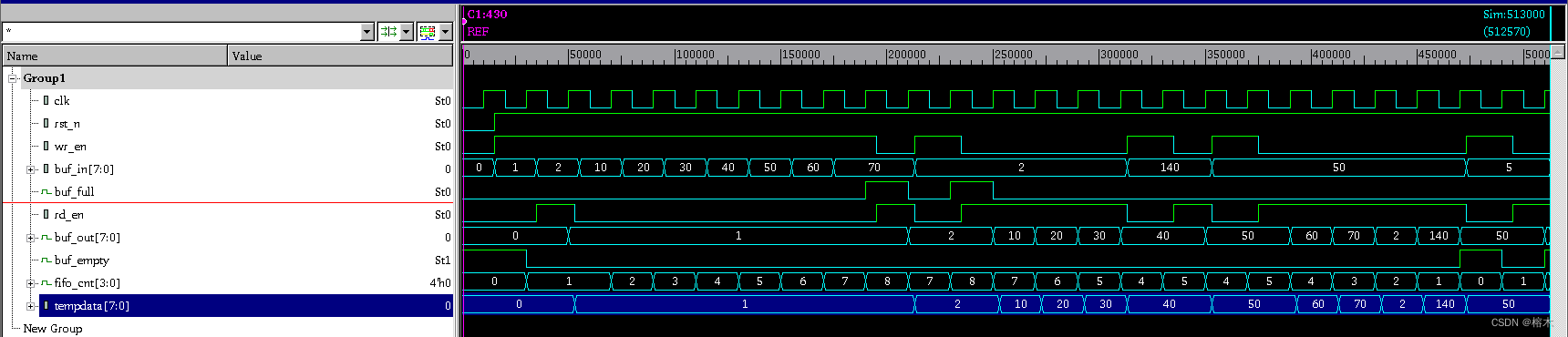

四、波形

新手小白还请各位大佬多多包涵!

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?