立创eda设计教程

1. 原理图的设计

2. PCB版绘制教程

3. 四层PCB板设计教程

简介

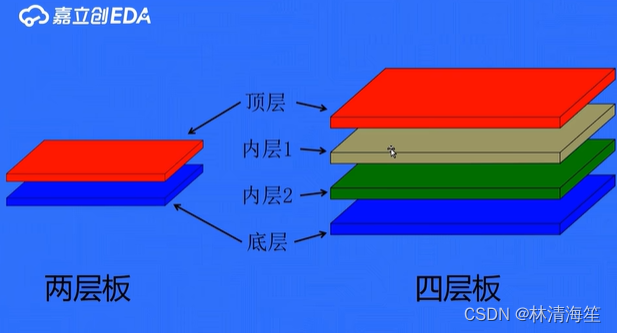

1.什么是四层板?

- 在默认情况下,四层板的顶层和底层的铜厚为1盎司,用于走关键信号线或者大电流的信号线。

- 内层1和内层2铜厚为0.5盎司,一般在内层进行GND铺铜和走电流相对较小的电源线和信号线。在四层板中,一般会将其中一个层设置为接地层,不走其他的线,这样就会有一个完整的地平面,可以更好的抗干扰,同时方便进行阻抗匹配。

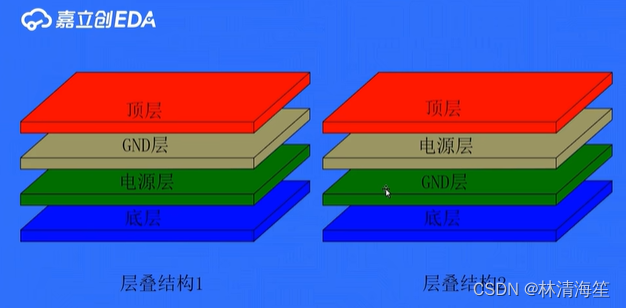

层叠结构

- 以四层板为例,一个层为GND层,另一个层为电源层。顶层和底层常用于走信号线,所以四层板常用的层叠结构有两种,第二层为GND或第三层为GND。不同的层叠结构对应不同的设计布局,根据设计来进行选择。

- 层叠设计的两个规则是,第一:每一个重要走线层都必须要有一个相邻的参考层(电源或接地层均可)第二:电源层和主接地层必须靠近摆放,以提供较大的耦合电容。

- 像四层板设计,如果器件都在顶层布局,或关键信号线在顶层走线的话,接地层最好放在第二层,然后第三层设置为电源层,底层走其余的线。如果器件在底层布局较多,或关键信号线在底层走线连接的话,接地层最好放置在第三层,保证关键信号线的质量减少干扰。

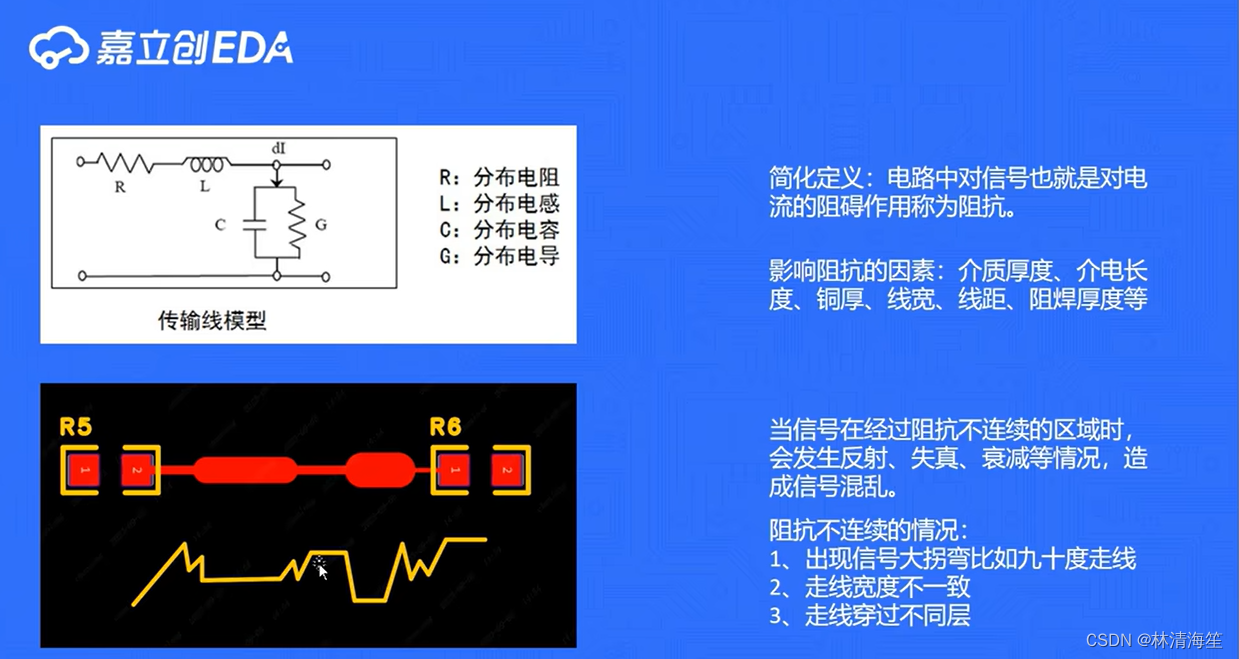

2.什么是阻抗匹配?

简化定义

- 首先阻抗并不是单纯的电阻,因为日常使用的器件并不是理想器件,而是会存在寄生电容,寄生电感,寄生电阻等这些参数会共同对电流起阻碍作用。

- 简化定义就是,在电路中对信号,即对电流的阻碍作用称为阻抗。

影响阻抗的因素

- 在PCB中,影响阻抗的因素有介质厚度,介电长度,铜厚,线宽,线距,阻焊厚度等等。

阻抗匹配

- 当信号经过阻抗不连续区域时,会发生信号反射、失真、衰减等情况,造成信号混乱。对于高速信号而言,这些情况很可能造成时序错误,从而导致通讯失败,比如两条或多条需要共同工作的信号线,如果传输信号速度很快,同时传输线之间阻抗差距比较大,一条线阻碍比较小,信号完整平稳地通过一条线阻碍比较大,信号存在较大的抖动,这就会导致信号混乱,时序错误。

- 所以在高速传输信号中,一般都会进行阻抗匹配,保证一组信号传输的一致性。在实际设计中,芯片厂家或常见的告诉传输线需要控制的阻抗大小一般都会直接告诉我们,我们仅需要根据对应计算

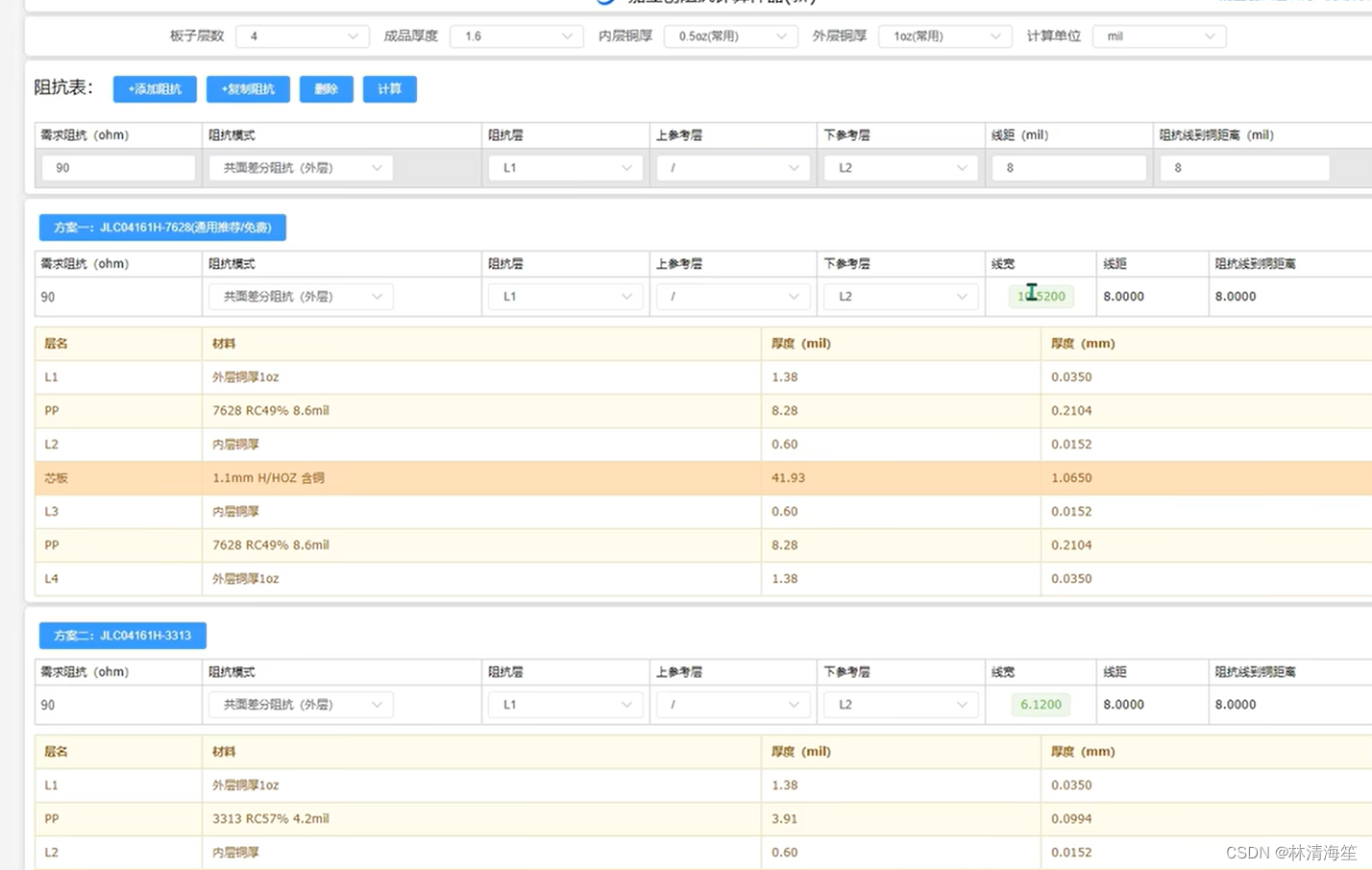

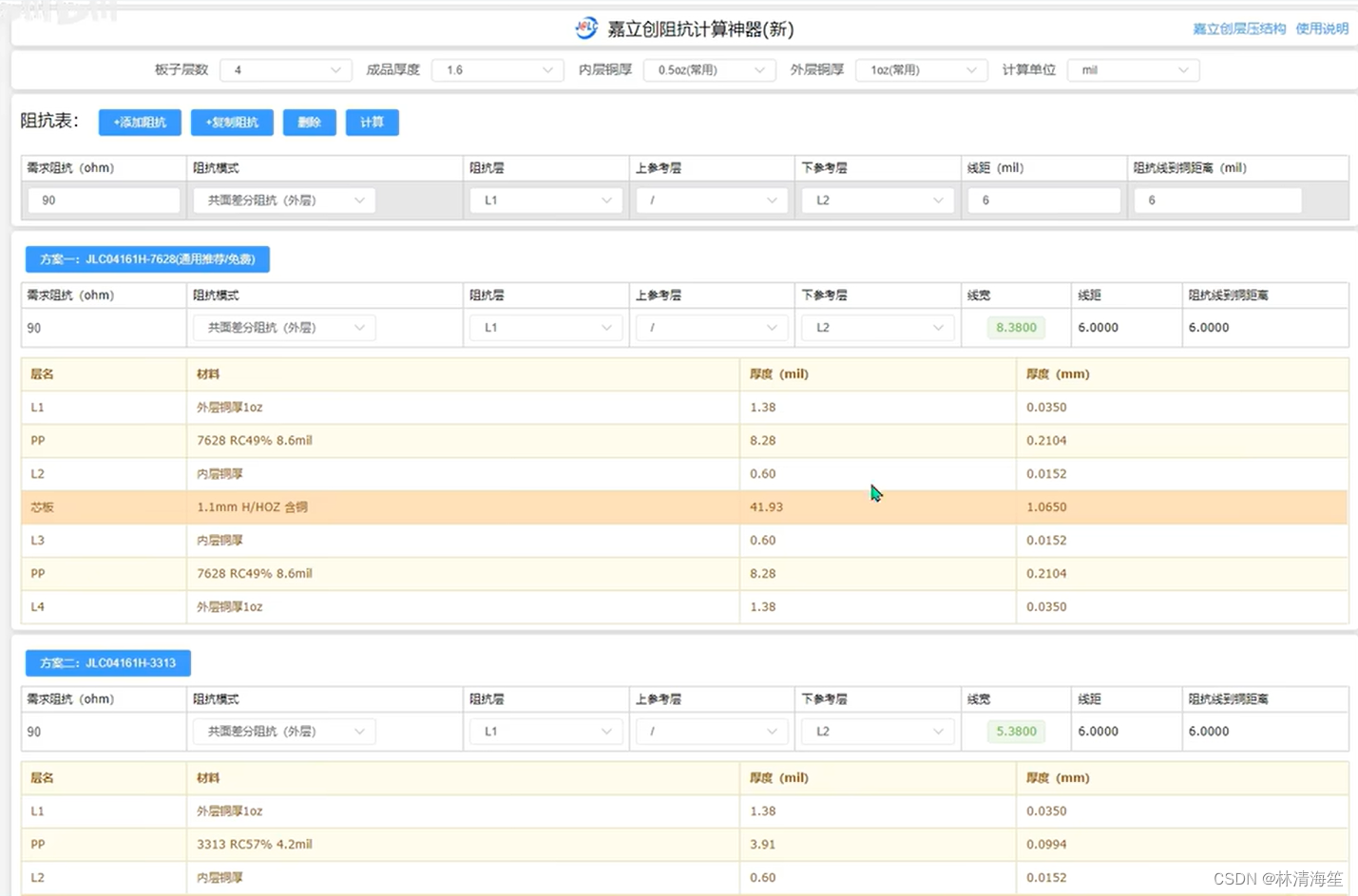

- 在立创官网选择产品服务,选择阻抗计算器

- 板子层数以4层板为例,板厚为1.6,铜厚按照默认参数,外层为1盎司,内层为0.5盎司。

- 假设需要控制的阻抗为90欧姆。

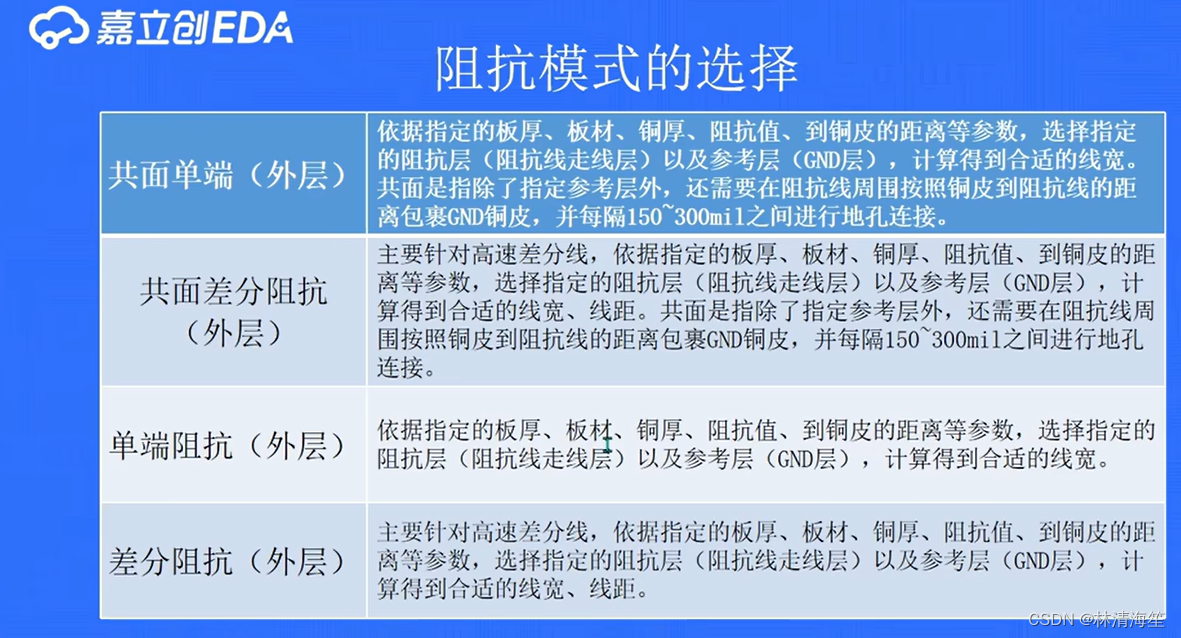

阻抗模式

-

指定阻抗层:控制阻抗走线的所在层

-

差分线是两线为一组,因此多了限距离的参数,

-

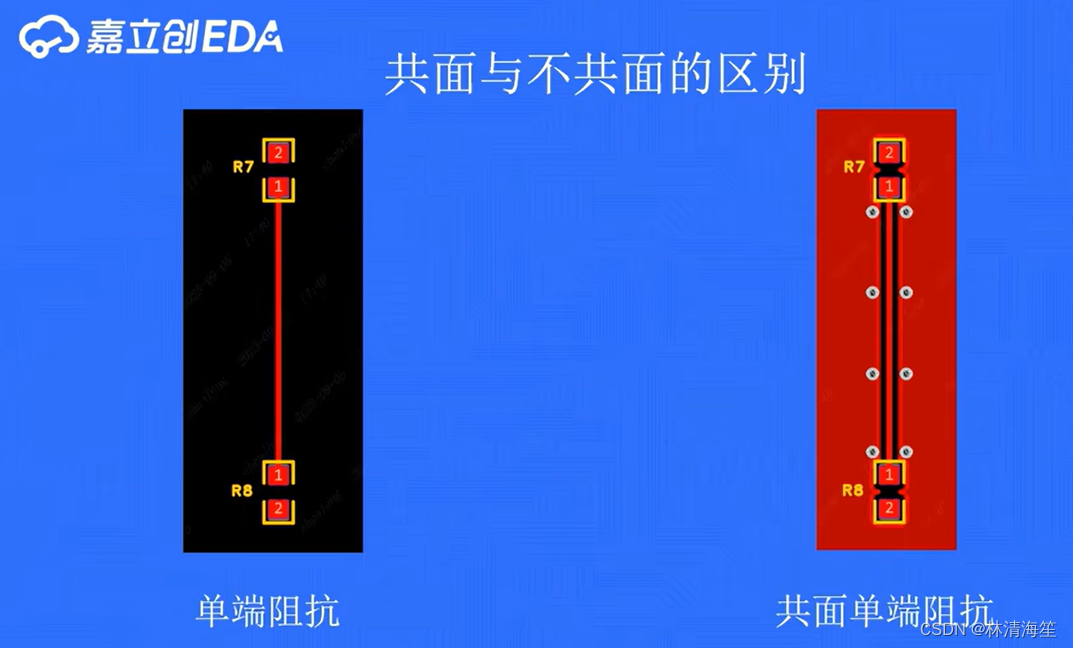

共面指的是在指定参考层外,还需要再阻抗线周围,按照铜皮到阻抗线的距离进行包裹GND铜皮,并且每隔150mil到300mil之间进行地孔连接。

-

共面阻抗的话,抗干扰能力会更好一点,但是需要考虑板子实际走线密度是否合适,

-

共面阻抗的话,抗干扰能力会更好一点,但是需要考虑板子实际走线密度是否合适。

-

像这里共面单端阻抗和普通的单端阻抗的显著区别是,共面单端阻抗有GND过孔,每隔150-300mil之间进行一个包裹,

-

阻抗模式选择差分阻抗,这里的阻抗层选择L1,也就是在顶层进行走线,在顶层是没有上参考层的,按照前面的层叠结构,选择第二层作为GND层,线距选择默认的8。后点击计算。线宽就计算出来了。

-

在PCB设计时,按照规定的线宽进行走线即可。如果线宽太大或太小,可以通过改变上述的参数进行调整。

-

但是这些参数不能随便修改,要考虑工艺的设计要求,像嘉立创的多层板,最小线宽或线距为3.5mil,一般都会流出余量保证合格率。所以采样嘉立创进行打板时,一般不建议小于6mil的线宽线距。

3.USB接口设计

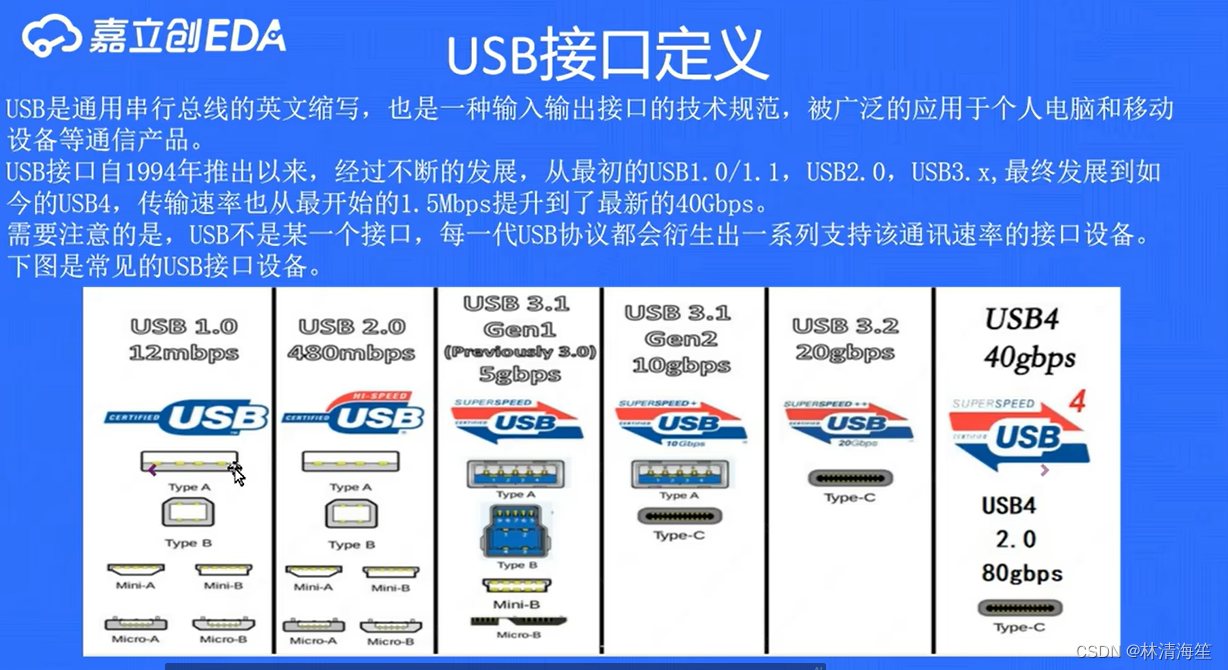

- 本次项目制作的USB拓展器,是支持USB3.1Gen1(USB3.0Hub)

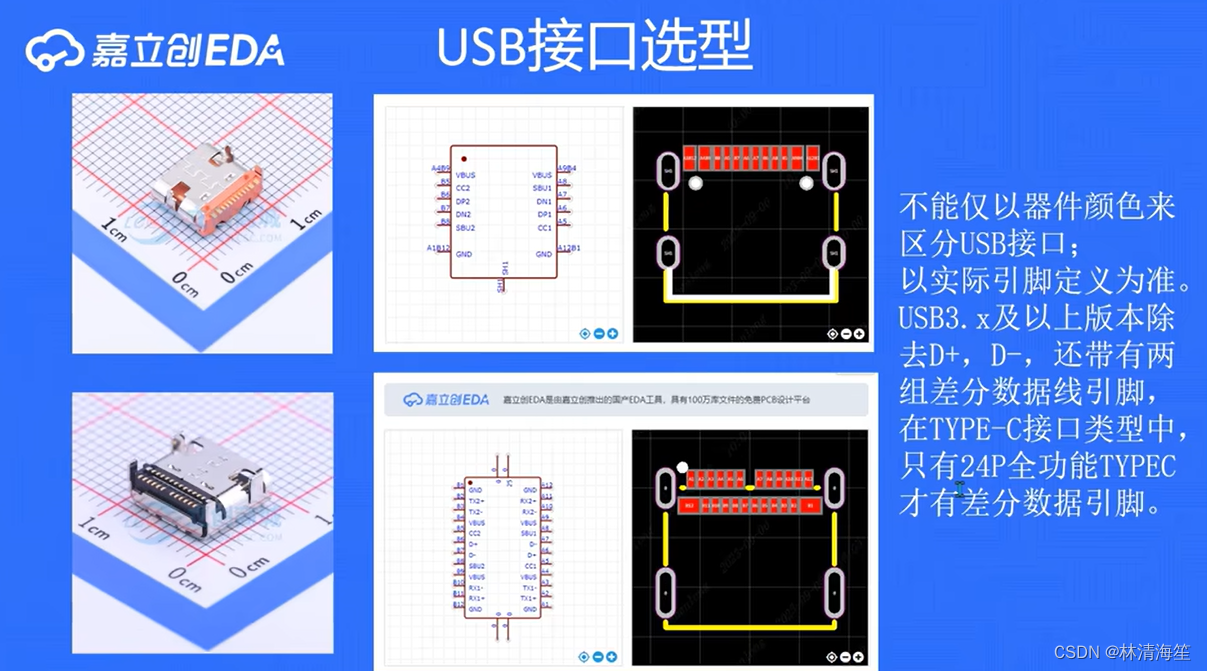

- 在进行USB选型时,不能仅依靠器件颜色来区分USB接口的版本,要以实际引脚定义为准。

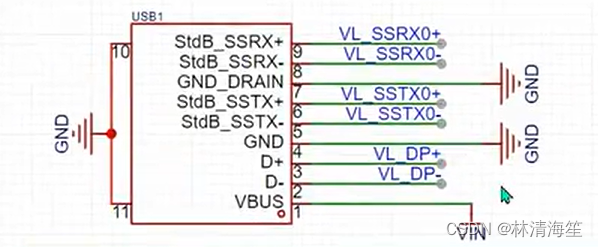

- USB3.0以上的版本,除去了D+和D-两条数据线,还带有两组差分信号线。在USB typeC的接口中,一般只有24片的全能typeC接口才有差分数据引脚。

- 对于USB-typeB来说,区分就会简单一些。3.0版本和2.0版本在外形上会增加一组数据接口进行数据传输,

VL812电路设计

1.主控芯片电路设计

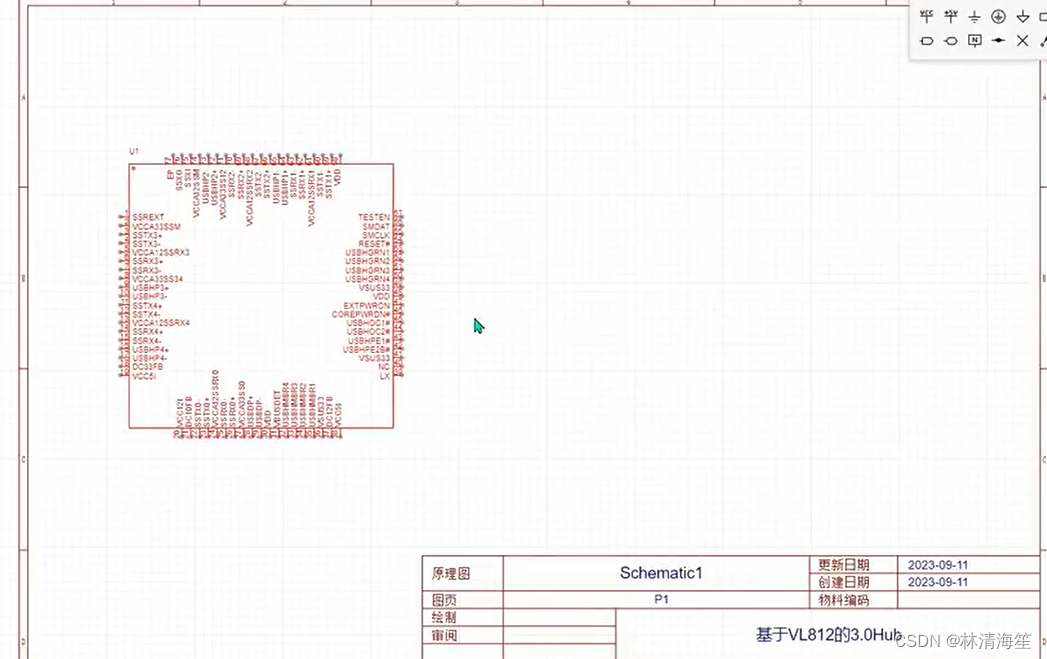

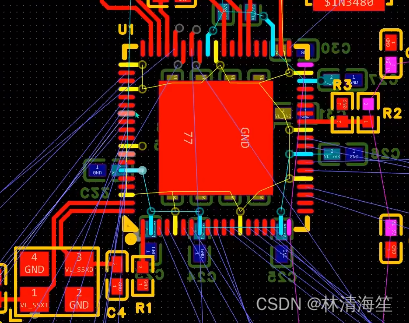

- 首先把主控芯片找出来,

- 接下来就是根据主控芯片的数据手册,对外围电路进行设计,点击主控,选择属性

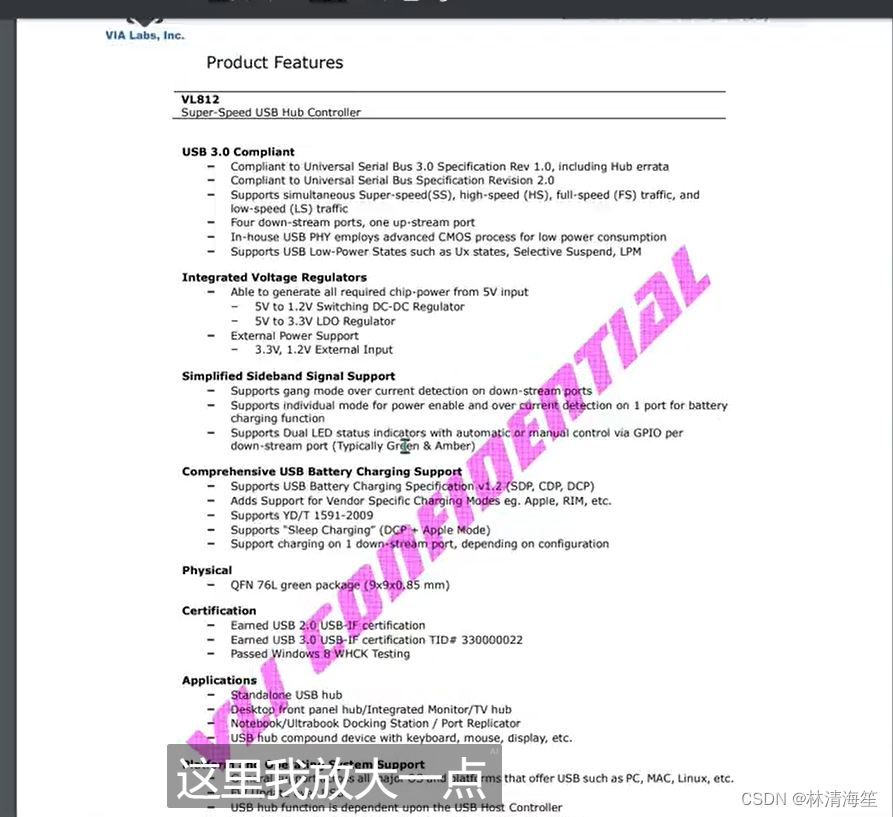

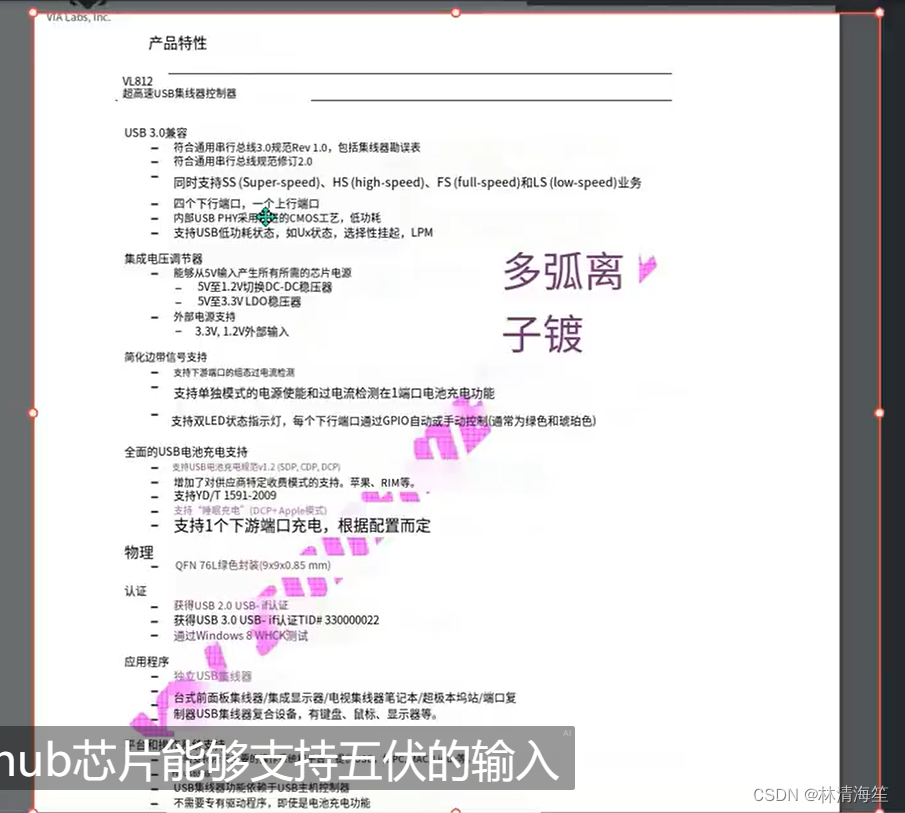

- 在数据手册中找到产品特点。看一款芯片的数据手册,首先应该看产品特点,因为这是对产品进行一个大致的描述,这样能够快速的了解产品的功能。

- VL812是一个符合3.0规范,同时兼容2.0总线。有四个下行端口,一个上行端口,也就是一拖四的3.0hub芯片能够支持5v输入,然后能够产生所有所需的芯片电源。且内部集成了电源转换芯片,也支持外部电源输入。

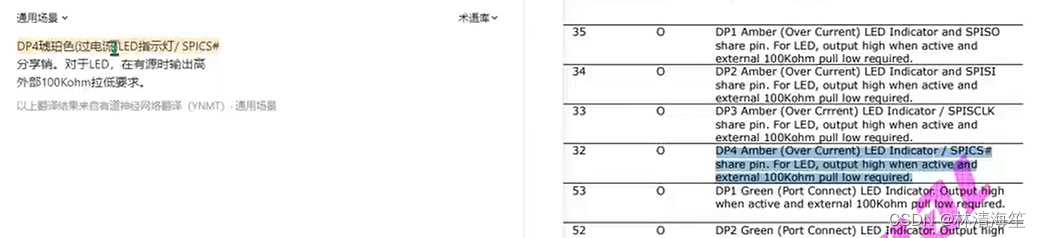

- 这里还有led指示灯用于指示下行端口,用于检测插入的功能的。

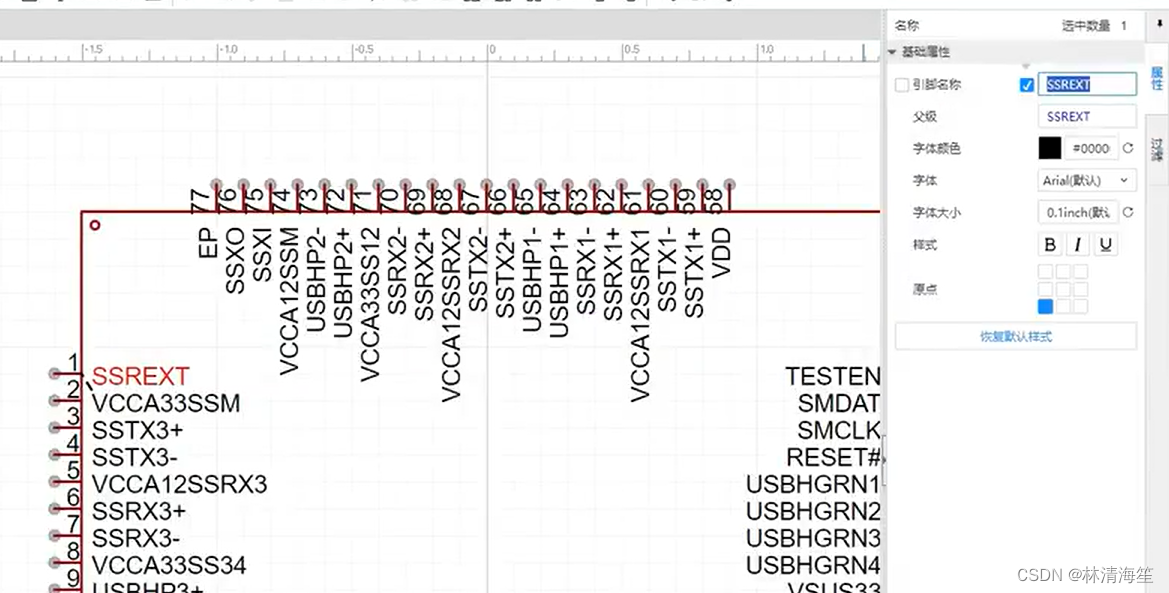

编辑芯片引脚颜色

- 在这里官方对不同功能的芯片引脚进行了颜色分类

- 点击芯片,选择右键选择编辑符号,点击是,进入符号编辑界面,对照数据手册进行颜色分类

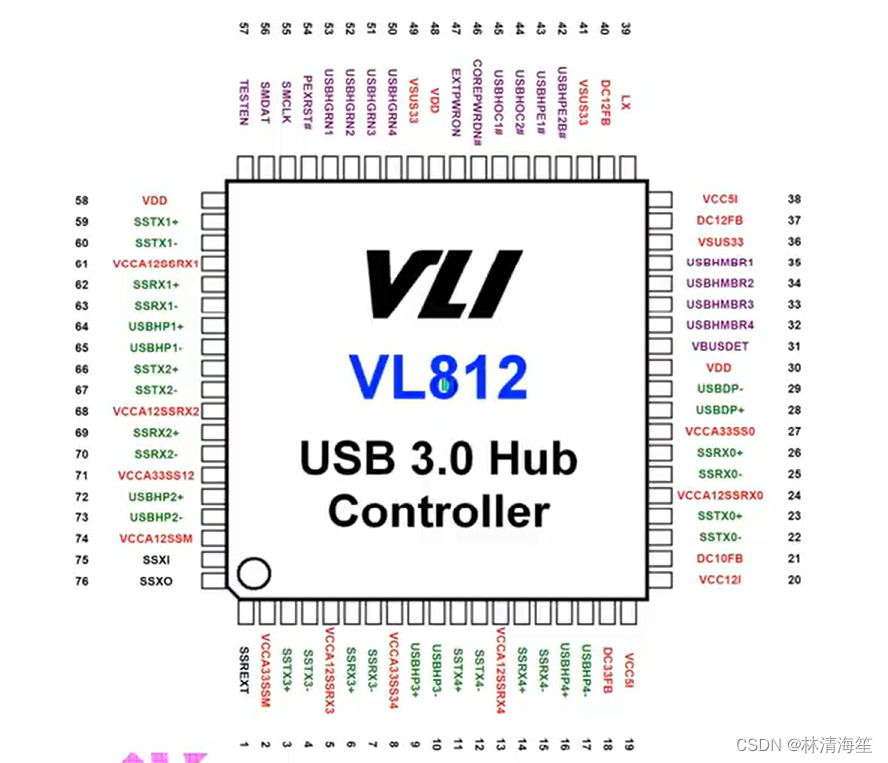

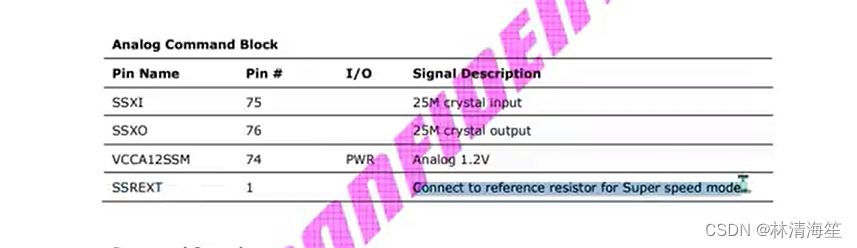

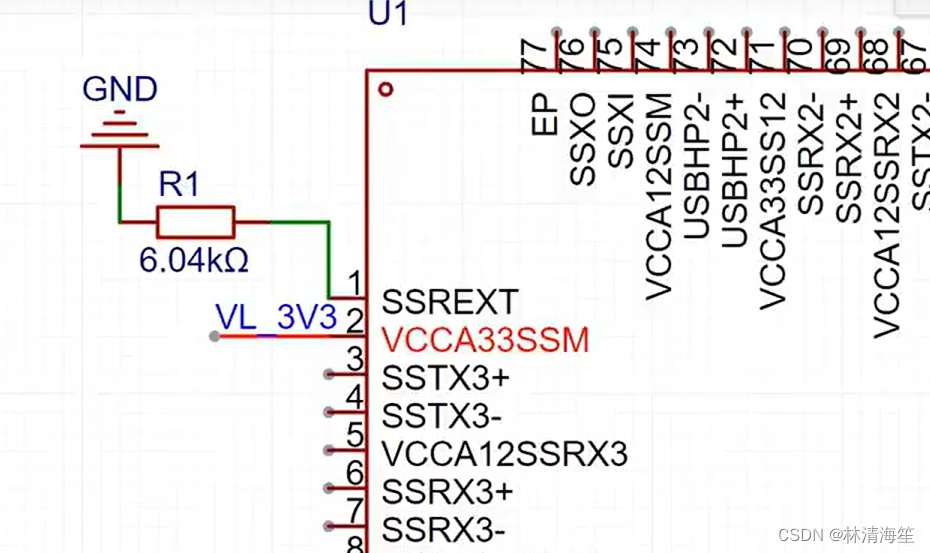

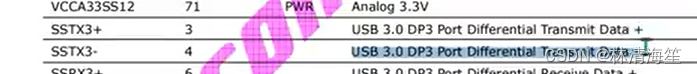

- 然后在芯片手册中找到引脚的定义,在这个引脚1的SSREXT的定义是连接到参考电阻的超速度模式,在这里询问了官方,按照官方案例,一般直接连接6.04k电阻到地即可。

- 由于设计比较紧凑,贴片电阻和电容一般选择0402封装的,会更好走线。

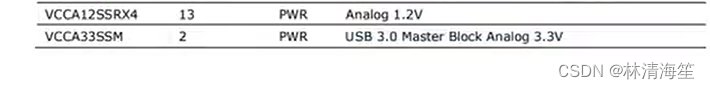

引脚2:VCCA33SM,定义为:USB3.0主控块模拟3.3v电源,由于本次设计的hub是没有其余主控和干扰源的,可以不用区分数字地和模拟地,直接使用即可。然后对引脚引出网络标签。

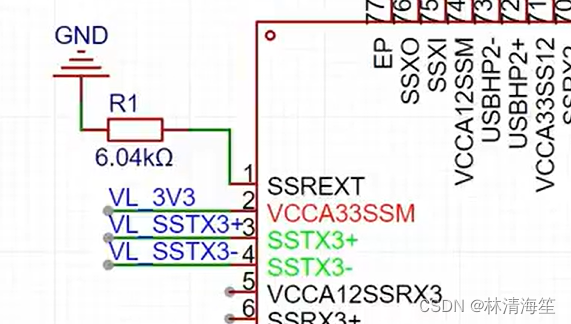

引脚3:SSTX3+ 。USB3.0端口3差分传输数据+

引脚4:SSTX3- 。与引脚3是一组差分对

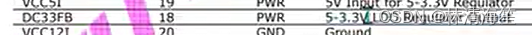

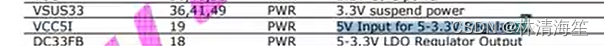

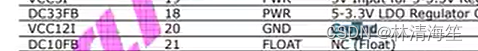

引脚18:DC33FB。5v转3.3v的LDO稳压器输出,他内部是集成了5v转3.3v稳压器的。所以这里是直接输出3.3v,像上面的3v3应该就是从这里引出来的。

引脚19:VCC5I。5v转3.3v稳压器的输入,即5v的输入。

引脚20:VCC12I。GND引脚

引脚21:DC10FB。NC浮空,这里不用管,打上非连接标识。

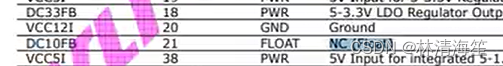

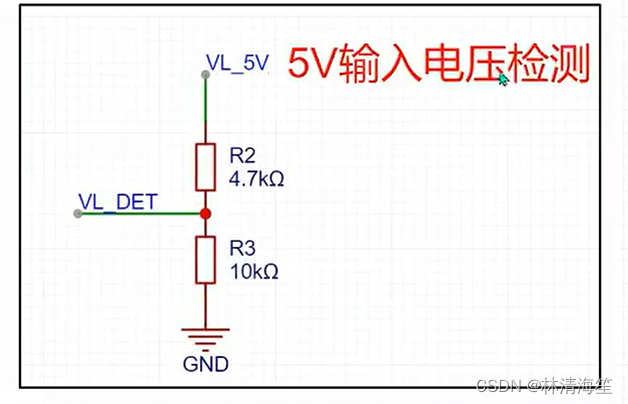

引脚31:VBUSDET 。5v的USB VBus存在检测,即5v的电源存在检测。根据官方的实例,当引脚为高电平的时候,存在5v输入,引脚为低电平时,就不存在5v的输入。

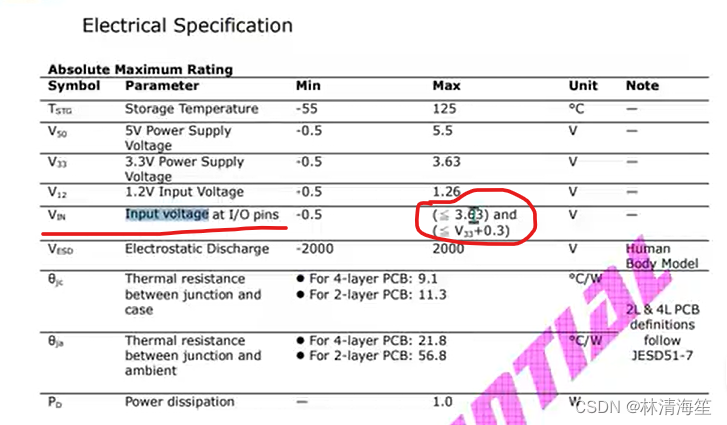

所以这里需要连接其他电路进行检测,将其进行拉高。在芯片手册中找到电气特性,这里有说输入的电平不能超过3.6v,所以这里不能直接将其拉到5v,而是要将其拉到3.3v左右,需要使用两颗电阻进行分压。然后使其稳定在3.3左右。

引脚32:USBNMBR4。端口4的过电流检测,同时也是SPI片选引脚的共享引脚。这里用不到过电流检测,同时芯片的一个SPI引脚是用来连接外部flash,进行固件升级的。VL812芯片出厂时自带固件的,如果不需要固件升级,这里可以直接进行一个非连接。

引脚36:VSUS33。这里是3.3v挂起电源,这是为设备进行低功耗的时候使用的,当设备没有进行数据传输时,挂起设备降低功耗,这里我们直接将其连接到3.3v

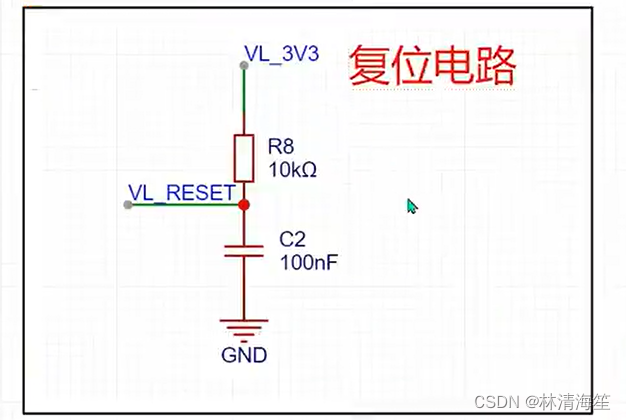

引脚54:RESET。复位引脚,高电平复位。一般芯片有上电时序的要求,

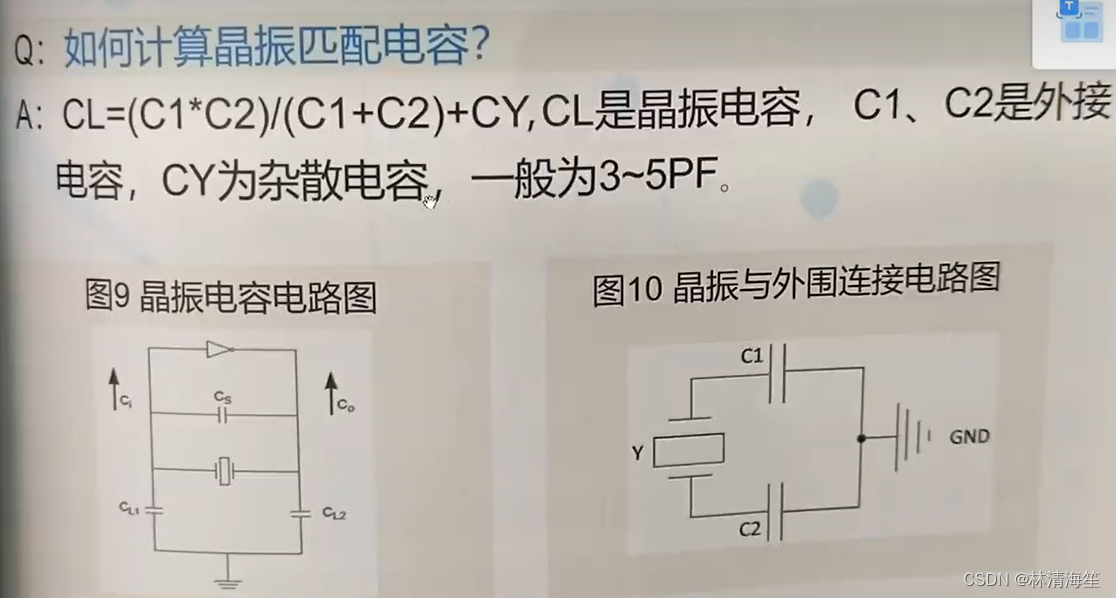

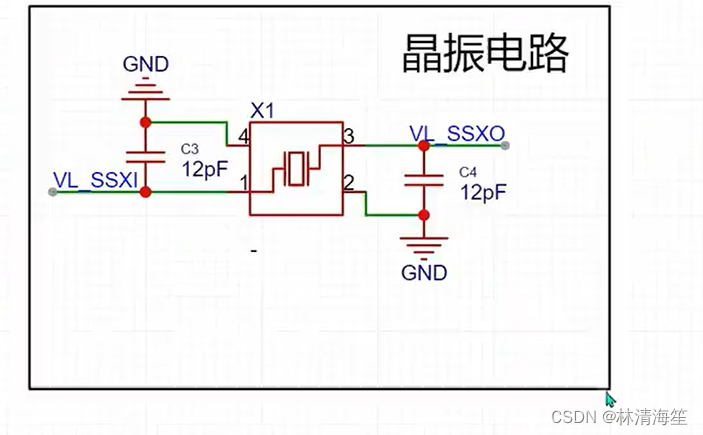

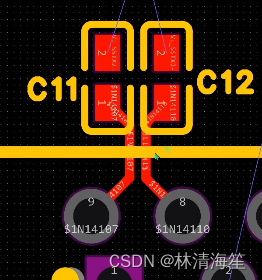

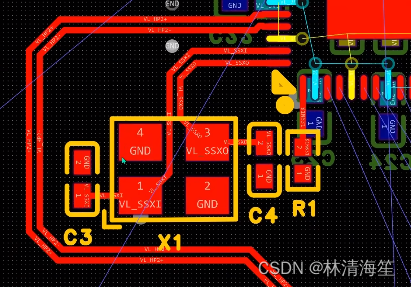

引脚75:SSXI。晶振25MHz,选用3325封装的,体积更小,内部晶振电容为10pF。

然后计算外部电容,根据下面的计算公式。根据计算,得到外部电容为12pF左右。

2.外设电路设计

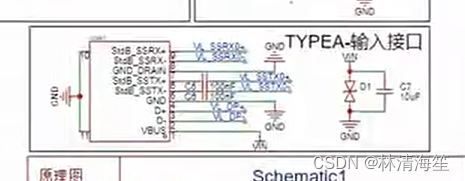

供电USB接口

- 供电部分,hub可以选择一个接口进行供电,插电脑的端口只负责通信,这样最为安全。另一种就是使用电脑接口一边供电一边通信,这样只有一条线方便使用。

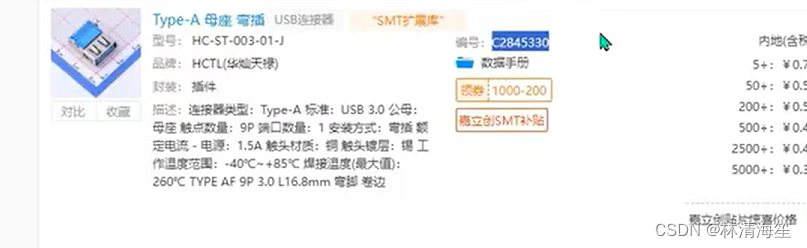

- 在立创商城选择连接器/开关,选择USB连接器,标准选择USB3.0,输入接口的母座选择typeB的母座,布局走线较方便

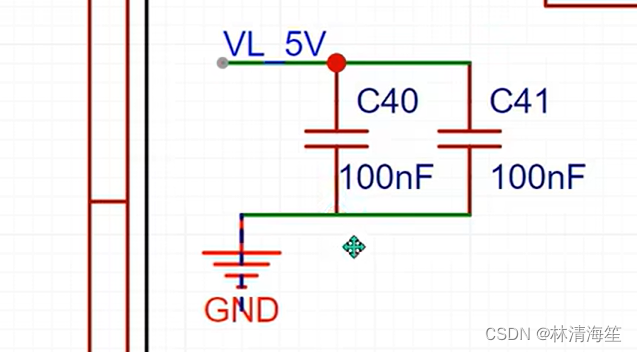

- 在3.0接口处,一般会在TX,也就是发送信号的线中,串联一个100nF的电容,来减少低频干扰,提升信号质量

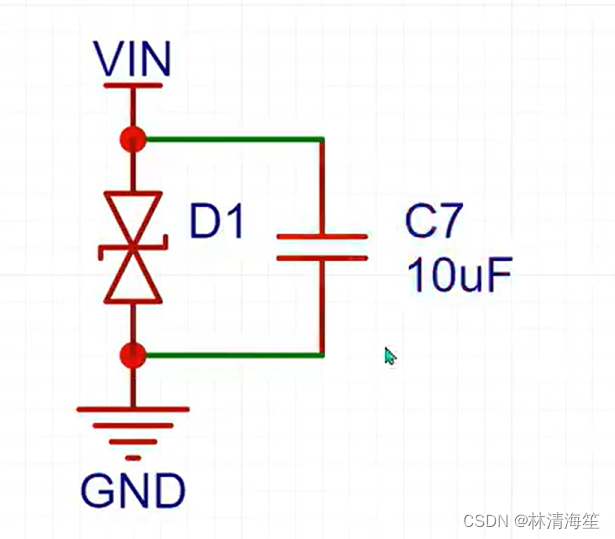

- 然后再输入电源部分加入10uF的电容进行滤波。

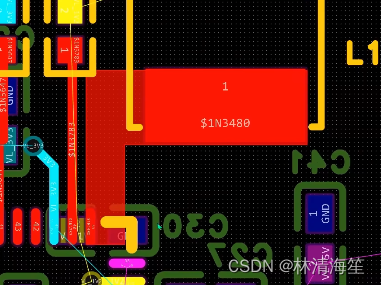

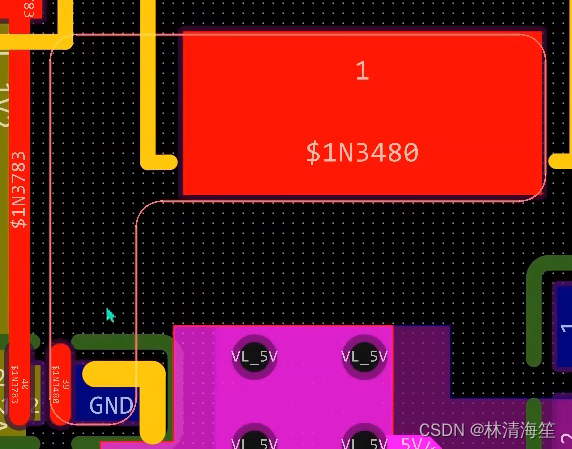

- 保险起见,还需放置一个TVS瞬态抑制二极管,去放置乱冗和静电。这是一个接口,人手碰到可能会有静电。在选型的时候,反向截止电压要选择大于或等于5v,这样接口在正常工作时是5v的状态,TVS是不工作的,它的漏电流小,

输出接口

- 选择typeA的母座,

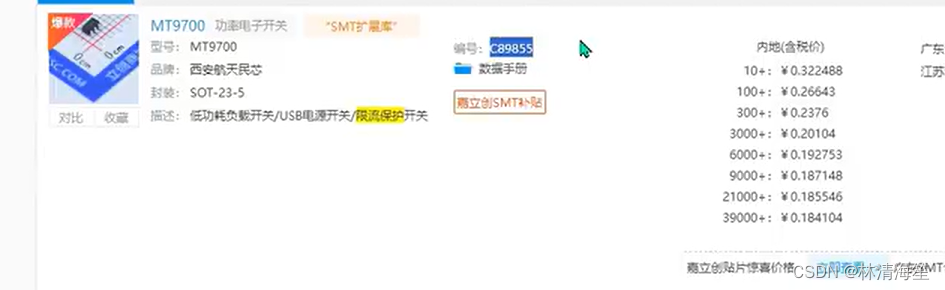

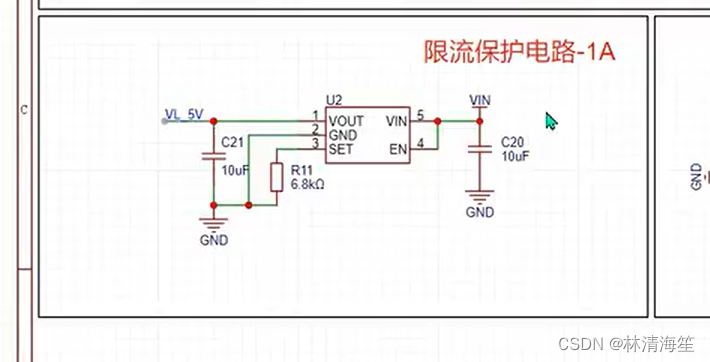

限流保护

- 现在采用电脑接口进行供电通行,一般笔记本电脑的输出电流在1A左右,如果4个输出接口接的负载较大,很可能会损坏电脑接口。

- 在立创商城搜索限流保护芯片,

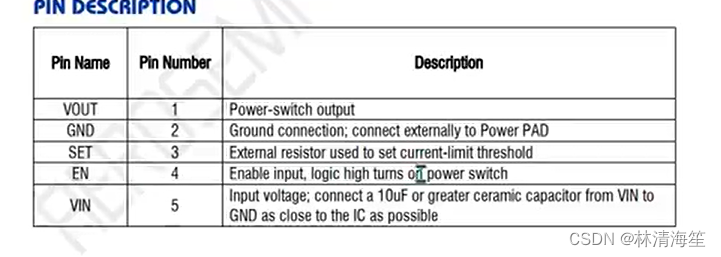

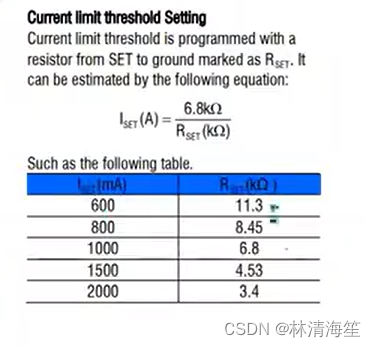

- SET:设置保护电流

- EN:高电平打开开关,高电平使能

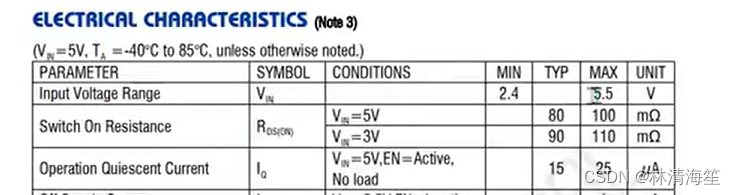

- 输入电压范围是在2.4-5.5v

- 设置引脚根据所需电流进行电阻选取。这里选择限流为1A,所以需要串联一个6.8k欧电阻。

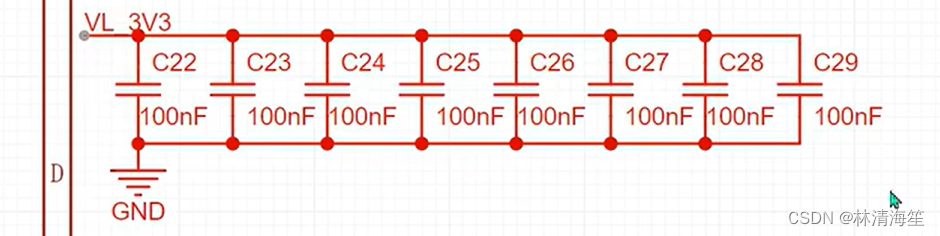

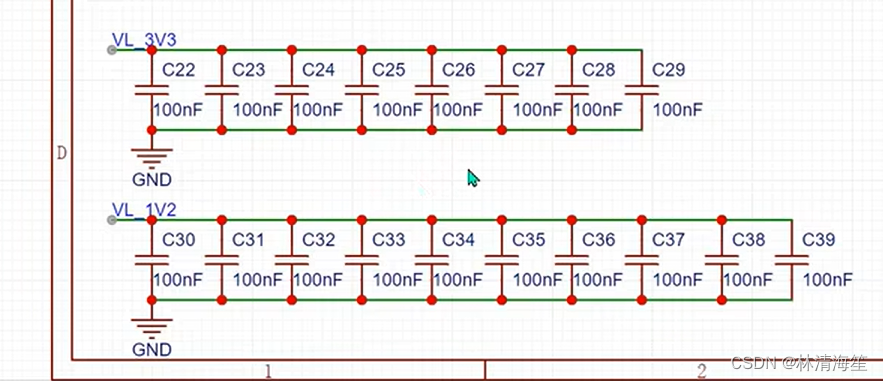

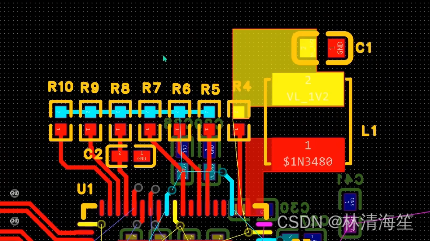

滤波电容

- 芯片很多引脚都需要1.2v或3.3v的,但是在这些引脚处,却一个电容都没有,这种情况会带来电源的不稳定。所以每个电源引脚都就近放一个100nF的滤波电容,保证电源干净。

- 在这个芯片中有8个3.3v的引脚,因此需要8个100nF的滤波电容。

- 在这个芯片中有10个1.2v电源引脚。

- 两个5v电源引脚

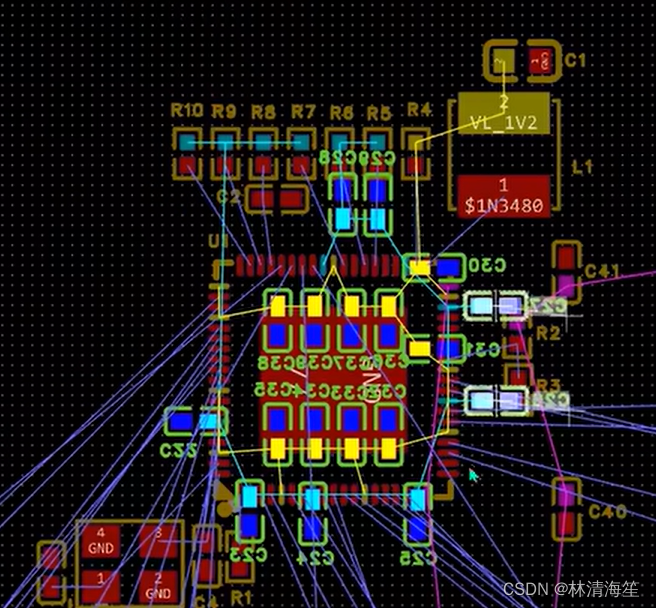

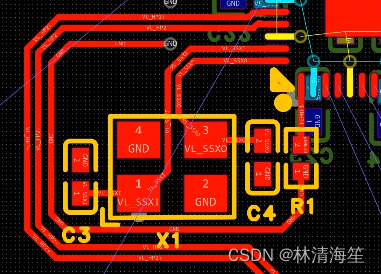

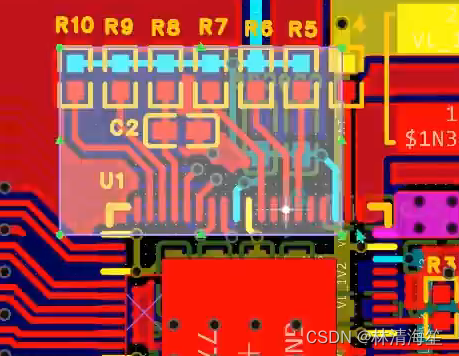

- 由于在顶层用于走高速信号线的,尽量不要去干扰,所以想要就近摆放,这些电容要放置在背面

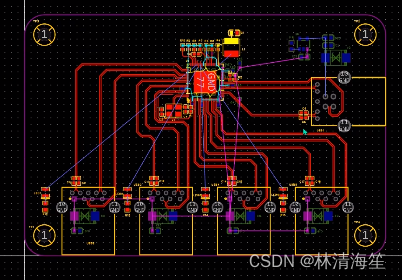

VL812的PCB设计

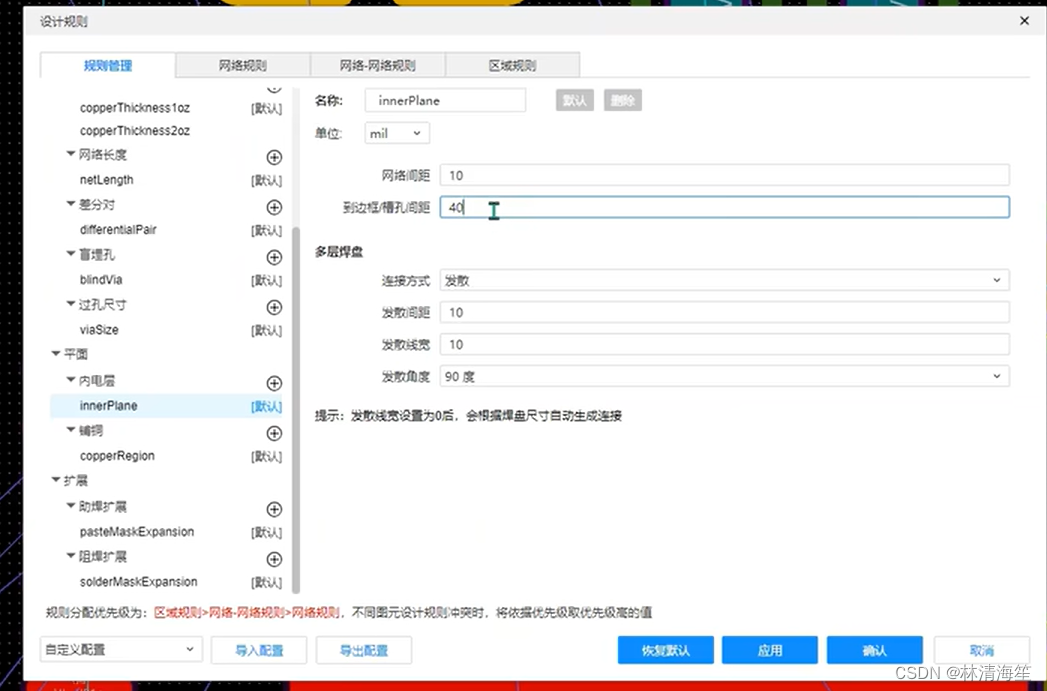

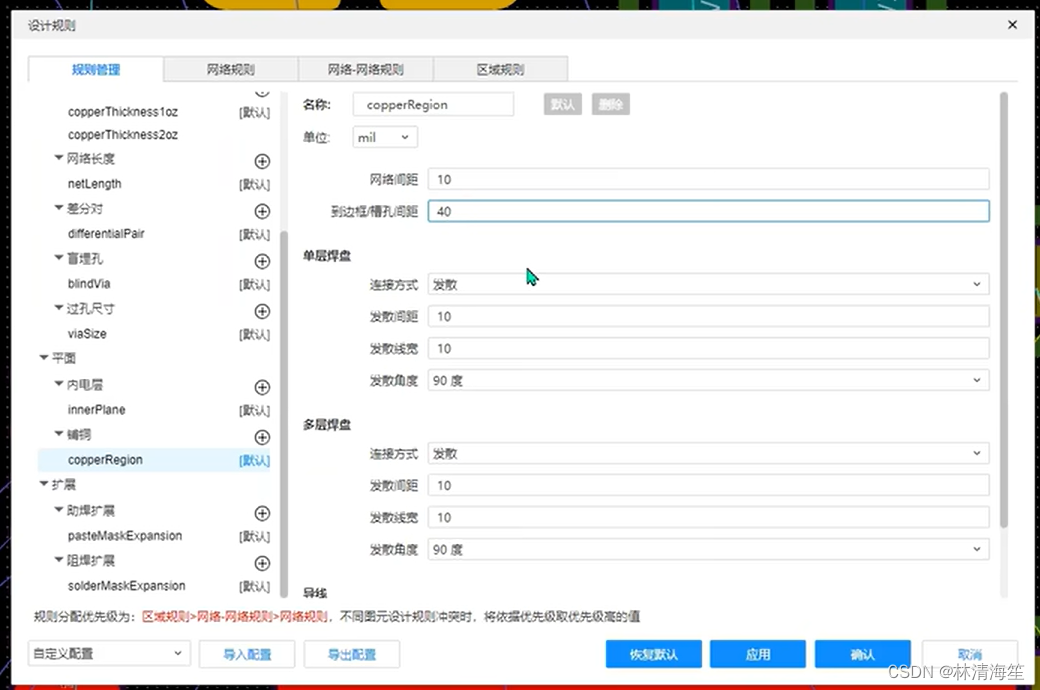

1.设计规则设置

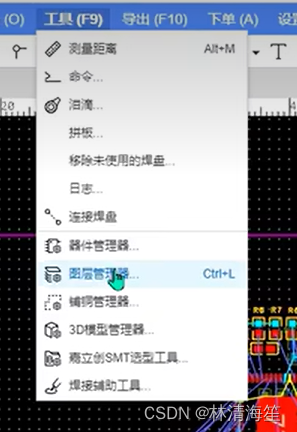

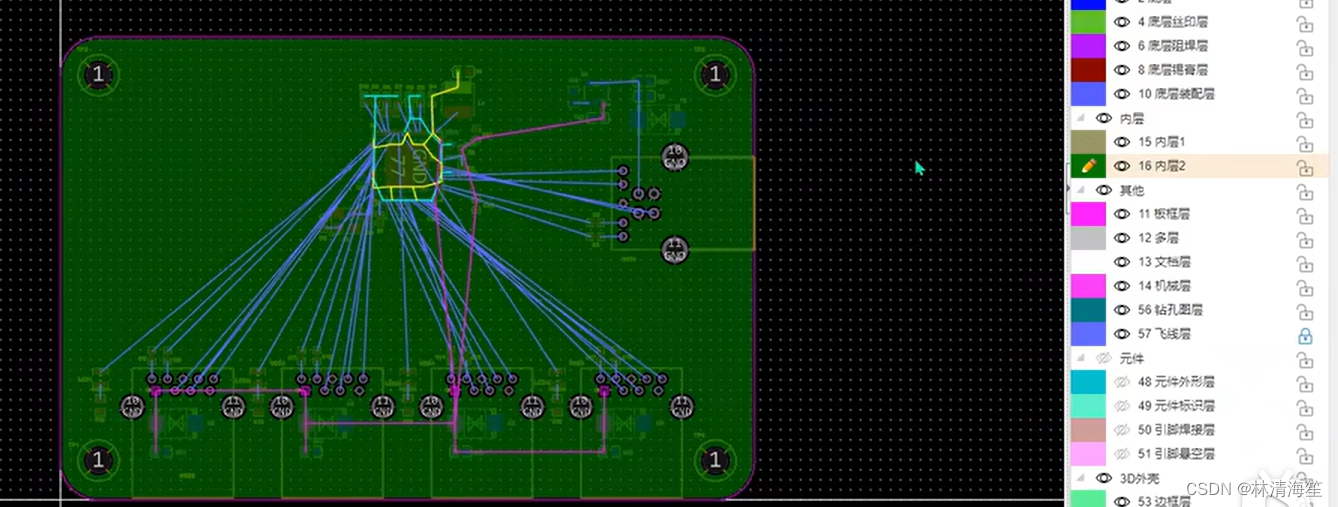

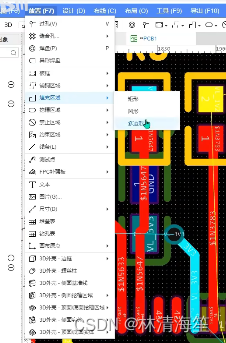

更改板子层数

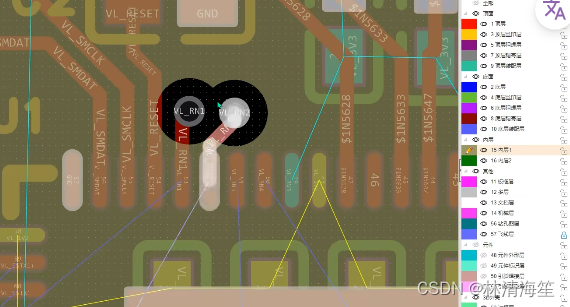

-

首先更改板子层数,选择图层管理器,选择4层板

-

这里内层类型,内电层为就是默认一整个层都是铜皮,不能用来走线,只能用来作为铜皮的分割。信号层就是走线层。一般情况下两个铜层都会设置为内电层,一个为GND层,一个为电源层。如果走线较多情况下,也可以根据实际情况进行设置。

-

此时就是四层板了,

-

USB3.0的传输速度最高能达到5Gps,对于这种高速传输信号线,一般都会进行阻抗设置。

-

如果不知道是多少,可以在百度查找,一般都是控制在90欧姆

-

-

然后再嘉立创的阻抗计算神器中,阻抗值设置为90。

-

USB3.0的高速传输线是以差分的形式,要选择差分阻抗。

-

然后是共面的选择,现在整个顶面没有其他多余的器件,非常空旷,对于共面阻抗的要求,是在传输线上两端加上过孔,然后进行包地处理。顶层的地平面是比较完整的,可以满足要求,所以阻抗模式要选择共面阻抗,所以在阻抗模式中选择共面差分阻抗。阻抗层,也就是走线层选择L1顶层,下参考层选择L2内层1也就是GND层。线距和阻抗线到铜的距离保持默认。

-

但此时发现如果使用免费的板材结构,线宽是10mil,还是太大了,这里将线距改为6mil,现在线宽变为了8.8mil。一般都会四舍五入一下,也就是9mi,还是较大。

-

再减小阻抗线到距离为6mil,计算得到8.3mil,也就是8mil。此时线距和阻抗线到铜皮距离也已经到极限了,再小可能生产就会有问题了。后续如果发现线宽还是太宽了,可以选择下面的板材进行生产。

-

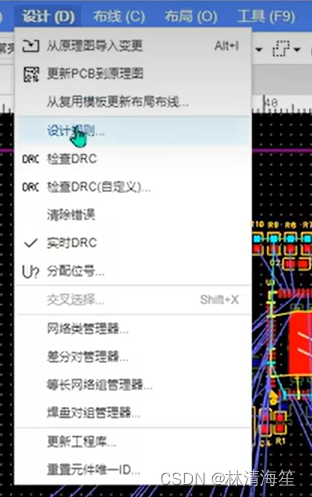

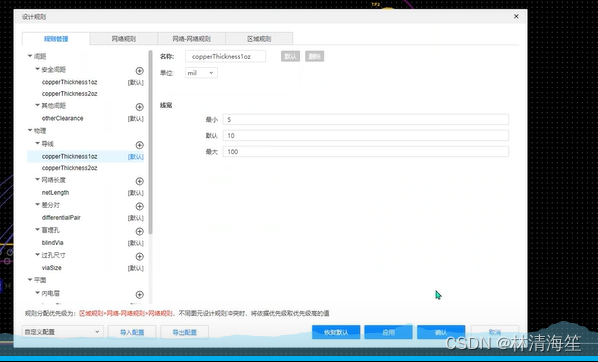

确认好线宽后,回到嘉立创,点击设计规则,将单位改为mil。

-

首先是安全间距,导线到导线的距离,我们可以设置的线距为6mil。因为我们刚才设置的线距是6mil,所以尽量保持同步,如果不等于6mil,还可以进行DRC报错,方便检查。其余的暂时保持默认,不用改。

-

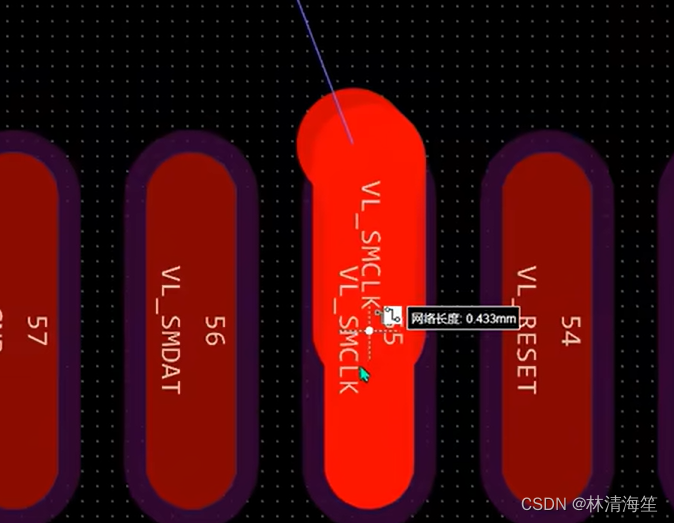

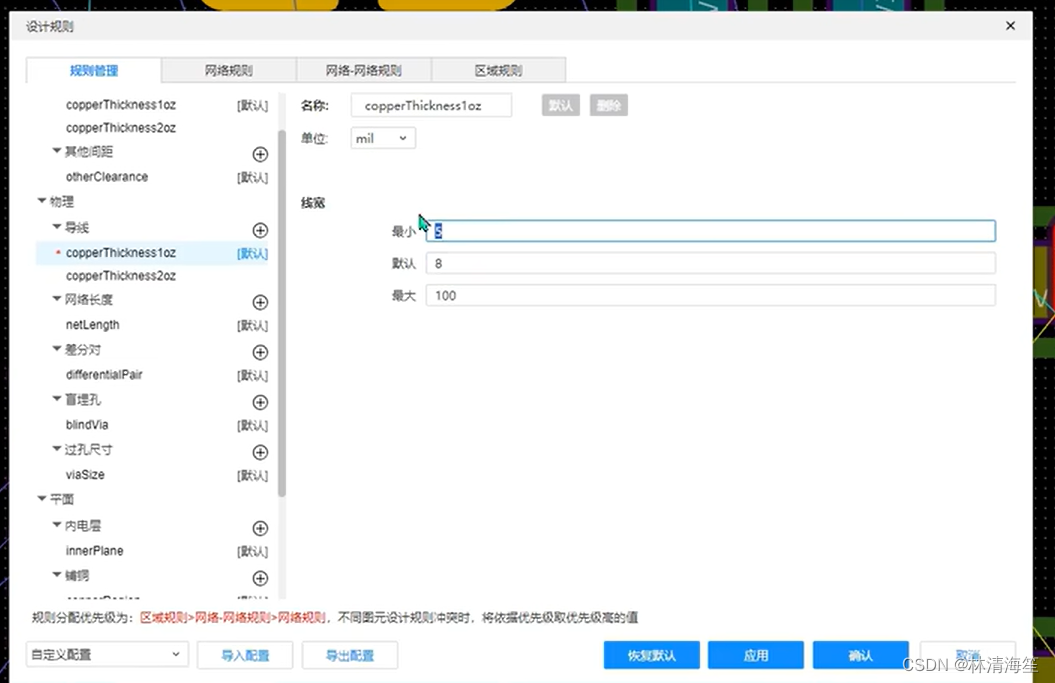

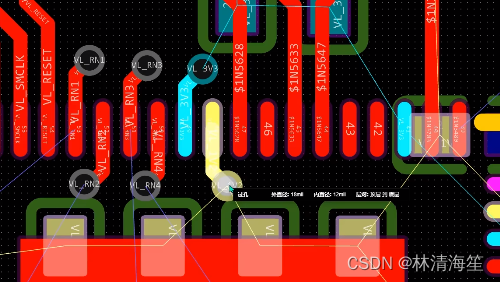

接下来是导线,这里导线默认是10mil,我们要控制阻抗的差分线,这里的导线线宽可以和计算出来的线宽不用保持一致,导线线宽一般和芯片的引脚线宽等宽。我们首先来看是否符合芯片焊盘大小

此时10mil线宽是比焊盘粗一点的,我们按住TAB键,将其修改为8mil,可以看到这个焊盘的宽度应该就是8mil了

-

所以我们回到设计规则,将线宽也修改为8mil

-

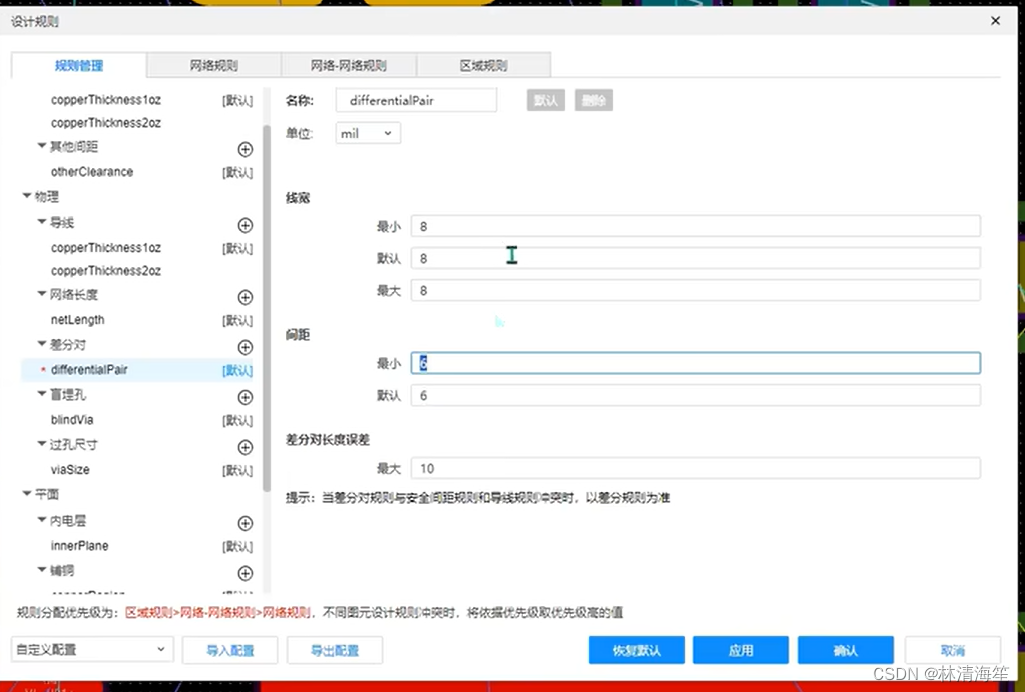

差分对导线是需要进行阻抗控制的导线,所以这里需要严格按照计算出来的数据进行走线。

-

线宽我们设置为8mil,线距为6mil,是之前阻抗计算神器中计算出来的间距。

-

差分对长度误差保持默认,在实际走线中肯定是越小越好。

-

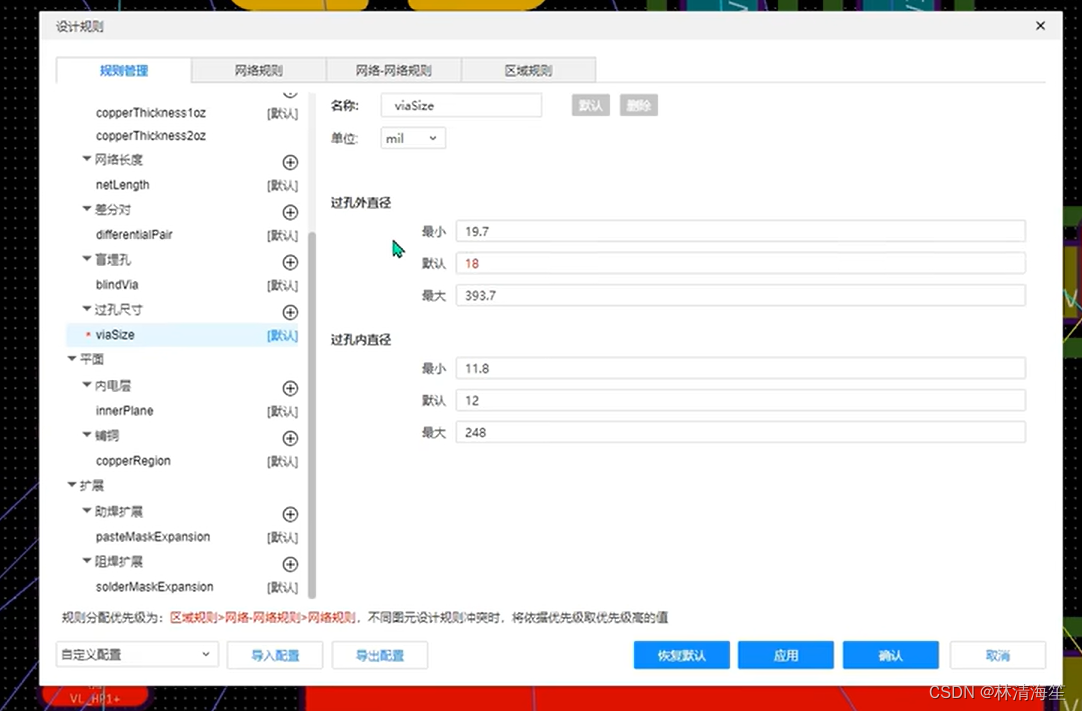

接下来是过孔尺寸,默认是24和12的大小。嘉立创打板最小内径为0.3mm,也就是12mil,如果改小了就需要付费了;外径最小为0.4mm,也就是16mil。这里我们将其修改为18mil。最小也改成18mil

-

接着是平面的内电层,在这里主要设置的是内电层到板框的距离。内电层通常作为参考层,为了防止外界干扰,一般内缩为40mil。

-

接着是铺铜,同样内缩40mil,防止外界干扰。由于整个板子都没有大电流器件,所以这里的铺铜可以采用默认的发散或10字连接即可。

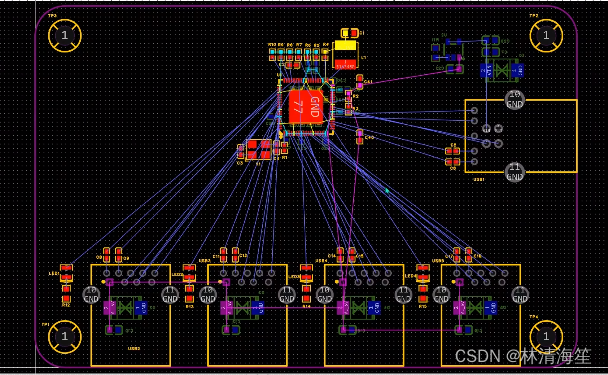

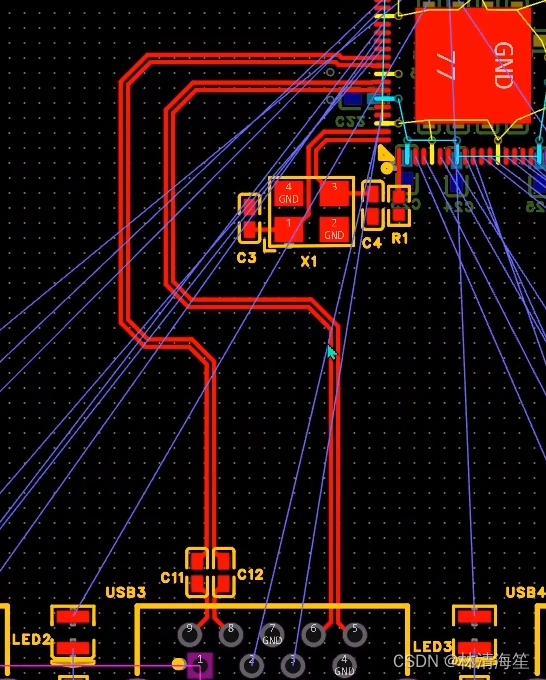

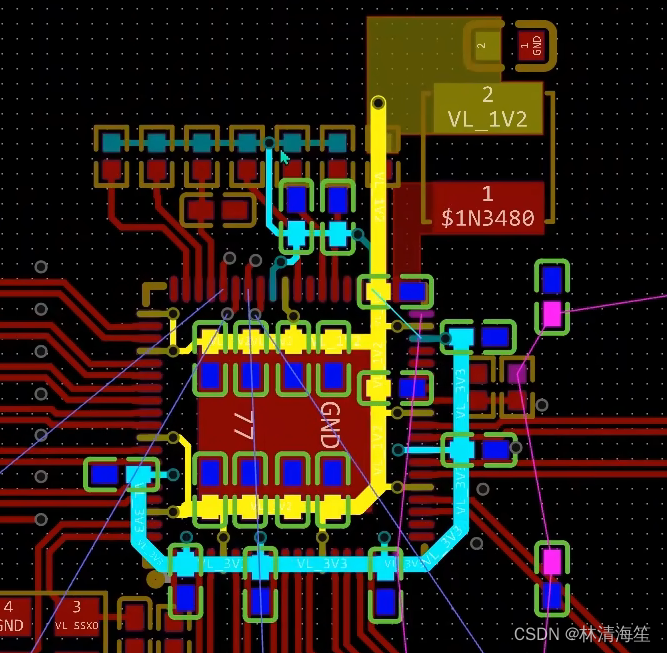

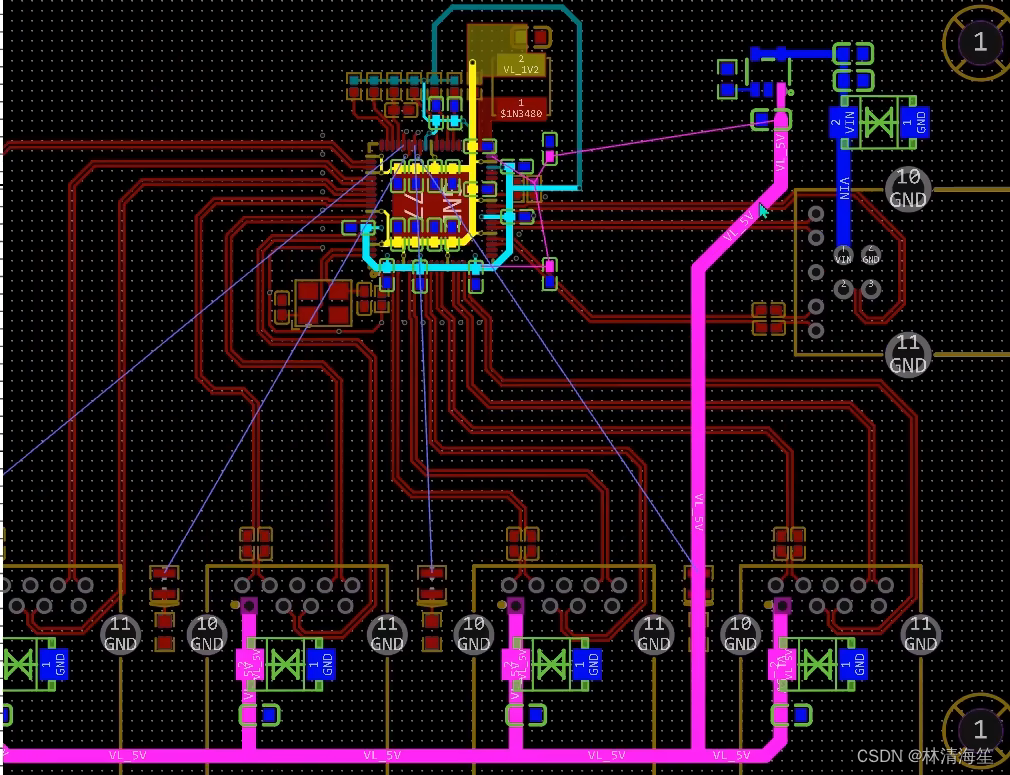

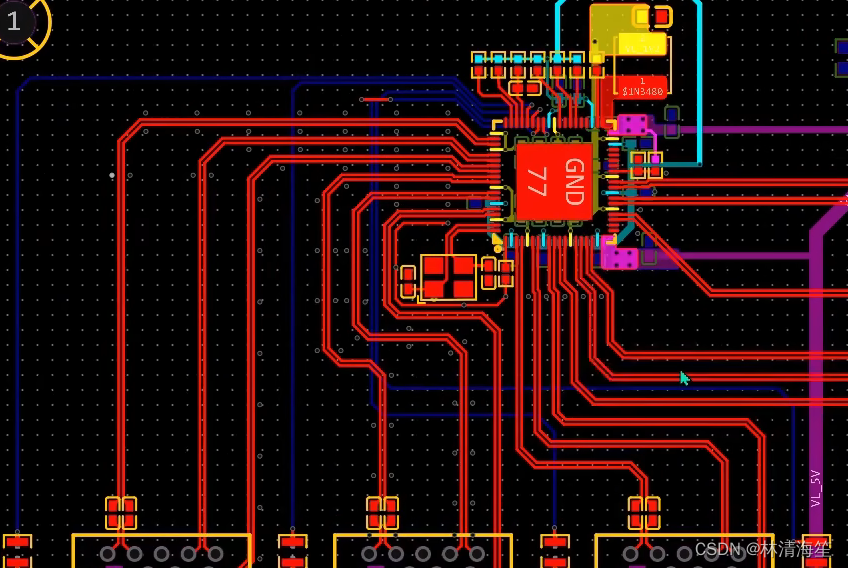

2.PCB走线布局

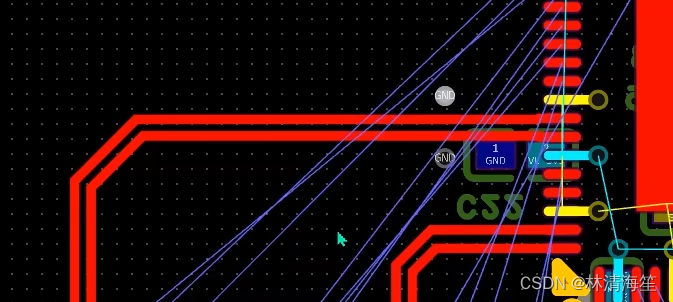

电源线及杂线的上出

- 目前高速信号线走线还是比较顺畅的,但是在芯片周围还有很多杂线和电源线,这里我们就先就近将杂线和电源线进行连接。如果一开始就走高速信号线的话,那么后续的有些杂线或者电源线可能就会没有位置引出去了。

-

- 首先是芯片顶部,有些上拉电阻的线需要连接到芯片的引脚处,同时这一块是没有高速传输信号线的。

- 如果连线较远且非重要线,先不进行连接,不要干扰高速信号线的走线。打上过孔进行上戳。

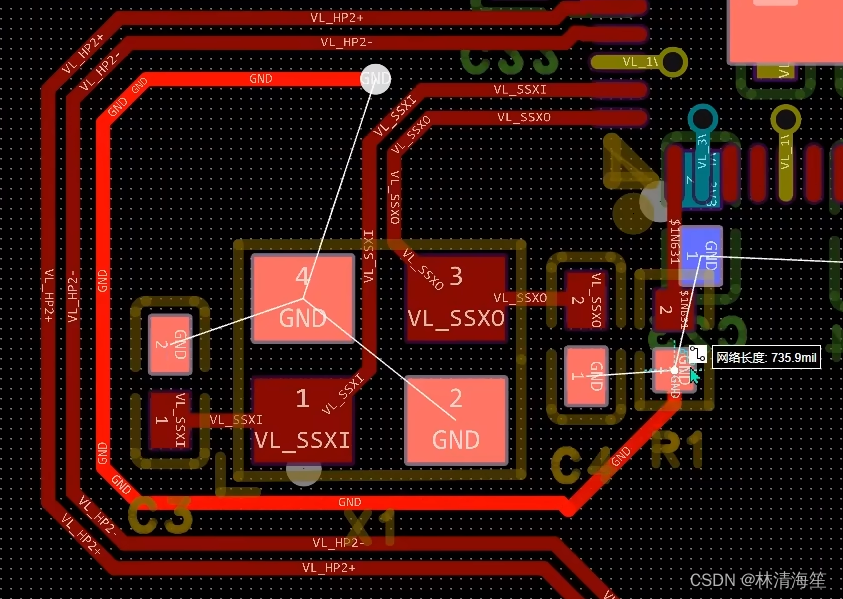

- 但是这两个过孔靠太近了,间距太小了,虽然没有DRC报错,但是在这个间距下面是连一根线也走不了了。我们可以打开图层的内层,重新铺铜看下。可以看到内层被这两个过孔分割走了。所以在打过孔的时候,最好要保持一定的余量,位置错开。

- 用同样方式,统一对电源线进行上出。最好都是朝芯片内部进行上出,因为芯片外部是要从其他高速信号线的。有了这些过孔的存在可能会干扰信号线。

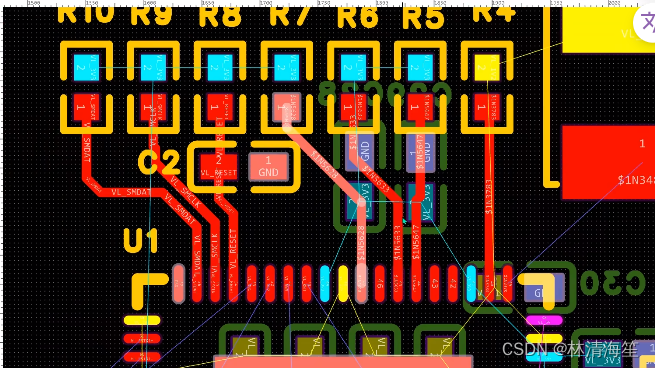

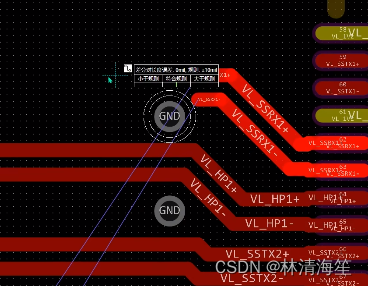

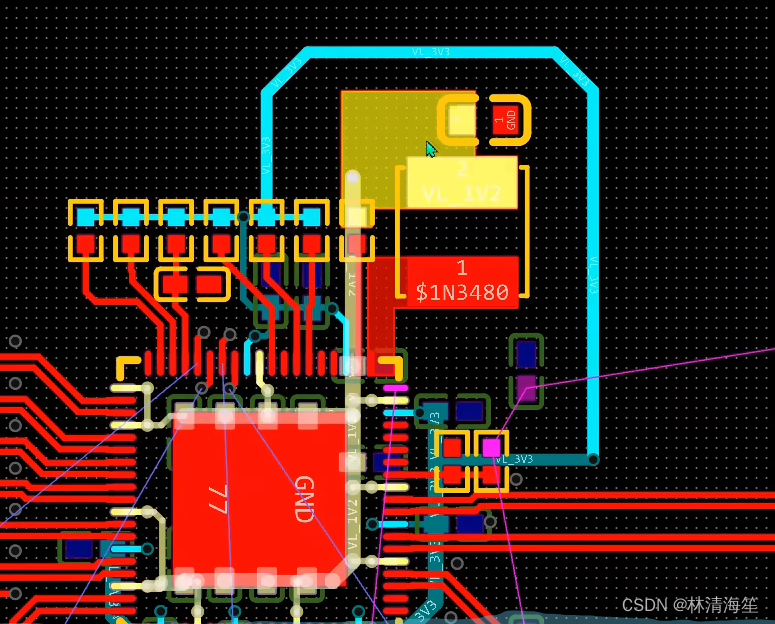

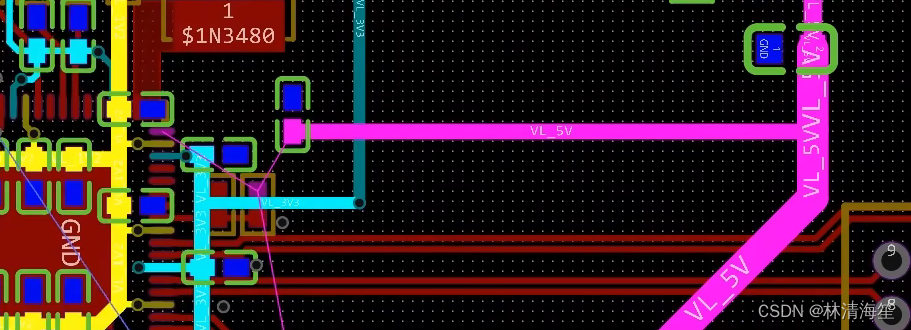

高速传输信号线(差分等长布线)

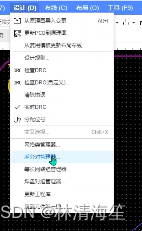

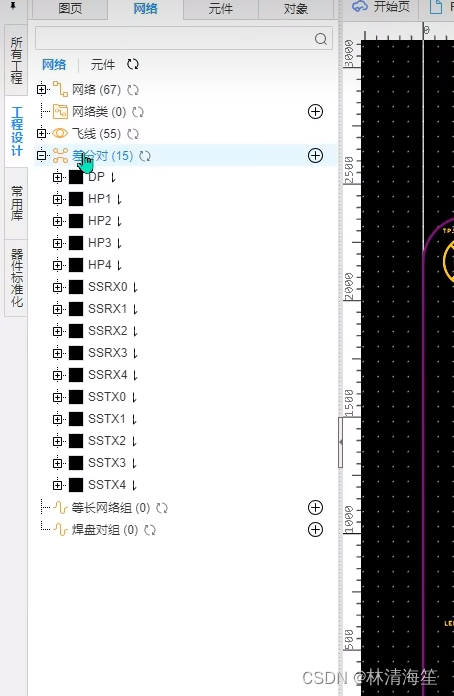

- 接下来就可以走高速传输信号线了。USB3.0的线都是差分数据线,这里可以点击设计,选择差分对管理器。

- 在这里对差分对进行命名,从左到右依次对不同信号线进行构建差分对。

- 创建完成后,点击网络,可以看到有15组差分对。

- 走线的顺序,一般来说都从有阻挡的一侧开始走线。还有走线的优先级,只有SSTX和SSRX是高速传输信号线,因此要优先考虑这两种线的走线顺畅。

- 选择布线,选择差分对布线,走线中要保持水平

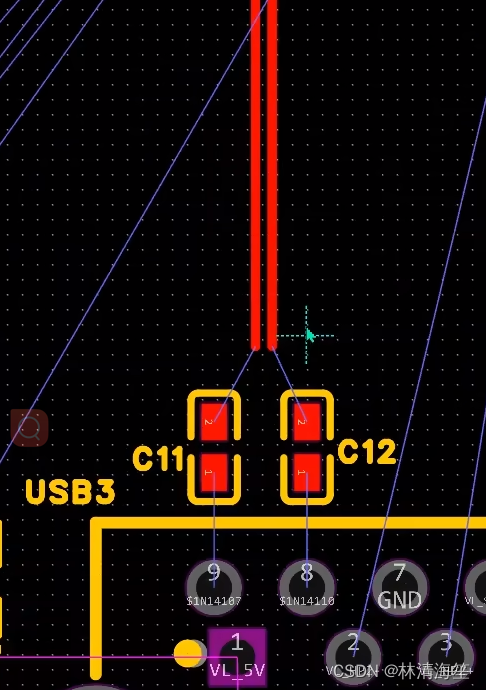

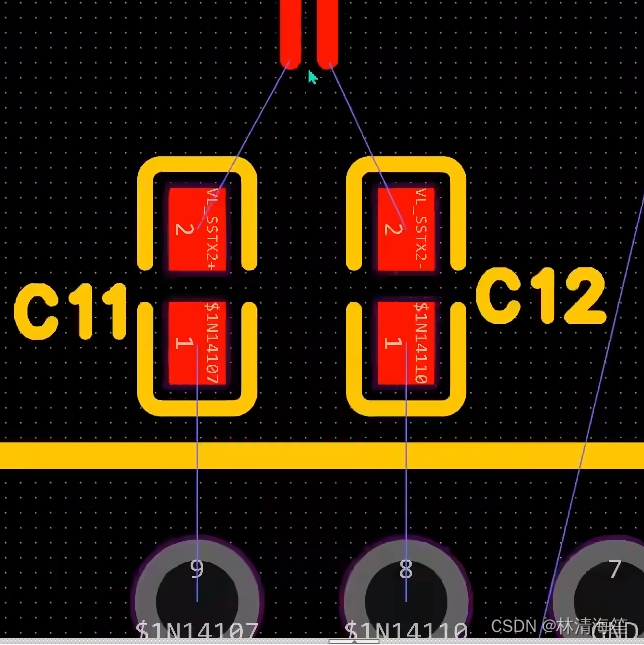

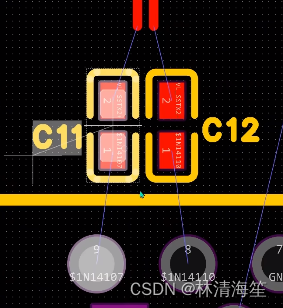

- 因为在之前控阻抗的时候,控制的是共面差分阻抗,所以这里还是会要求每隔150mil左右进行一个包地处理,因此在这里线预留GND过孔站位,确保要与GND靠得最近。

- 在这里走线绕开前面留下的过孔。

- 在这里有一个小细节,上面下来的差分对间距较小,但是在电容往下连接时,如果直接顺畅的拉上来的话,间距较大。这样是显然不符合差分线的。

- 所以我们需要对其进行耦合,将两个电容靠近一点。这样连线就是耦合了

- 如果想要速度上去的话,这些信号线的弯越少越好。2.0的信号线必须让路。

- 这里如果想要直接这样拉的话,太靠近引脚拐角太小了,一出来就拐一个大弯,这样是非常不利于高速信号线的信号传输的。

- 所以可以将过孔整体往后挪。

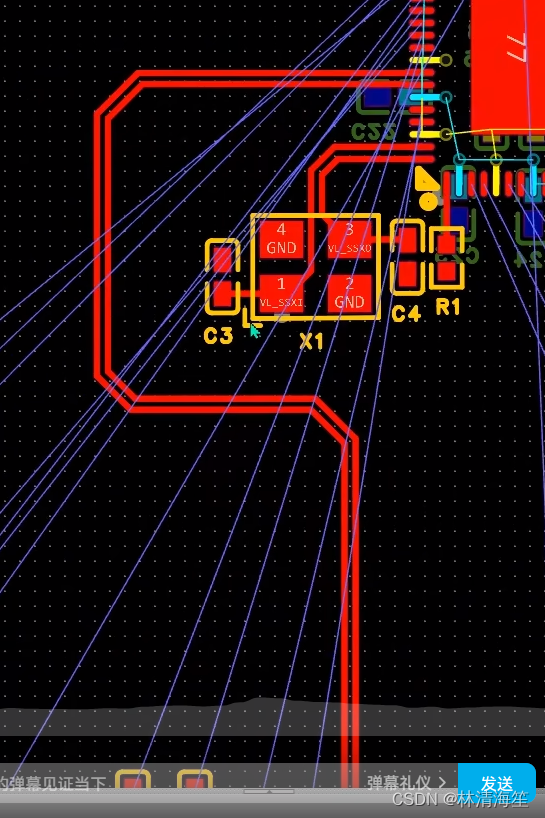

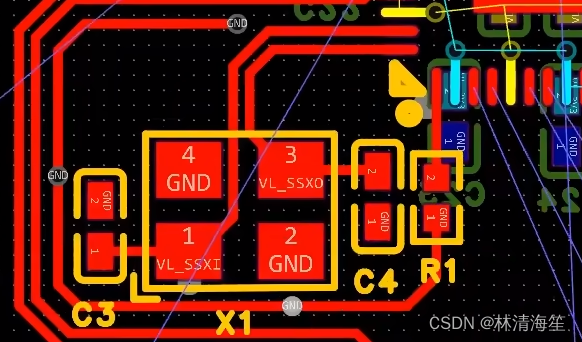

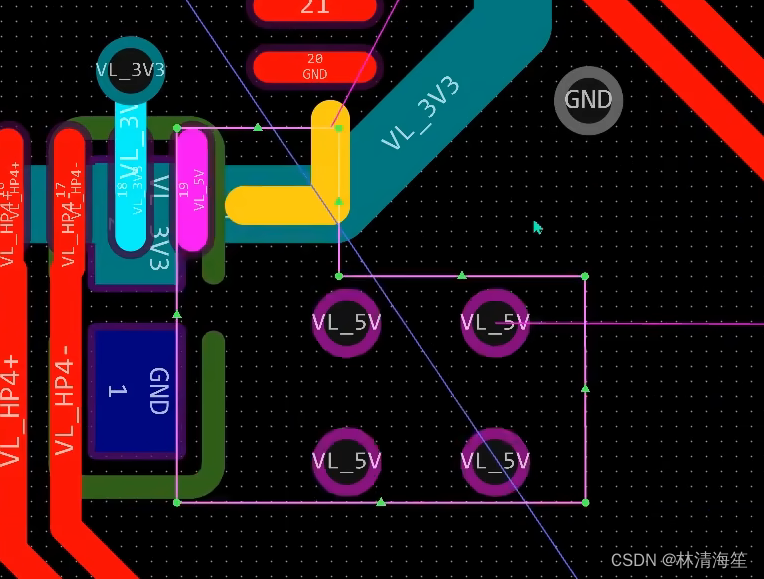

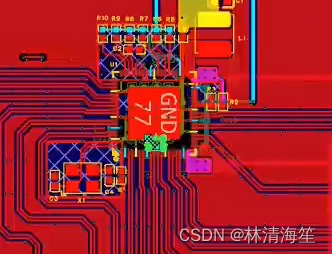

晶振包地处理

- 利用GND线将晶振饶一圈

- 然后还要在这些区域打上过孔,先用过孔进行占位置。后续整体布局完成后再进行调整。

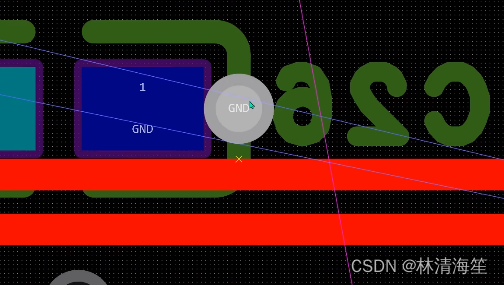

过孔不要放在焊盘上

- 注意不要把过孔放在焊盘上,这样容易造成漏锡。

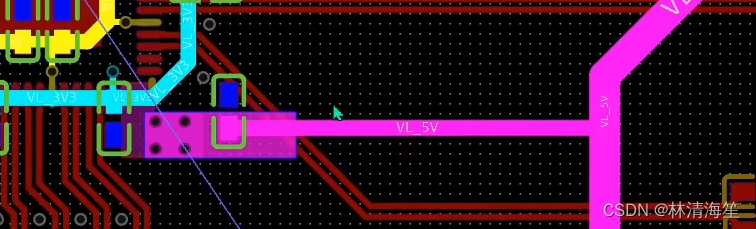

芯片内部电源线

填充区域连接

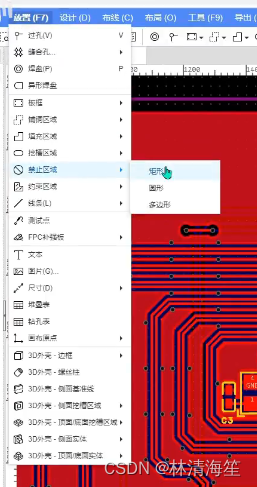

- 这里导线只有8mil,可能不够,这里我们可以点击放置,选择填充区域,选择多边形。

- 在这里进行多边形的填充,填充完后点击鼠标右键进行确认。然后调整填充区域,全部变为90度。

- 整体铺铜连接,这样导线就可以删除了。

- 这样填充的话,走过的电流肯定是要比单纯的导线走过的电流要大得多。

- 这里我们可以添加圆角,10mil半径,进行倒圆角。

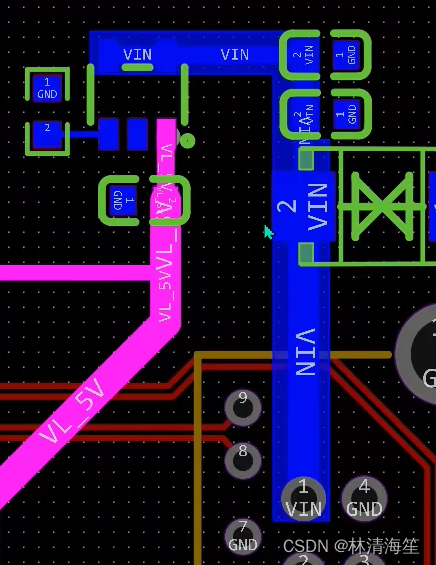

电源层的连线

- 采用20mil进行连线。相当于是电源总线,然后分别将各支路进行连接。

- 而对于上面3.3v的线(蓝色),如果这样画的画,就相当于3.3v电源线将芯片包裹起来了,形成了一个圈。这样其实是对整个芯片不好的,可能会有干扰。

- 这里我们可以通过其他地方绕一下,打过孔进行连接。因为这里本身就有电感了,本身干扰就很大,多一个圈其实也无所谓了。对芯片周围信号进行改善。

- 40milVin总线

- 5V到芯片,芯片电流没有那么大,所以只需20mil即可,连接到总线上。

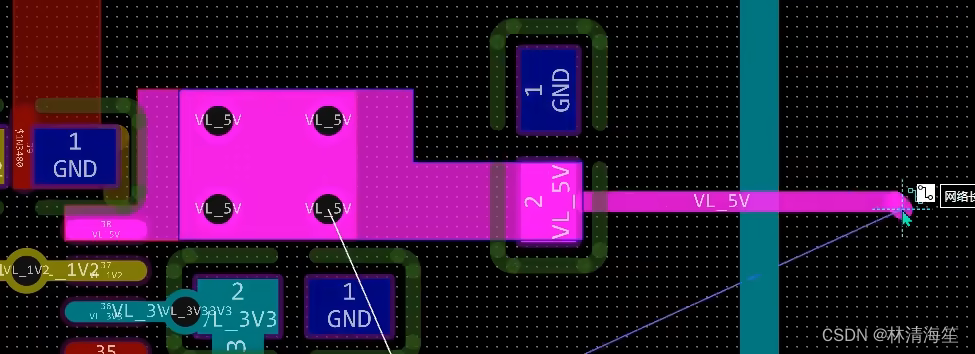

芯片输入电源引脚连接

- 芯片电源引脚的引出。因为这个芯片只有1路的5v输入,还要转化为其他的电压,所以消耗挺大的。像这样焊盘的宽度只有8mil左右,就算有两个焊盘也只有16mil左右,是比较极限的。

- 这里我们可以采用过孔加全极限的形式,尽可能保证5v输入的稳定。

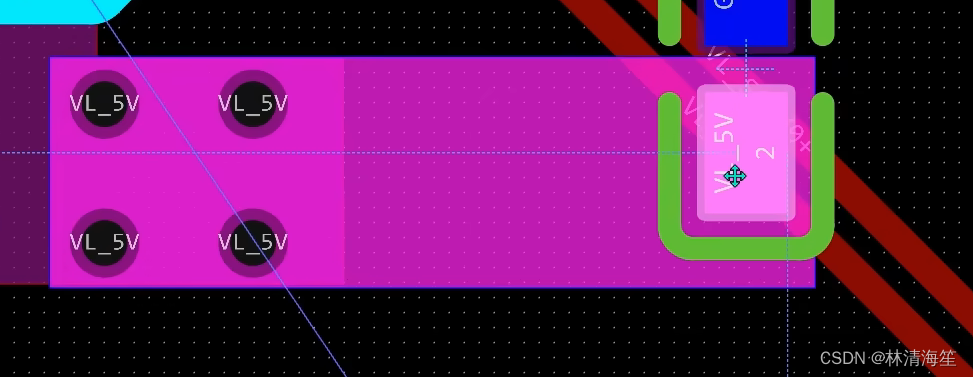

- 放置四个过孔,尽量分开些,不要分割底下的铜皮。

- 顶层放置铜皮,对其进行填充

- 对底层也一样,放置多边形填充区域,

3.PCB设计优化

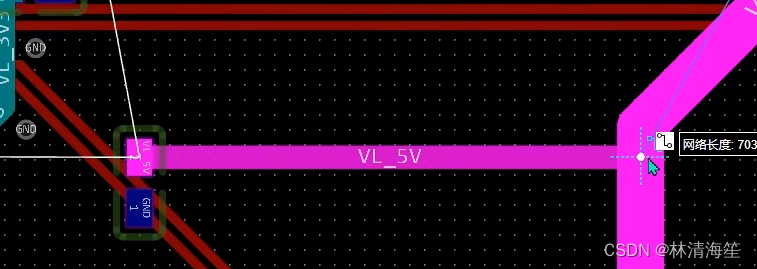

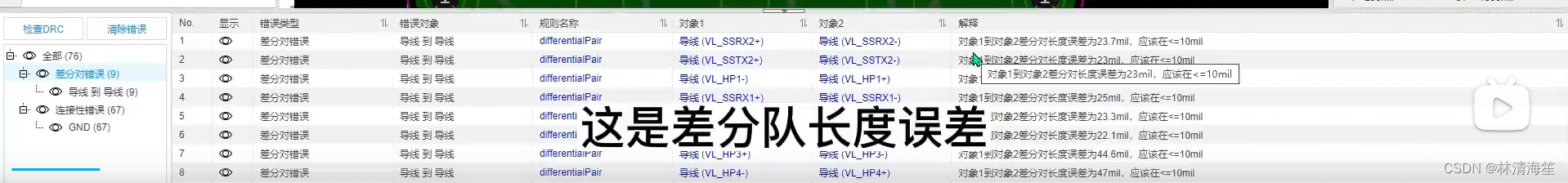

差分对弥补

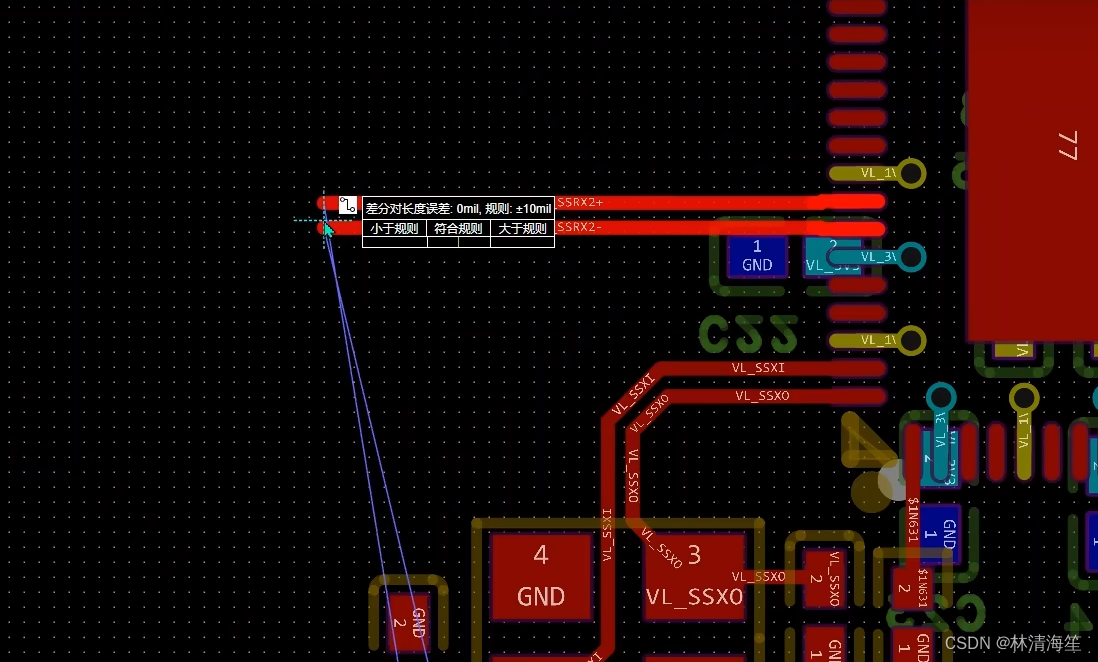

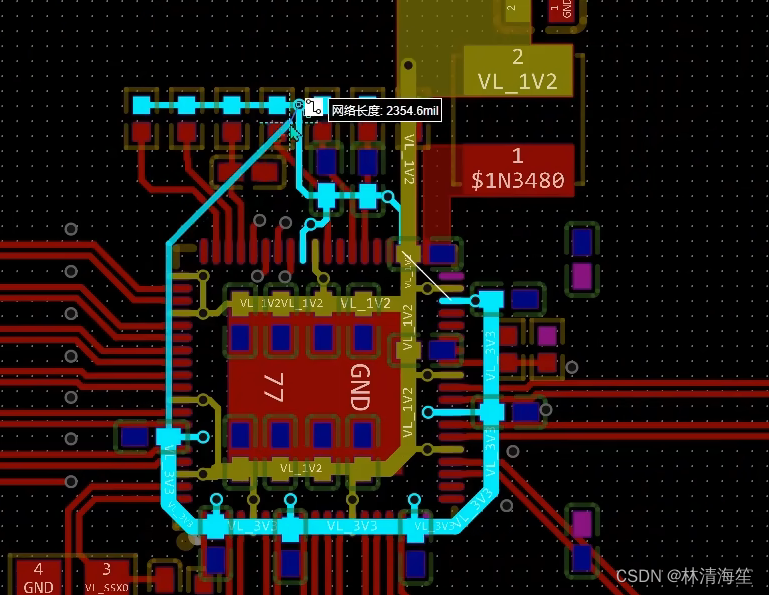

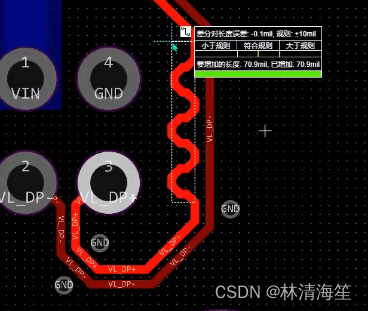

- 下面的DRC错误是差分对误差超过10mil导致的,需要进行等长调节,确保误差在10mil以内,尽量越少越好。

- USB两组高速差分线,建议误差不超过5mil

- 在左侧选择网络,选择差分对,根据每一组差分对,根据他们每条导线的长度。

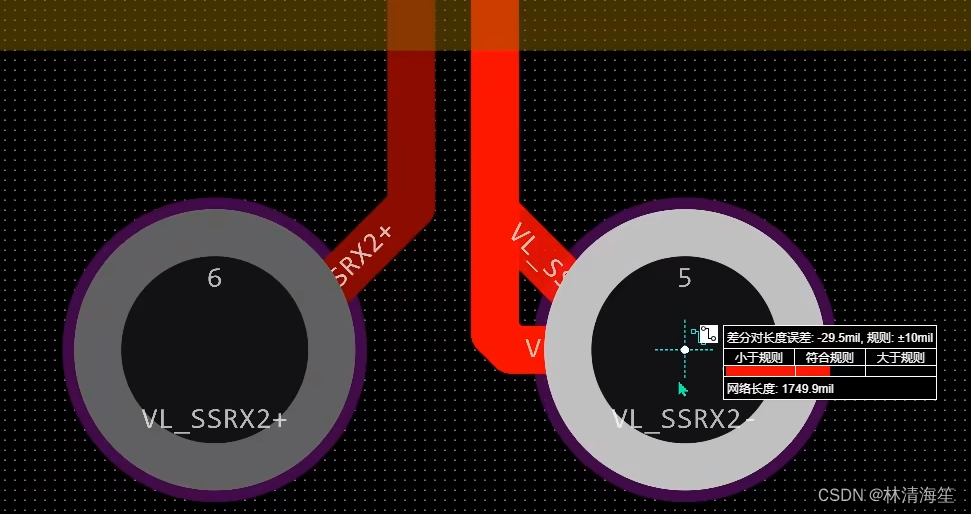

- 在工具栏中选择布线,选择等长调节,我们选择较短的线进行增加长度,以此来减少长度误差。

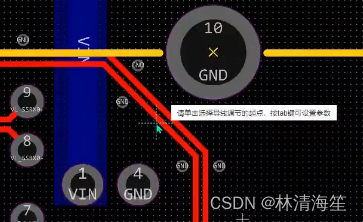

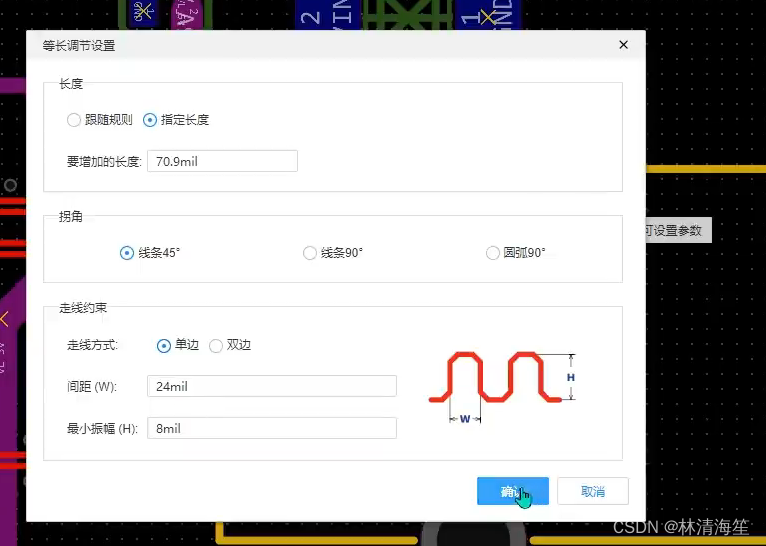

- 在我们选择完之后,有提示说选择导线调节起点,按住TAB键可以设置参数。

- 按住TAB键,进入设置界面。

- 首先是长度设置,我们选择了指定的长度。在增加长度的提示框中,我们可以进行简单的加减法运算。输入1707.8-1636.9,输入完成后点击空白区域,系统就会自动计算完成了。

- 长度值设置完后,设置拐角的方式,建议选择线条45度或圆弧90度。

- 走线约束,有单边和双边走线。如果是布局较为紧凑,可以选择双边。本次设置空间较为充裕,使用单边即可。

- 重点是间隔以及最小振幅的设置。间隔一般采用3W原则。差分线宽是8mil,这里我们建议在24mil比较合适。最小振幅在1W左右比较合适。这里按照线宽的设置为8mil。设置完成后点击确认。

然后选择起点,起点选择好后向上拉,有白色的框,系统就会在白色区域内自动给我们绕线。这里不建议绕线的幅度较大。使其误差小于0.1mil。

删除游离铜块

- 在铺完GND后,有一些游离铜块是不利于信号质量的。

- 这时候我们可以防止禁止区域

- 对晶振区域禁止铺铜,进行包地处理

- 将游离铜块都禁止铺铜。

6646

6646

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?