Chris射频IC教程学习笔记

1. 教程简介和BLE射频收发机系统结构介绍

2.1 低噪声放大器电路结构以及单晶体管仿真分析

2.2 LNA的testbench搭建及S参数仿真优化

2.3 LNA噪声、线性度及稳定性仿真分析

2.4 LNA增益控制,工艺角偏差,高低温对性能的影响

2.5 LNA完整电路设计及蒙特卡洛仿真

2.6 LNA版图设计及DRC/LVS验证

4 D类功率放大器PA电路设计/loadpull仿真/输出功率及效率PAE计算

(未完待续,还会继续更新)

一、低噪声放大器电路结构介绍

-

设计性能参数指标要求如下图所示

-

低噪放的输入形式是单端的输入端口,由于后续的混频器等部分是采用差分的电路结构,因此需要转变为差分信号。有两种方法去实现

- 在输入端做一个巴伦,把单端信号转变为差分信号输入到差分的低噪声放大器中,后续电路都采用差分的电路形式。但这种结构的缺点是在芯片中巴伦所占用的面积会非常大,必须要用平面螺旋绕线的电感形式去实现阻抗变换器。而且巴伦的成本非常高。

- 采用有源电路部分来实现一个单端到差分的一个转换,放大器为单端输入,然后差分输出的一种结构。

本电路结构采用方法2去实现单端到差分的转变

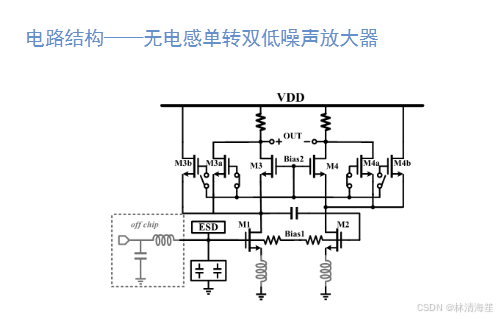

1. 电路结构——无电感单转双低噪声放大器

- 下图结构是单端输入差分输出的

(1)电路特点:

- 单端输入,差分输出:通过多级放大实现单端到差分的信号转换。

- 无片内电感:设计中未使用芯片内部的平面螺旋电感,减少芯片面积占用。

- 外部和封装电感:(芯片内部没有电感)

- 输入匹配电感:采用芯片外部的窄带L型匹配电感进行输入匹配。

- 源端简并电感:M1和M2利用封装中的引线电感来实现,而非片内电感。

(2)输入匹配:

- 输入端通过外部匹配电路实现窄带阻抗匹配,匹配后的信号进入芯片内部的ESD保护电路,随后进入第一级放大电路。

(3)放大级结构:

- M1晶体管:作为共源放大器,进行信号的首次放大并产生反相输出。

- M3级(与M1形成Cascode结构):

- 消除米勒效应,提高高频性能。

- 提高耐压能力,优化射频性能。

- M2晶体管:在栅极通过耦合电容接收来自M1的漏端信号,并进一步将耦合信号进行放大。

- M4级(与M2形成Cascode结构):与M2一起完成第二级差分放大,最终在M3和M4的漏端输出差分信号。

(4)相位转换:

- 单端到差分转换:

- M1将输入的正相信号反相放大,在漏端输出为反相信号(负相位)。

- 由于受到cascode的M3(同尺寸)影响,M1漏端电压增益为1,没有电压的放大作用,只是转化为电流。因为cascode的M3输入阻抗就等于跨导的倒数,因此被抵消掉了。

- 这也是cascode能够消除弥勒效应的原因,由于M1的栅极到漏端没有电压增益,所以Cgd的弥勒效应就不会产生,这样工作的频率会更高一些。

- M2接收耦合后的M1输出的反相等幅信号进入栅极,再经过反相放大后,在M2漏端输出正相信号。

- M3和M4的Cascode级放大为同相放大,因此在M3和M4漏端得到一对相位相反的差分信号。

- M1将输入的正相信号反相放大,在漏端输出为反相信号(负相位)。

- 在OUT输出端的正端得到的是只经过了m1一次反向放大,然后m3的一个同向放大,是一个反相信号。在另一端负端,是经过了两次反向放大(m1m2),一次同向的信号放大,最终得到的是一个同相信号。

(5)增益控制机制:

- 辅助晶体管(M3a/M3b和M4a/M4b):(用于控制整个电路的增益)

- 将m1和m2产生的电流进行分流,一部分(m3a和m4a)是经过负载电阻转化为最终输出信号的电压,另一部分电流(m3b和m4b)直接旁路到电源端,从而降低放大器的增益。

- 当M3b和M4b导通时,放大器的整体增益减小。

- 在后续电路设计中做了功耗方面的优化设计,增益控制部分采用的是另外一种方式来实现的,增益控制不是在casecode这个地方来进行实现,而是在输入这端,一个是通过改变他的工作电流。二是通过类似负反馈的形式来改变整体的增益。

(6)主要优点:

- 高频性能优越:通过优化结构,减小米勒效应并提升工作频率。

- 芯片设计紧凑:无片内电感,节省芯片面积。

- 增益灵活可调:通过辅助电路实现动态增益控制。

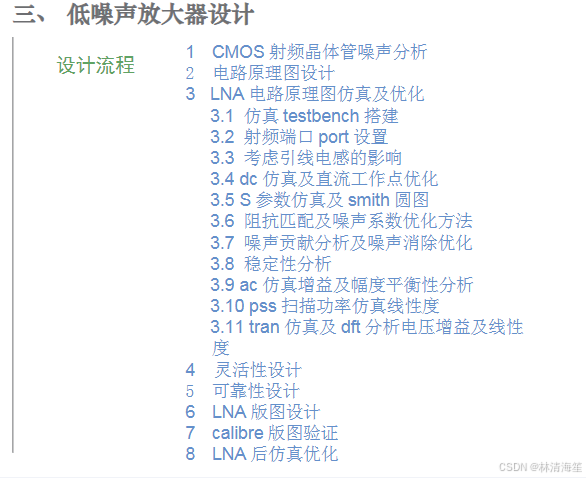

2.设计流程

二、CMOS射频晶体管噪声分析

- 这里参考的是清华大学石宝勇老师的《CMOS射频集成电路分析与设计》第八章 低噪声放大器

1. 两端口网络噪声分析理论

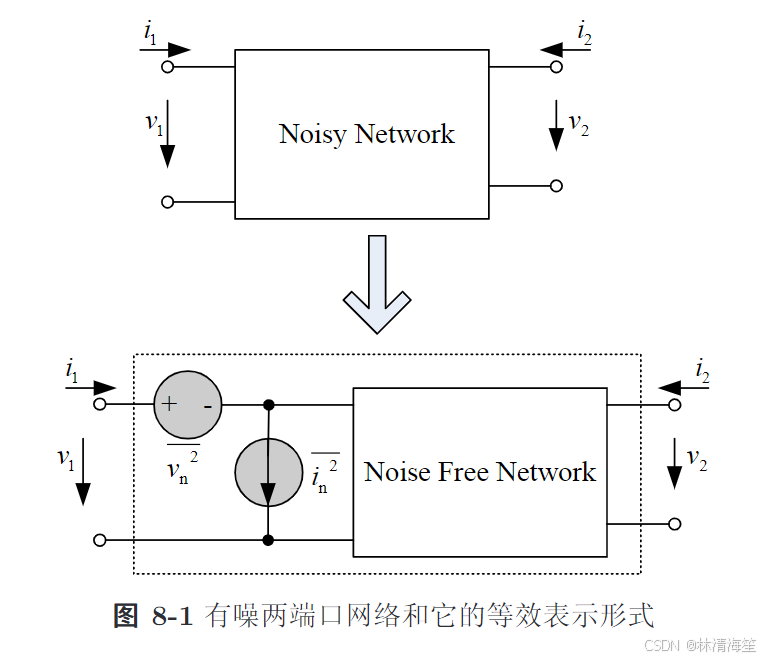

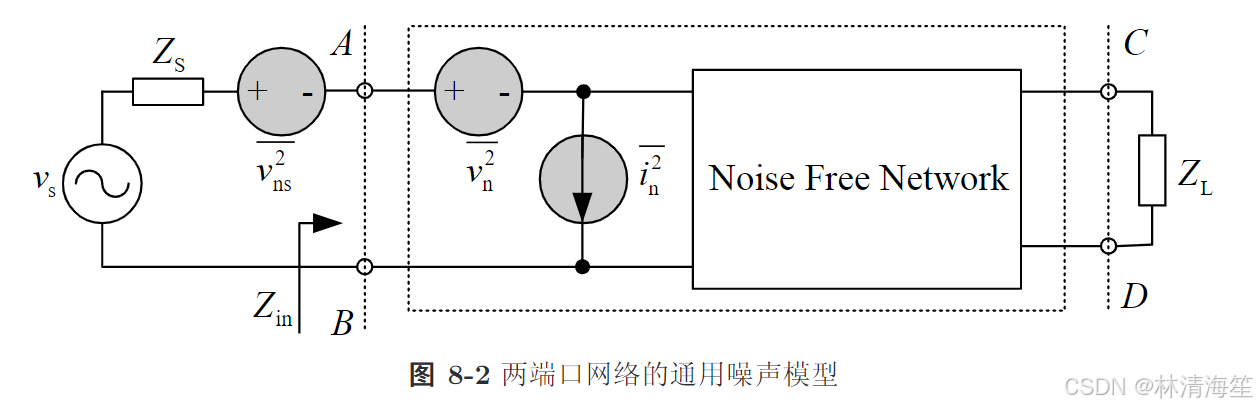

(1) 等效噪声模型:

- 噪声网络可以等效为一个无噪声的两端口网络,外加输入等效噪声电压 v n v_n vn 和等效噪声电流 i n i_n in。

- 这种模型有助于将复杂电路的噪声特性归约为输入端的噪声分析。

(2) 噪声系数公式:

- 噪声系数

F

F

F 的表达式为:

F = F min + R n G s [ ( G s − G opt ) 2 + ( B s − B opt ) 2 ] F = F_{\text{min}} + \frac{R_n}{G_s} \left[ (G_s - G_{\text{opt}})^2 + (B_s - B_{\text{opt}})^2 \right] F=Fmin+GsRn[(Gs−Gopt)2+(Bs−Bopt)2]- F min F_{\text{min}} Fmin:最小噪声系数。

- R n R_n Rn:噪声电阻。

- G s , B s G_s, B_s Gs,Bs:输入导纳的实部和虚部。

- G opt , B opt G_{\text{opt}}, B_{\text{opt}} Gopt,Bopt:最佳噪声匹配点对应的导纳参数。

(3) 最佳噪声匹配:

- 为了使噪声系数达到最小,输入导纳

Y

s

Y_s

Ys 应与最佳噪声导纳

Y

opt

Y_{\text{opt}}

Yopt 匹配,即:

Y s = G opt + j B opt Y_s = G_{\text{opt}} + jB_{\text{opt}} Ys=Gopt+jBopt

(4) 等噪声系数圆:

- 在史密斯圆图中,最佳噪声匹配点是等噪声系数圆的中心,其余噪声系数的分布呈闭合圆形。

- 等噪声系数圆有助于优化输入阻抗匹配设计。

2. MOS晶体管噪声模型分析

(1) 噪声源分类:

- 漏端沟道热噪声:

i n d 2 = 4 k T γ g d o Δ f i_{nd}^2 = 4kT\gamma g_{do}\Delta f ind2=4kTγgdoΔf

其中, γ \gamma γ 为与器件相关的噪声因子。 - 栅端诱导噪声(Induced Gate Noise):

i n g 2 = 4 k T δ g g Δ f i_{ng}^2 = 4kT\delta g_g \Delta f ing2=4kTδggΔf

其中, δ \delta δ 表示栅诱导噪声因子。

(2) 等效输入噪声:

- 通过噪声模型的转换,可以将漏端和栅端噪声等效为输入端噪声电压和噪声电流:

v n , eq 2 = i n d 2 g m 2 + i n g 2 ∣ j ω C g s ∣ 2 g m 2 v_{n,\text{eq}}^2 = \frac{i_{nd}^2}{g_m^2} + \frac{i_{ng}^2 |j\omega C_{gs}|^2}{g_m^2} vn,eq2=gm2ind2+gm2ing2∣jωCgs∣2

(3) MOS晶体管噪声参数:

- 噪声电阻:

R n = γ α 1 g m R_n = \frac{\gamma}{\alpha} \frac{1}{g_m} Rn=αγgm1 - 最佳噪声导纳:

G opt = α ω C g s δ γ ( 1 − ∣ c ∣ 2 ) G_{\text{opt}} = \alpha \omega C_{gs} \sqrt{\frac{\delta}{\gamma}(1-|c|^2)} Gopt=αωCgsγδ(1−∣c∣2)

B opt = − ω C g s ( 1 − α δ γ ) B_{\text{opt}} = -\omega C_{gs} (1-\alpha \sqrt{\frac{\delta}{\gamma}}) Bopt=−ωCgs(1−αγδ) - 最小噪声系数:

F min = 1 + 2 5 ω t ω δ γ ( 1 − ∣ c ∣ 2 ) F_{\text{min}} = 1 + \frac{2}{\sqrt{5}\omega_t}\omega\sqrt{\frac{\delta}{\gamma}(1-|c|^2)} Fmin=1+5ωt2ωγδ(1−∣c∣2)

3. 设计中的关键问题

(1) 输入阻抗匹配:

- 噪声匹配:需使输入导纳 Y s = Y opt Y_s = Y_{\text{opt}} Ys=Yopt。

- 功率匹配:需使 Z s = Z i n ∗ Z_s = Z_{in}^* Zs=Zin∗。

- 噪声匹配与功率匹配在理论上难以同时满足。

(2)低频噪声的忽略:

- 射频设计中, 1 / f 1/f 1/f 噪声对高频性能的影响可忽略不计。

(3) 射频电路优化:

- 使用史密斯圆图优化输入阻抗匹配,平衡噪声系数与功率增益。

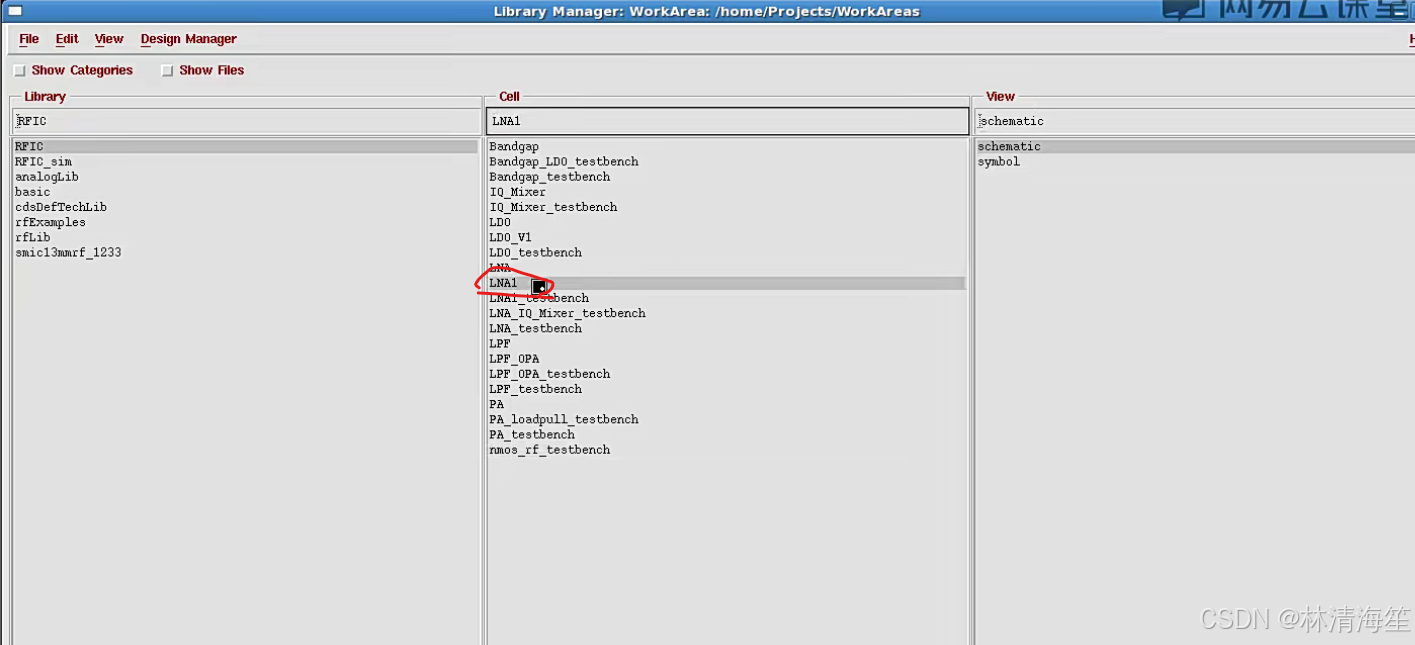

三、Cadence仿真电路

- 首先启动cadence设计软件,在桌面运行终端

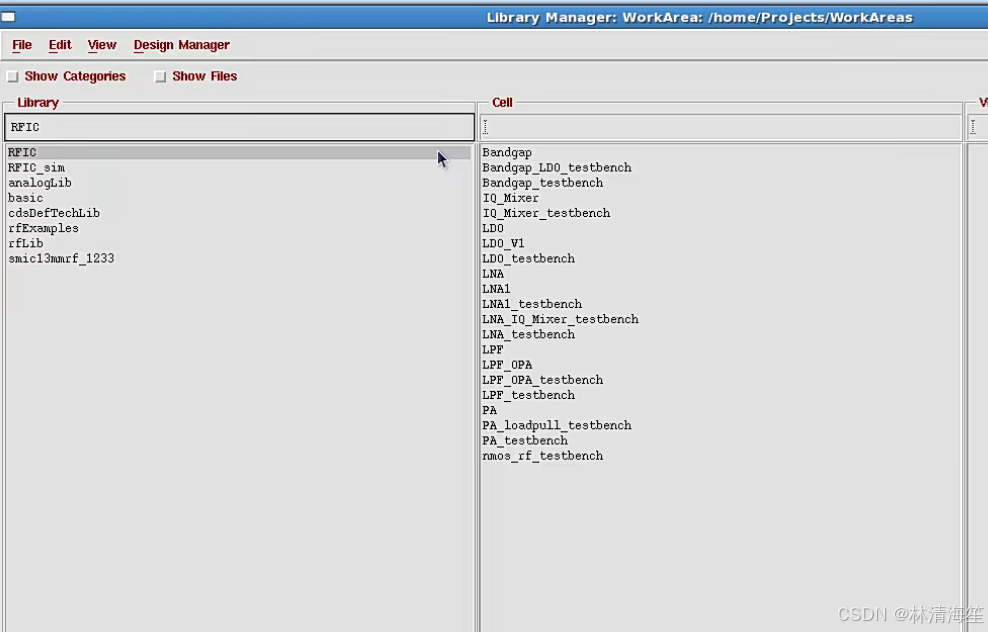

- smic13mmrf是使用到的工艺库

- RFIC是设计的工程文件

- RFIC_sim是设计过程中testbench放置的位置

1. 单晶体管仿真分析

- 晶体管的尺寸设计是低噪放最核心的参数

- 晶体管的性能参数可以通过参考工艺库的pdk文件对这个mos晶体管的说明,会提供该晶体管的sptre模型作为参考。

- 但在实际设计过程中,我们是通过直接仿真来提供更直观的设计,来确定晶体管的尺寸偏置电压等参数。

- 由于书本上的公式在推导过程中忽略了很多次要的因素或者变量的干扰影响,使得理论推导结果和实际仿真结果产生偏差。

- 特别是在随着频率越高,工艺越先进,沟道长度越小以后,各种的二阶效应,亚阈值的工作状态会跟实际的偏差越来越大。

- 因此在低频模拟电路设计里面,会引入很多gmid的方法,通过仿真然后去查表的方式去进行电路优化设计。

- 在射频电路设计中,模型会变得更复杂,就很难去推导出准确的公式。一般只会有一些趋势性具有指导意义的计算公式,像对于噪声、增益、线性度、失真等,但这些指导意义的公式也会存在较大的偏差,在实际电路设计过程中,是需要反复优化迭代的

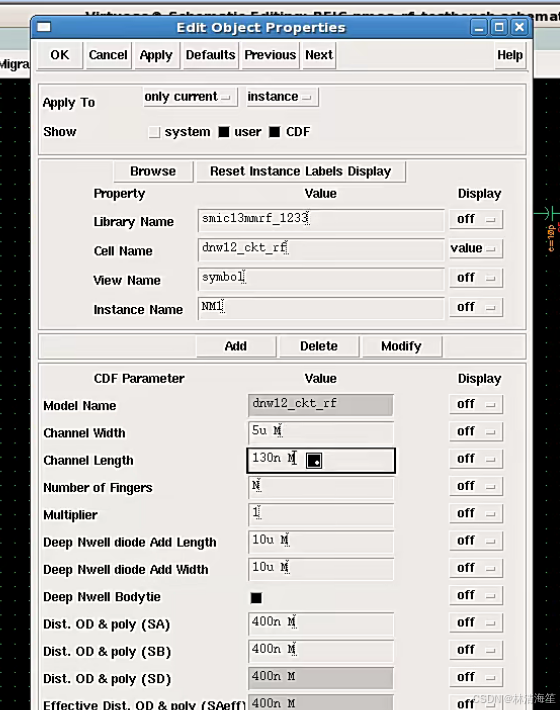

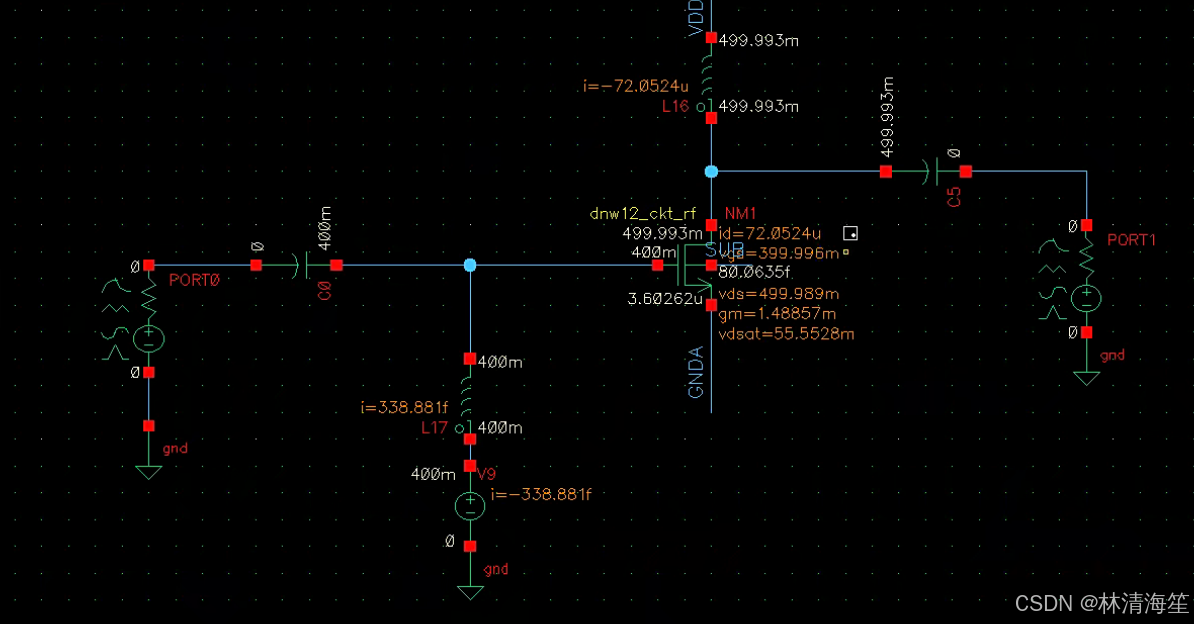

(1)原理图搭建

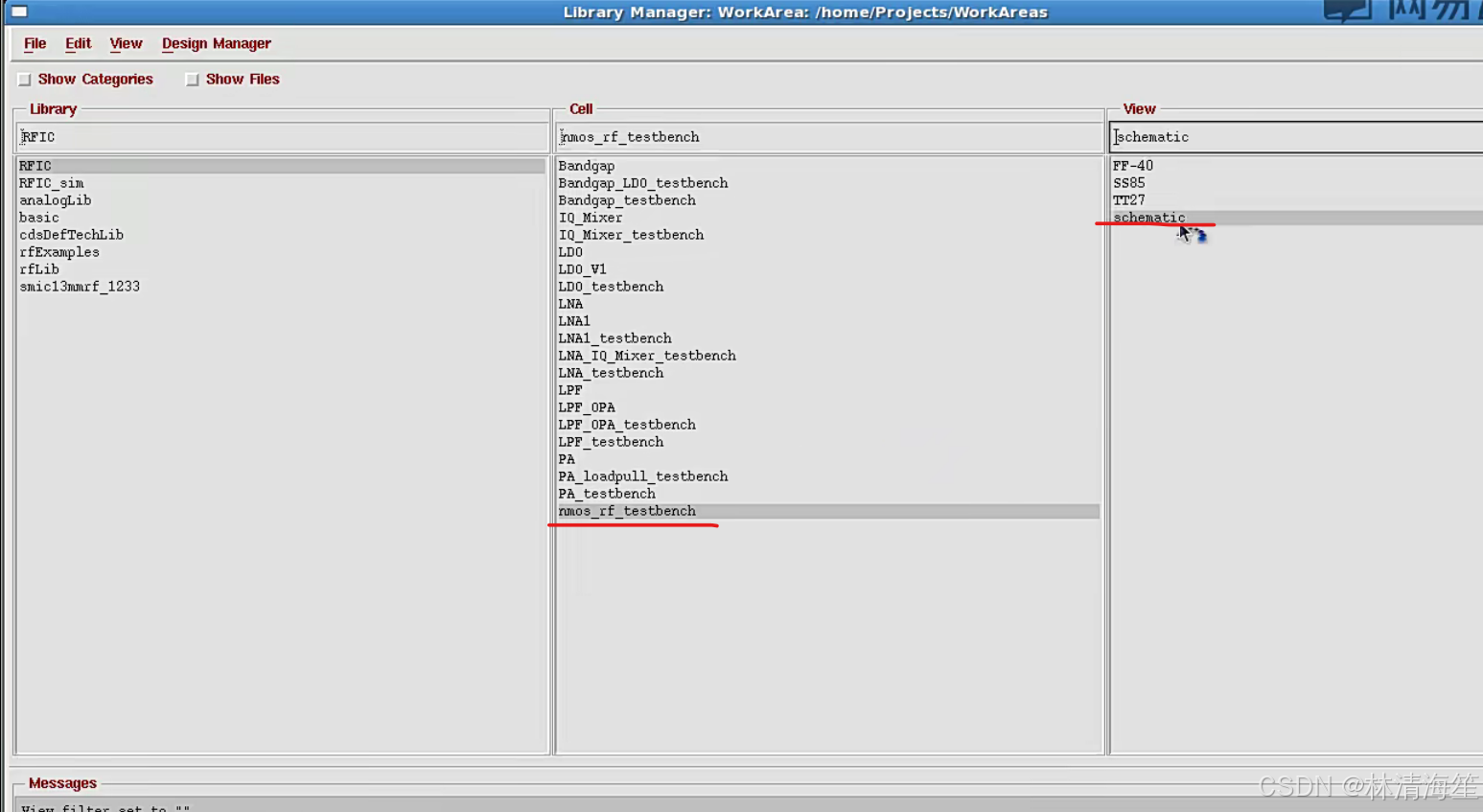

- 打开已经搭建好的nmos仿真工程文件

- testbench主要是为了评估射频晶体管的性能参数,包括直流参数、噪声参数,仿真的方法主要是直流仿真和s参数仿真。

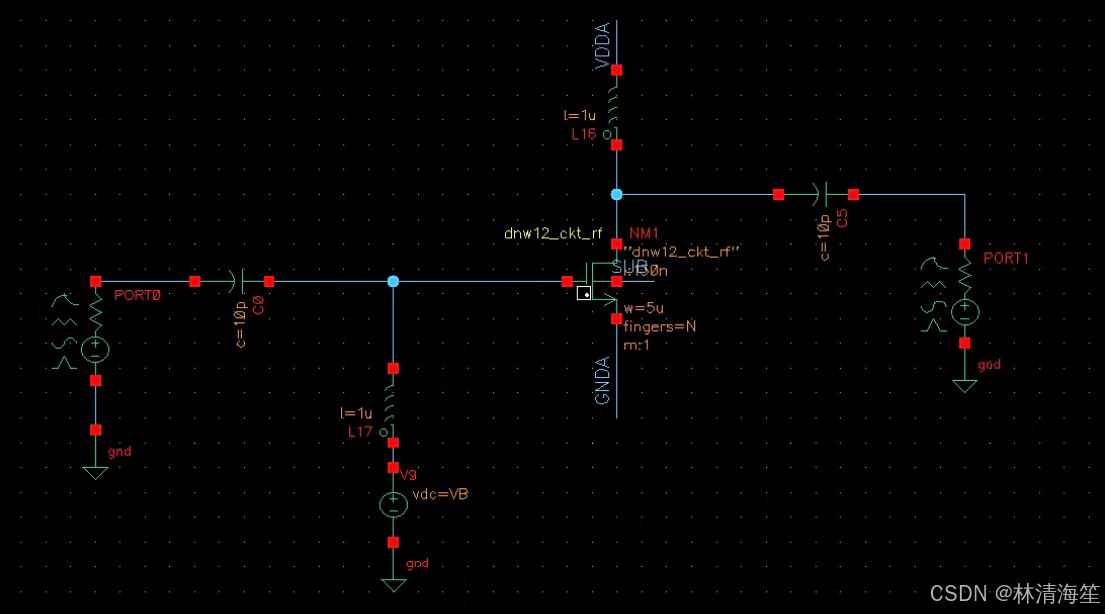

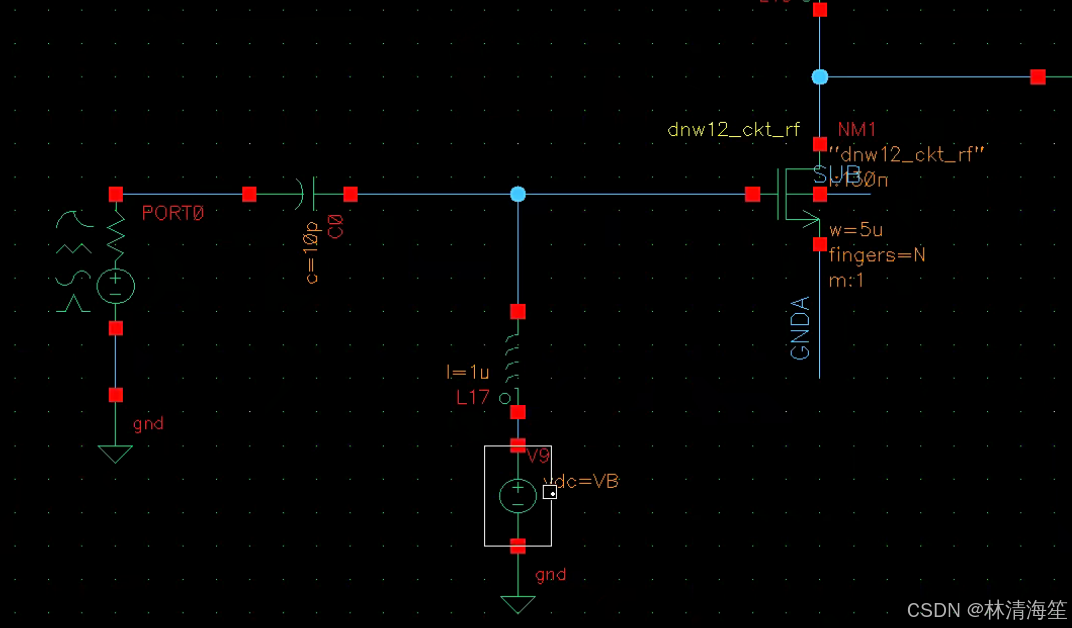

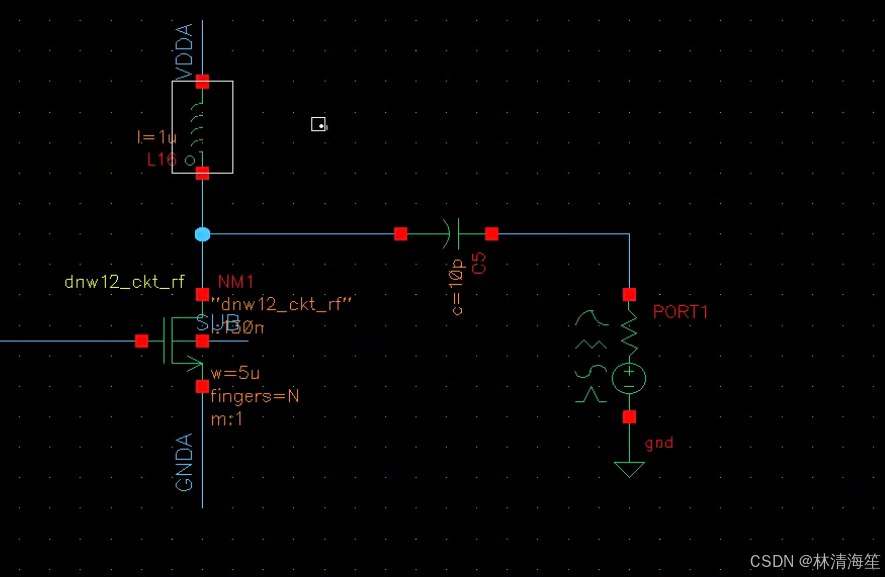

- 原理图如下

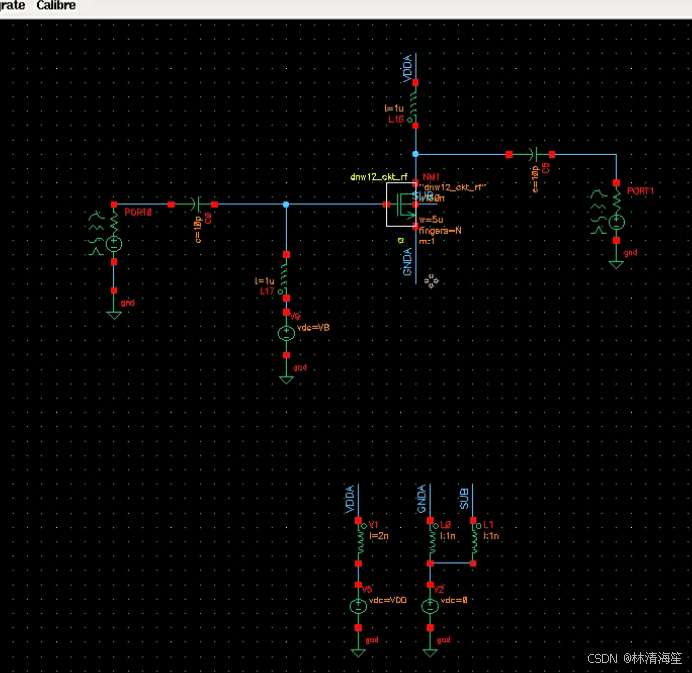

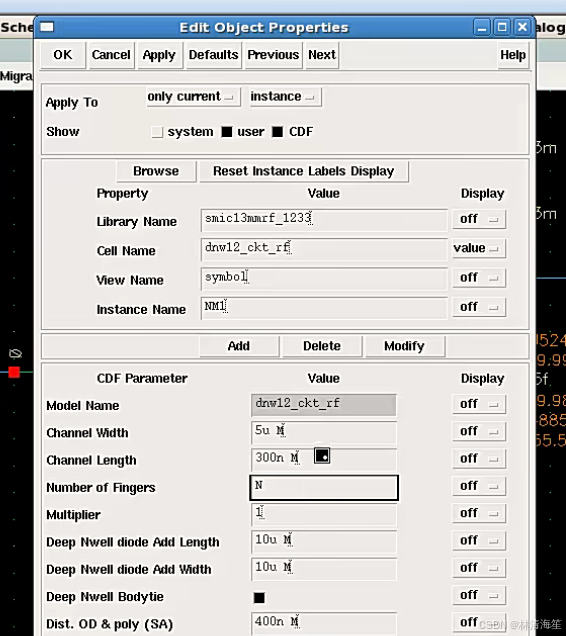

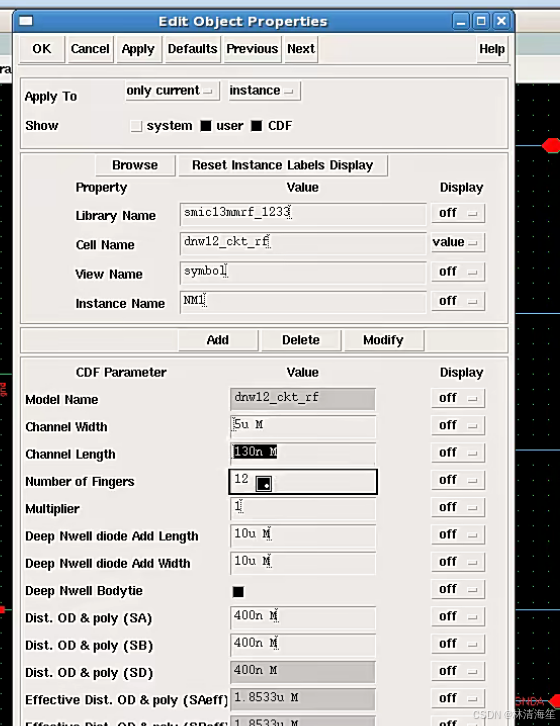

- 这里用到的器件就是nmos晶体管,采用1.2v deep n-well最小沟道长度的射频晶体管

- 选用deep n-well是因为,在最终做整个芯片版图的时候,我们会把整个放大器电路放在一个deep n well单独的深n井里面来进行隔离。那么由于deep n well深n井的存在,他对其他电路的干扰,或者其他电路对他干扰的耦合,就能够减到最小。起到提高抗干扰特性。也就是说,减小其他电路对低噪放敏感电路的影响。

- 所以我们会把低噪放的全部的器件都放在deep n well里面,因此rf器件就必须用到它的deep n well的这种类型的晶体管,也就是dnw12_ckt_rf。这种类型的晶体管跟普通的nmos_rf在建模是没有什么差别的,只是在版图上增加一个deep n well的深井。

- 晶体管的沟道长度channel length设定为工艺最小沟道长度130nm

- 对射频电路来说,为了提高它的射频特性,降低它的噪声系数,提高射频增益。通常构造的沟道长度基本上是取得一个工艺最小的沟道长度。所以我们选择的是130纳米的沟道长度。

- 沟道宽度channel width设置为5um,这是单个finger的宽度

- finger number设置为参数N

- 工艺的pdk要求finger的数量必须为偶数个,且不能小于四个。主要是跟他模型提取和最终建模时的一些参数会有关系。所以他做了一定的限制。

- multiplier是晶体管的并联个数,设置为1

- 其他的参数采用默认的,不用修改

- 然后我们对晶体管搭建了仿真电路

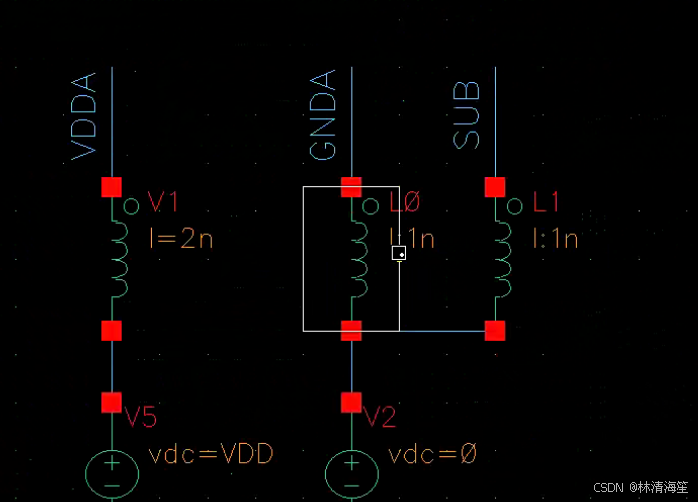

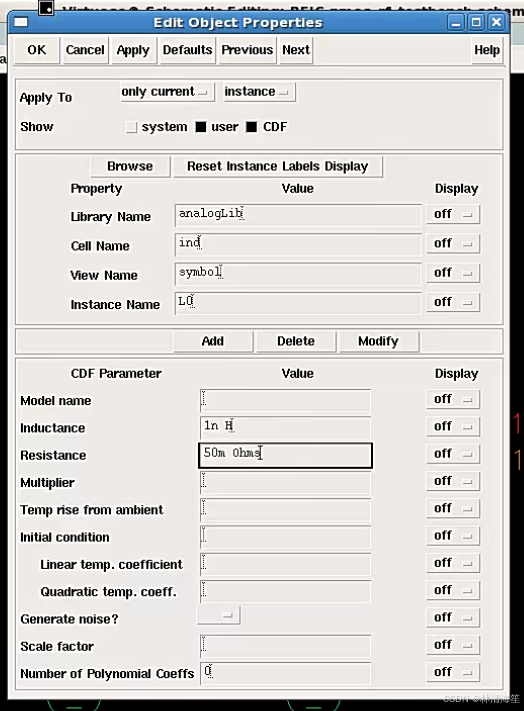

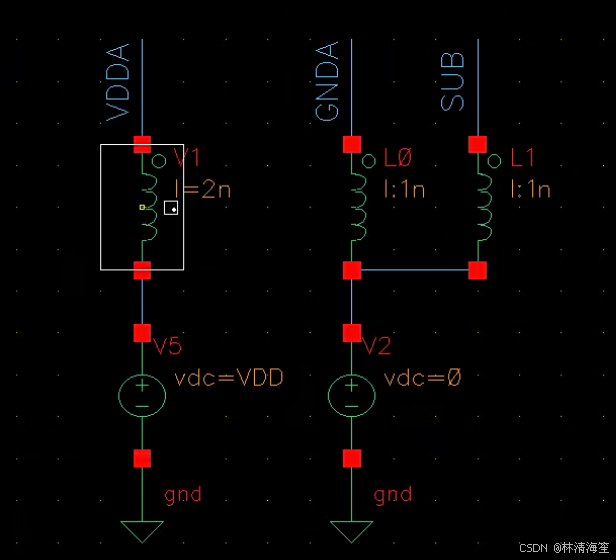

- nmos的源端接在GNDA上,GNDA接在1nH的引线电感模型上,引线的寄生电阻是50m欧姆

- nmos的衬底接在SUB端,同样单独分出接到引线电感上面

- SUB和GNDA经过引线电感后,接在0v的电压源上面,即理想的GND上面

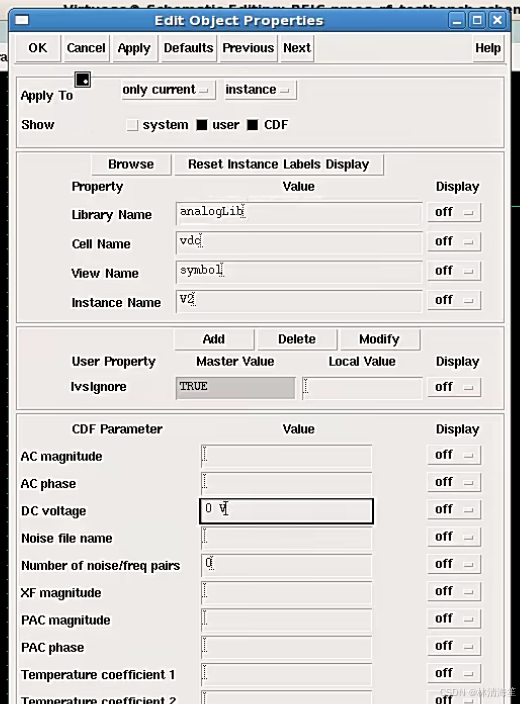

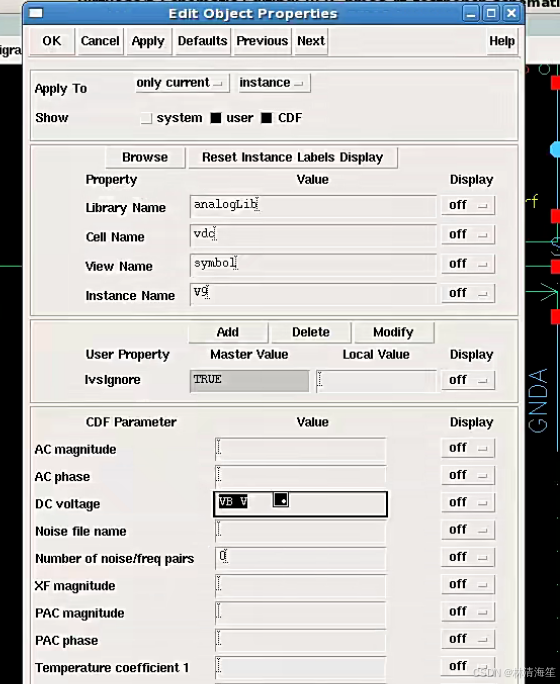

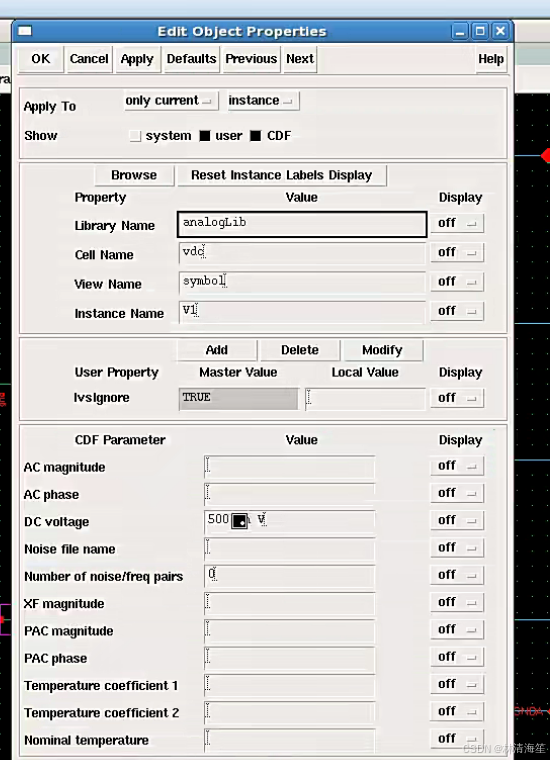

- 晶体管的栅极提供了偏置电压,是通过理想的电压源来提供的

- 直流电压源的电压设置为参数VB,进行偏置

- 栅极的直流电压会通过1uH的的理想电感,隔离后再输入到栅极

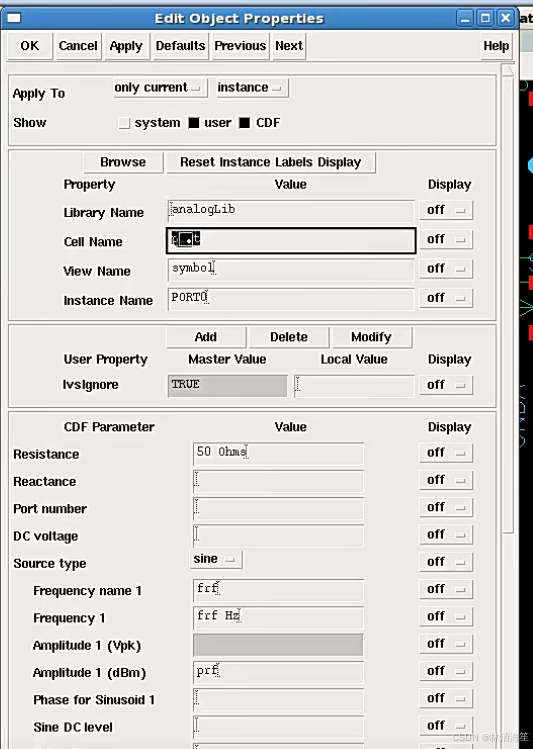

- 输入端口port与栅极连接的时候有10pF隔直电容

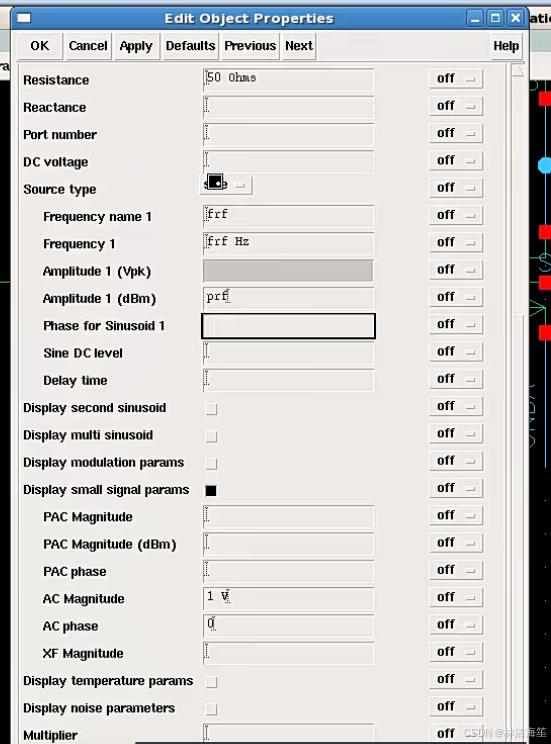

- 端口阻抗为50欧姆

- 由于已经有偏置电流,因此DC voltage可以悬空不填

- 信号源类型source type一般设置为sine正弦信号,然后就会有该信号的名字、频率、幅度

- 幅度有两种设置方法,一个是设置峰峰值电压,还有一种是设置功率。在这里我们选择是功率prf

- 对于小信号参数small signal params,在防PAC+pss的时候需要在这里设置

- AC仿真需要用到的是AC信号的幅度和相位

- 晶体管漏端接入1uH的大电感,即射频扼流圈,然后接入漏端电压VDDA,是接到理想电压源里面,也有2nH的引线电感模型

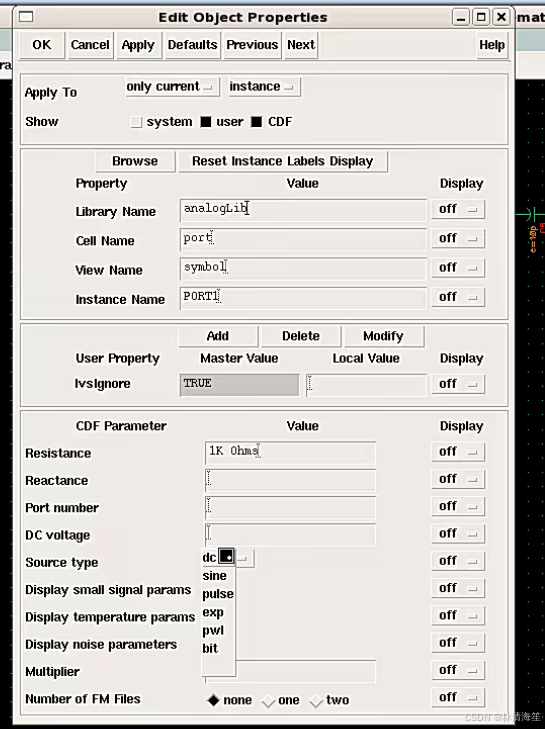

- 在输出端的port上,设置的信号类型是dc,因为它是负载端,没有必要去提供射频信号,所以是直流端口

- 负载阻抗设置的是1k欧姆。阻抗不一样对仿真可能会有影响,但是对分析是没有什么影响的

- 设1000欧姆主要是为了模拟最终低噪声放大器输出以后到射频输入端的基本输入阻抗,给了他一个高阻抗的负载。

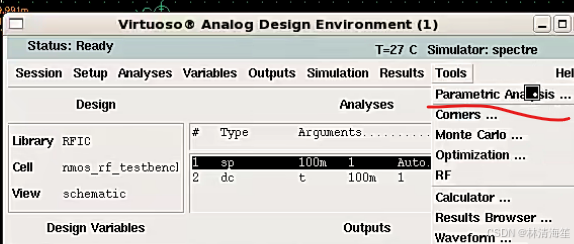

(2)仿真分析

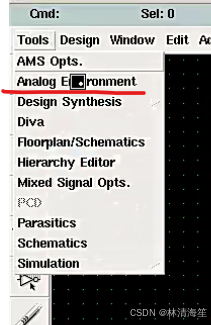

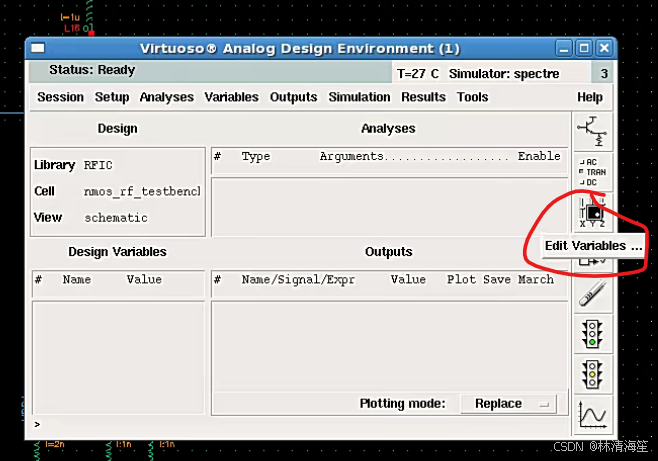

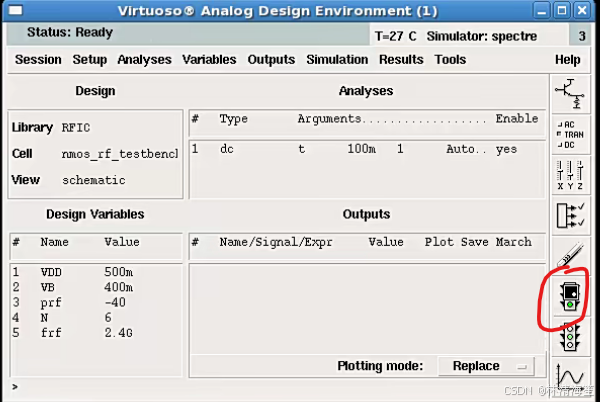

- 首先打开模拟设计环境

· 仿真参数设置

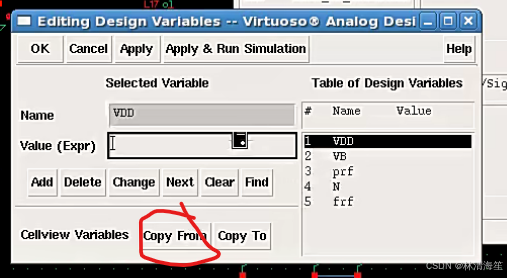

- 查看仿真的参数有哪些

- 点击copy from,把所有参数都显示出来

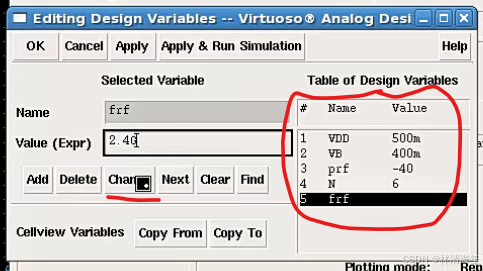

- 漏端电压vdd设置为0. 5v

- 其他参数设置如下

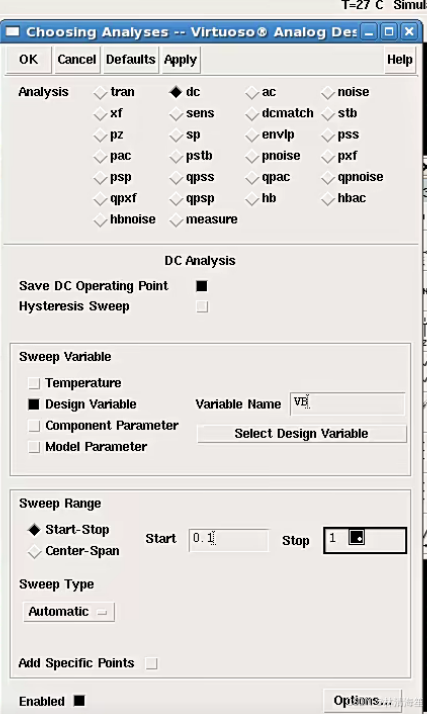

- 然后我们需要设置直流仿真

- 参数扫描主要是选择晶体管的栅极偏置电压,来看基本的工作电流状况

- 然后扫描出来的结果,点击check and save,然后点击运行

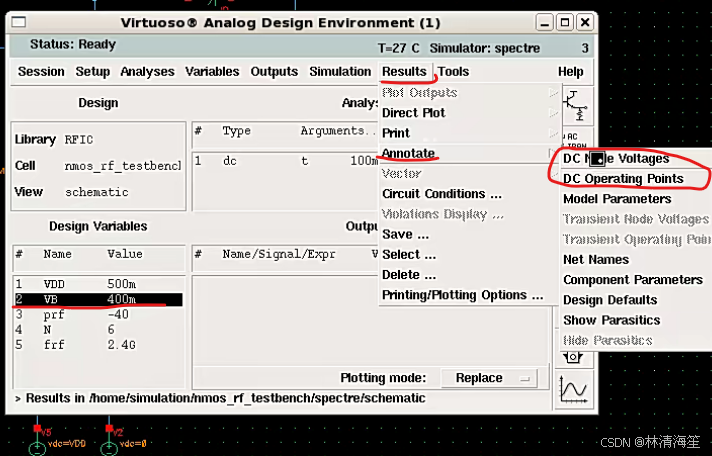

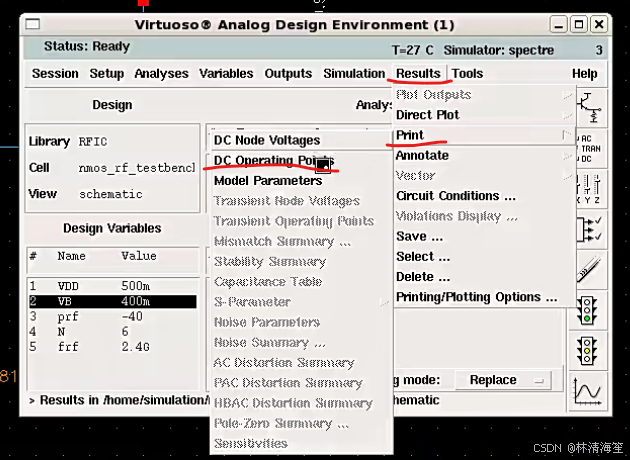

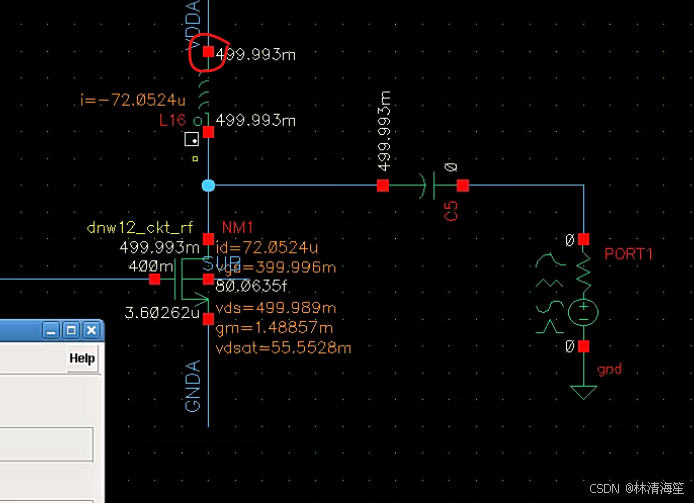

节点电压显示

- 然后我们查看在VB为400mv下的直流仿真结果,把节点电压和直流工作点都显示出来

- 可以看到在输入为400mv的时候,晶体管漏端电压为72uA

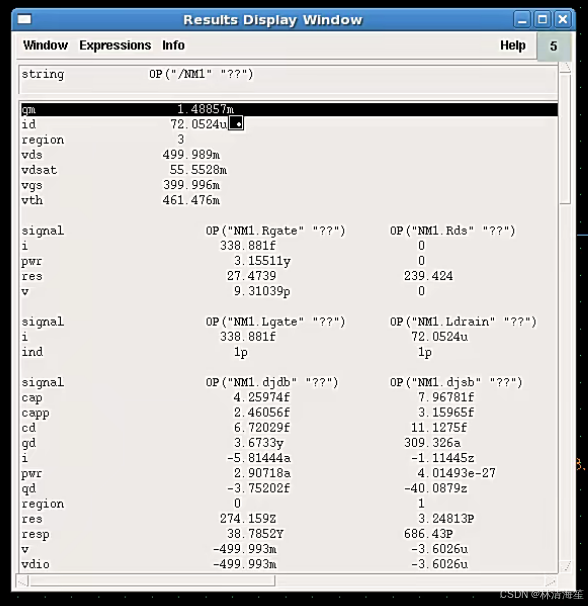

· 直流工作点打印

- 然后可以把晶体管的直流工作点给打印出来

- 这里我们要重点关注阈值电压Vth,为460mv

- 而vgs是小于vth的,所以晶体管是工作在截止区上

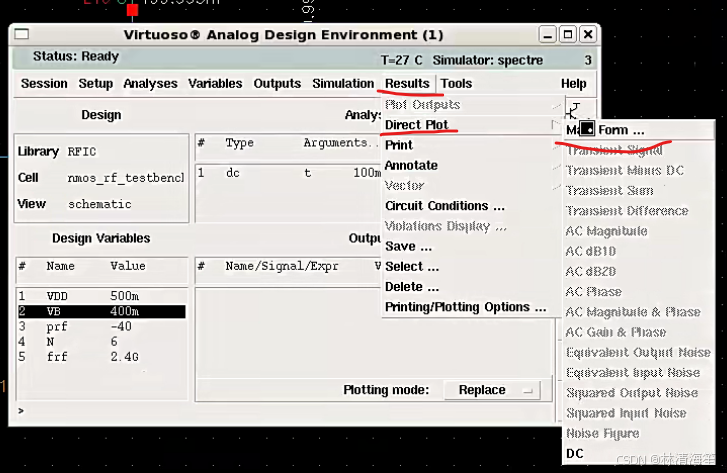

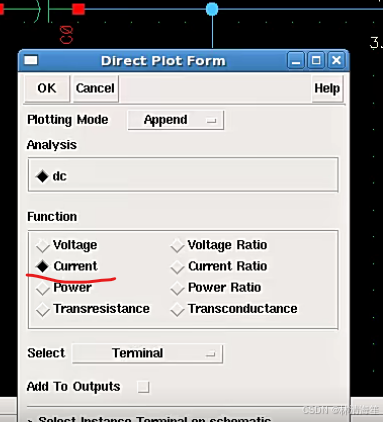

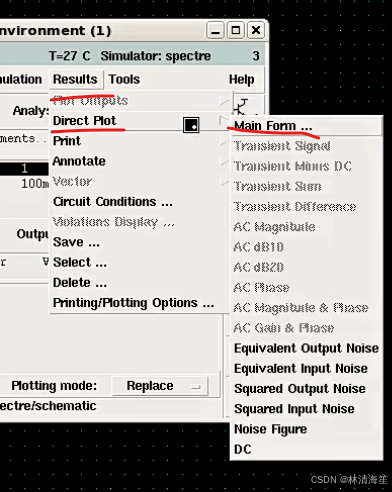

· 直流工作状态图形输出

- 如果想要查看晶体管的直流工作状态,选择main form

- 选择current电流,然后点击漏端电感的一段

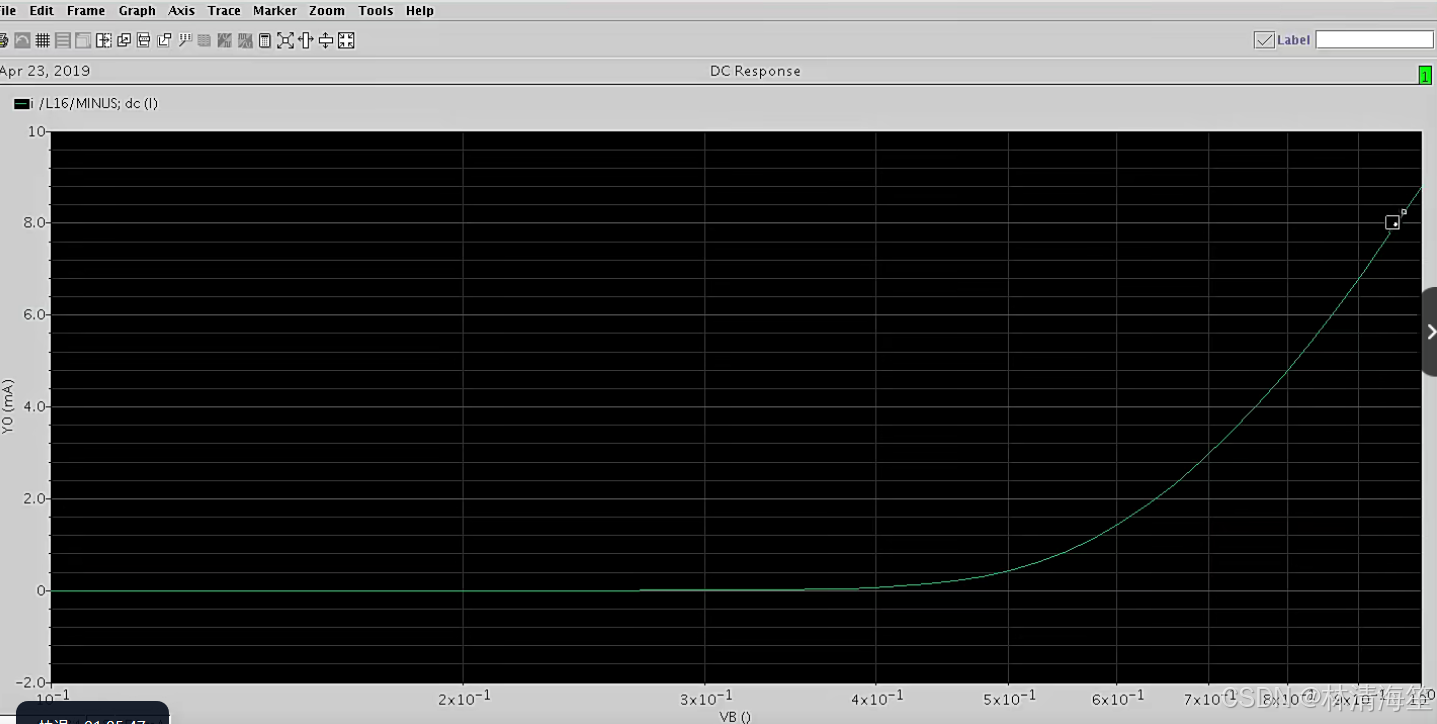

- 下图为晶体管直流的工作状态图

- 输出的波形可以发现在小于400mv的时候电流是非常小的,然后再慢慢接近到500毫伏的时候,电流就达到了400多微安,然后到600毫伏的基本上就有一点五毫安左右了。再往上到一伏的话,那么这个电流就变得非常非常的大了,到了八九毫安的一个电流值。

· 噪声系数

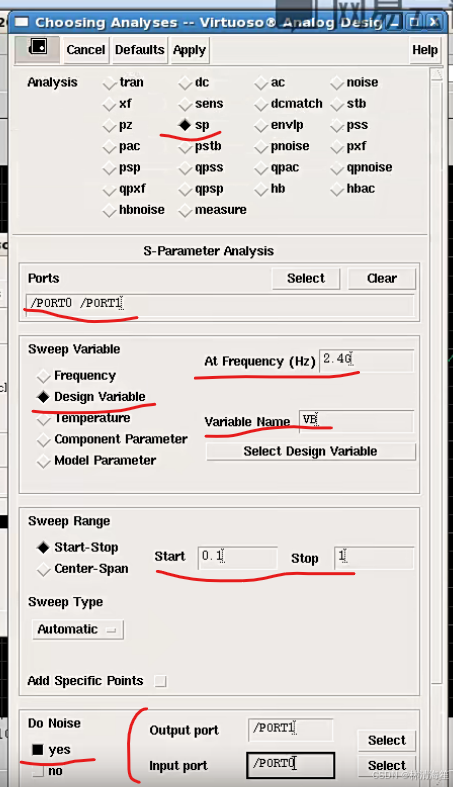

(s参数仿真)

- 我们还关心晶体管的射频参数,即噪声系数的问题

- 首先端口port,选择输入端和输出端port

- 扫描的变量,当晶体管静态的工作状态固定下是去扫描频率。由于这里需要扫描评估不同晶体管性能参数,改为扫描设计的变量,即晶体管的输入偏置栅极电压VB。工作频率选择2.4GHz。

- 如果我们需要去分析噪声性能,需要勾选Do Noise,

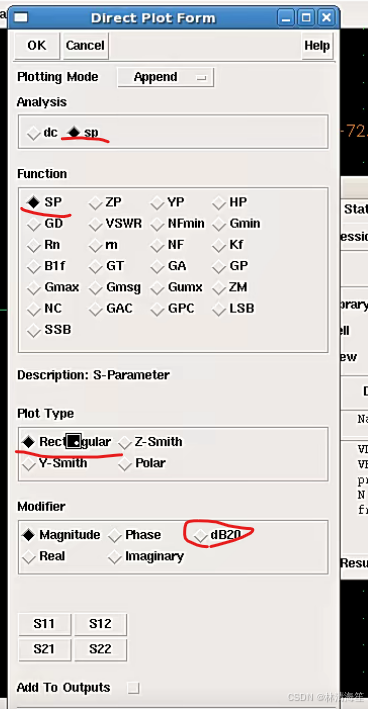

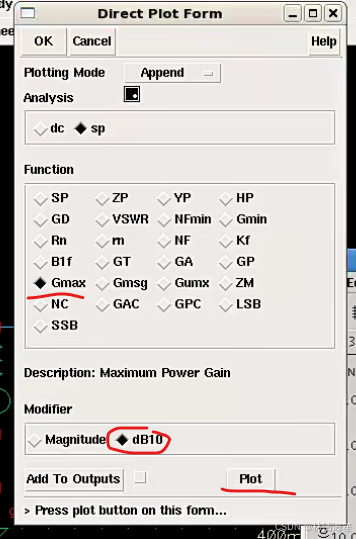

- 点击运行,然后选择direct plot form,选择SP

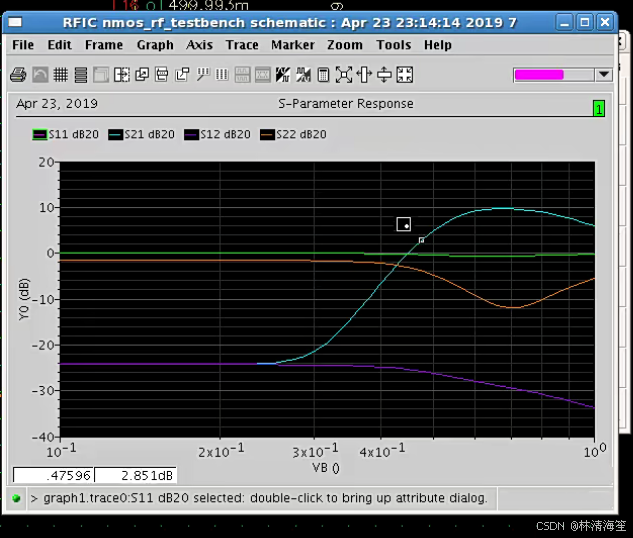

- s参数仿真一般选择dB20的形式,矩形rectangular图表

- s11是,s12是增益部分,s21反向隔离度,s22输出匹配

- 这里可以发现s参数的性能都不太好,所以直接查看这些数据是没有意义的

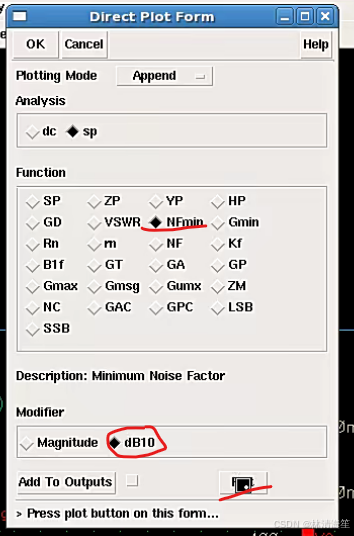

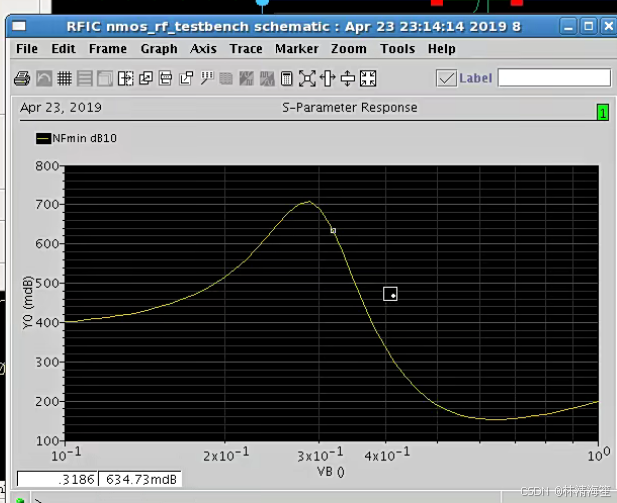

(最小噪声系数NF)

- 所以我们需要去查看最小噪声系数

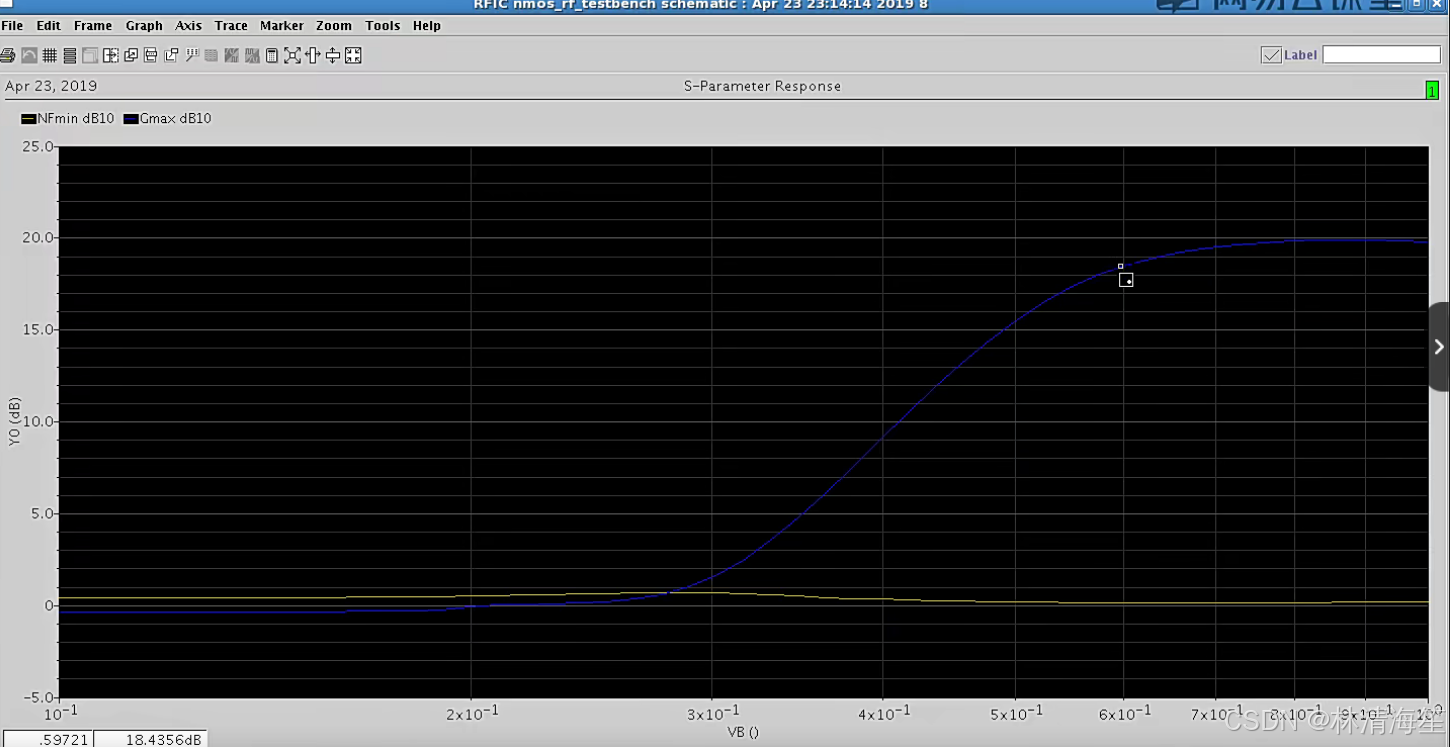

- VB在600多毫伏的时候能够获得一个最小噪声系数。

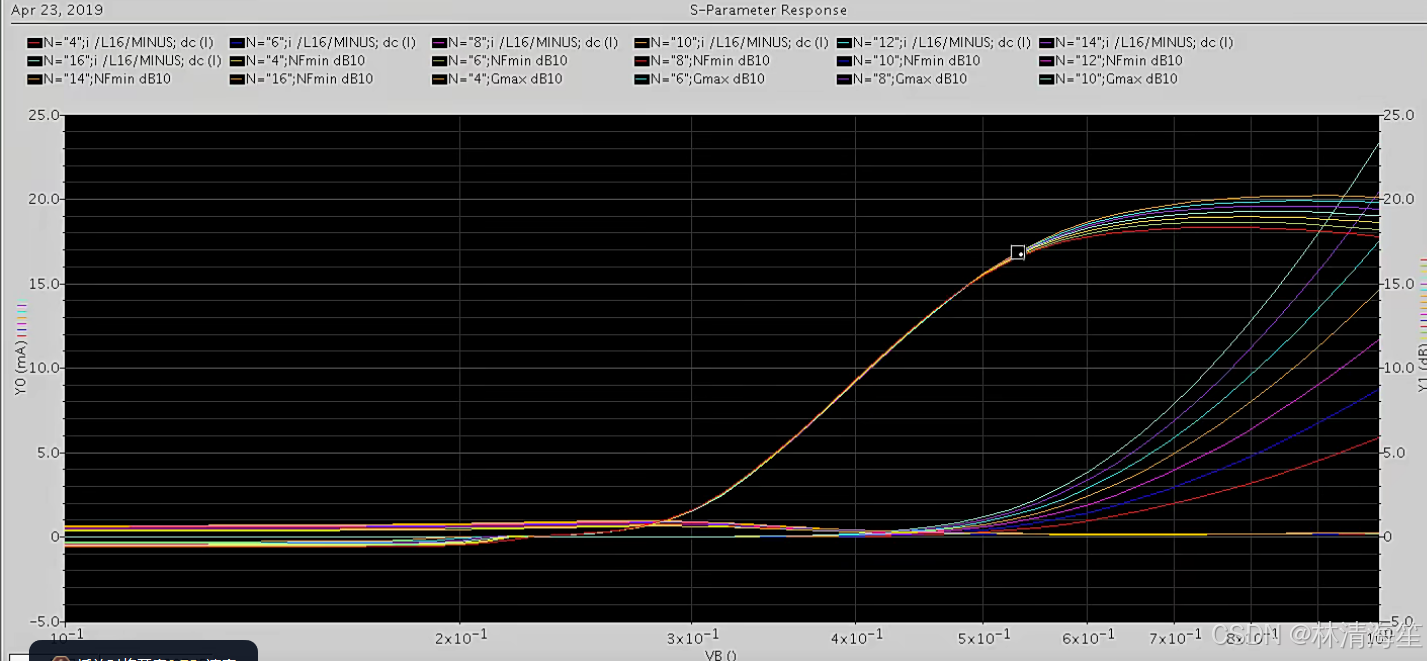

(最大功率增益Gmax)

- 由于目前没有做任何的匹配,主要看最大的增益Gmax

- 这里我们得到了最大功率增益Gmax和最小噪声系数NF的曲线

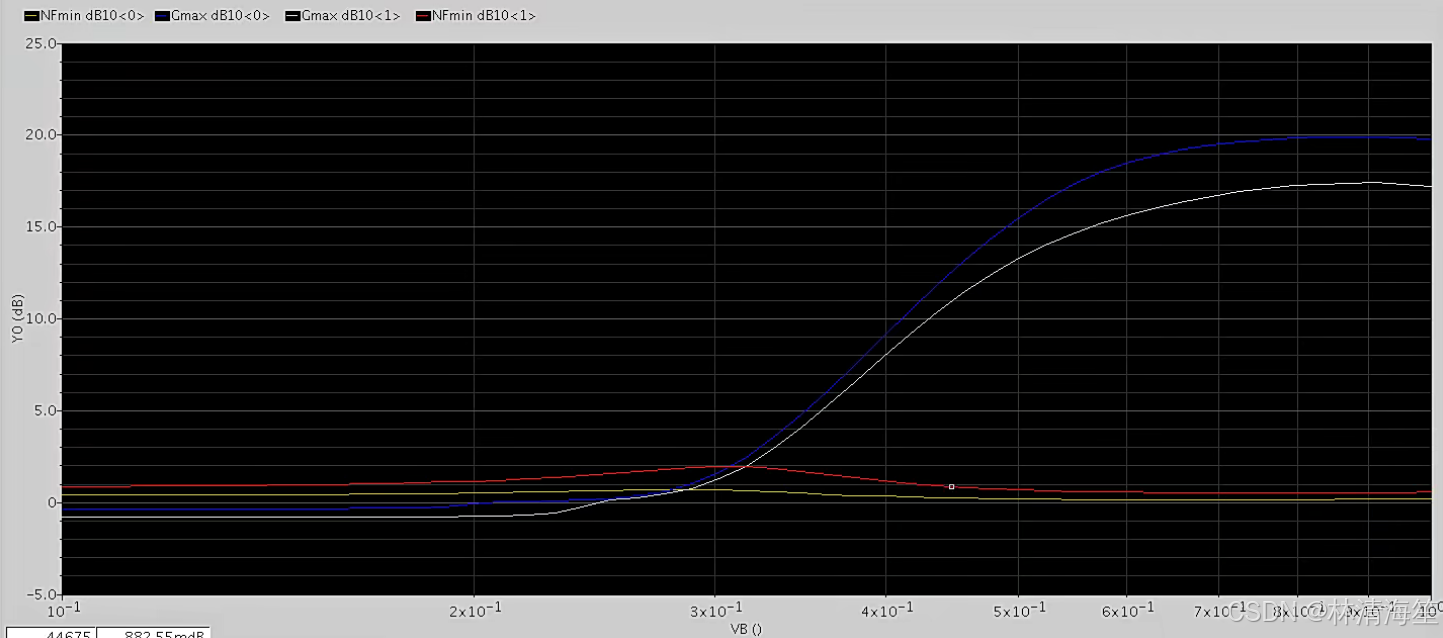

- 当我们改变沟道长度的时候,改为300nm

- 沟道长度加长后,晶体管总的宽长比就变小了,所以增益是会下降的。最小噪声系数NF也变高了

- 对于射频电路设计,特别是低噪放,一般都是选择最小沟道长度来设计的,所以这里我们改回最小沟道长度130nm

(3)晶体管的参数设计

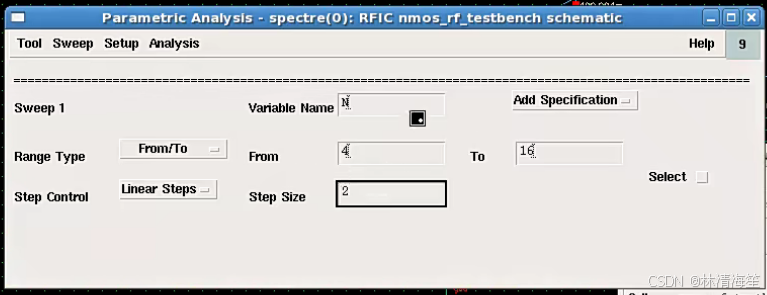

- 这里我们需要进行额外的变量参数扫描分析

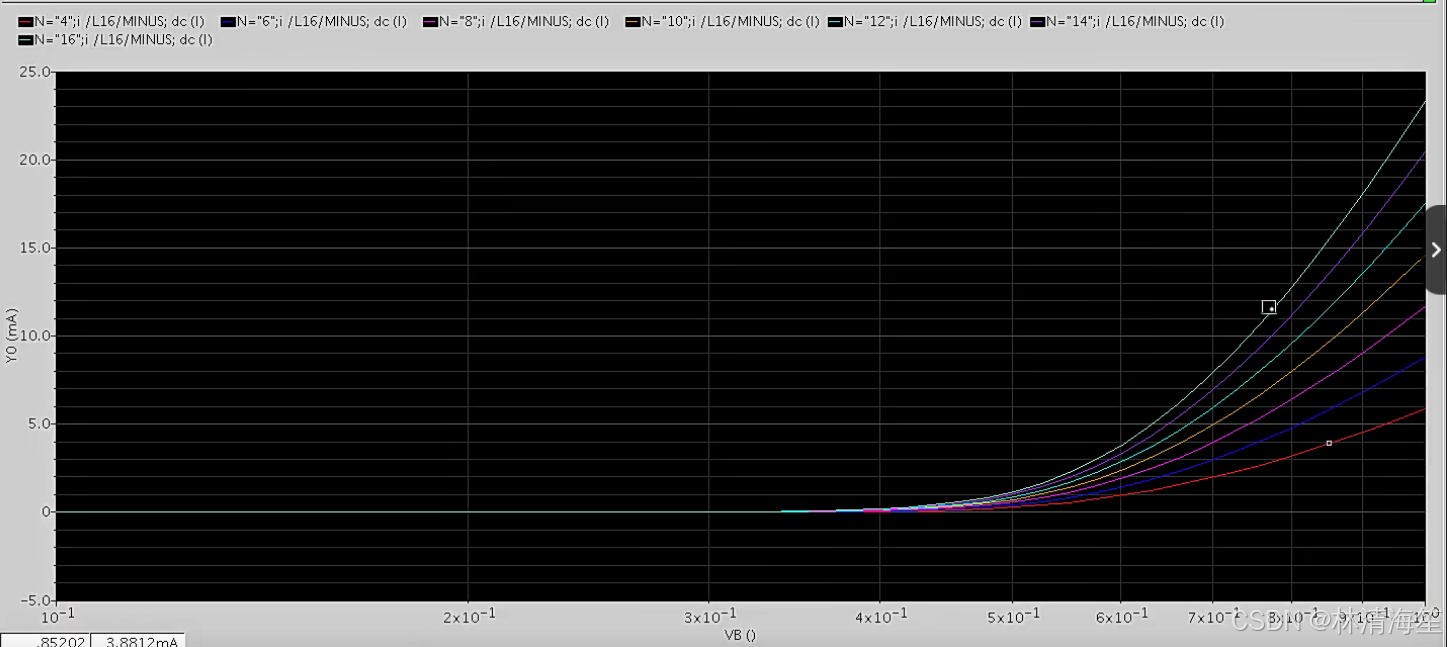

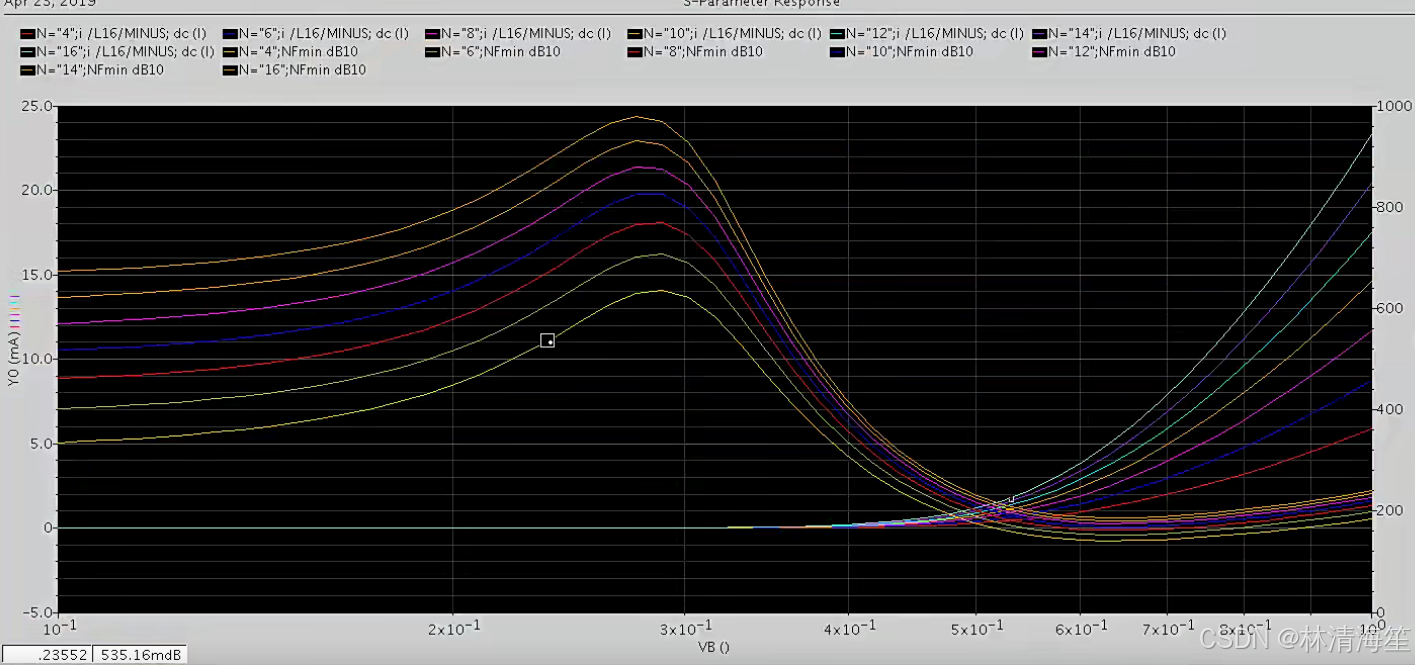

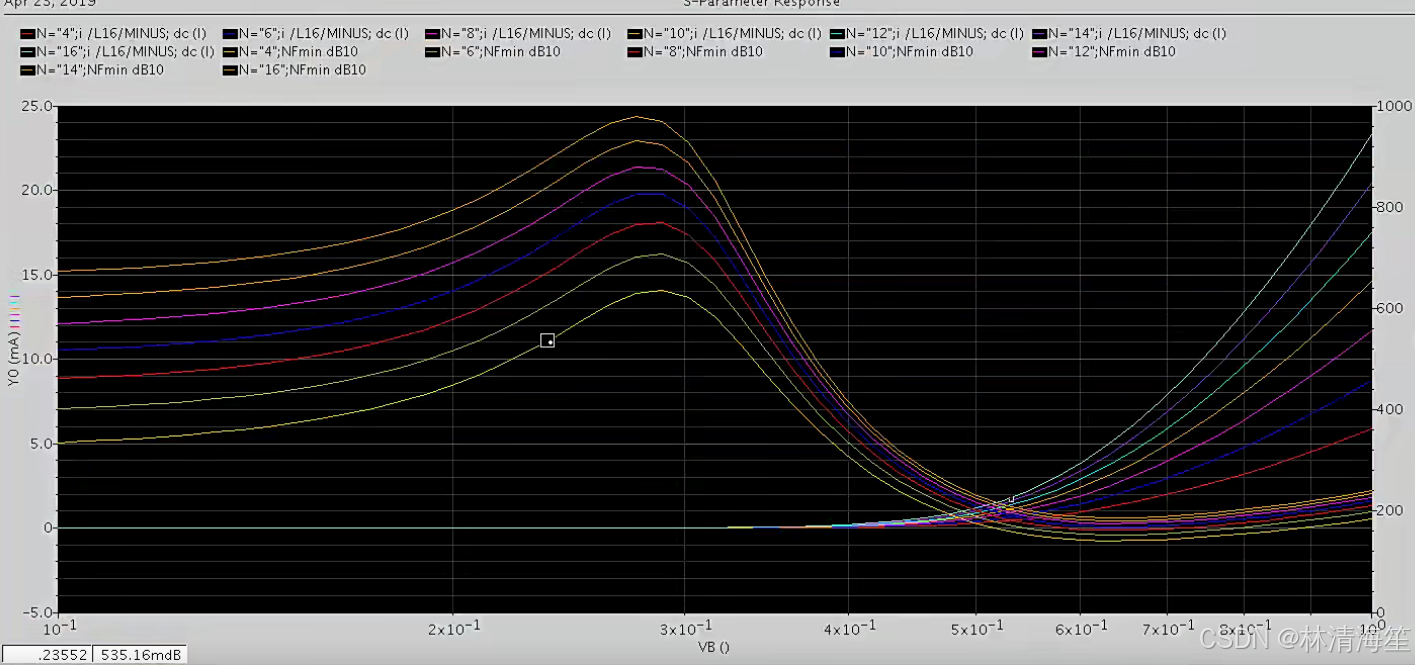

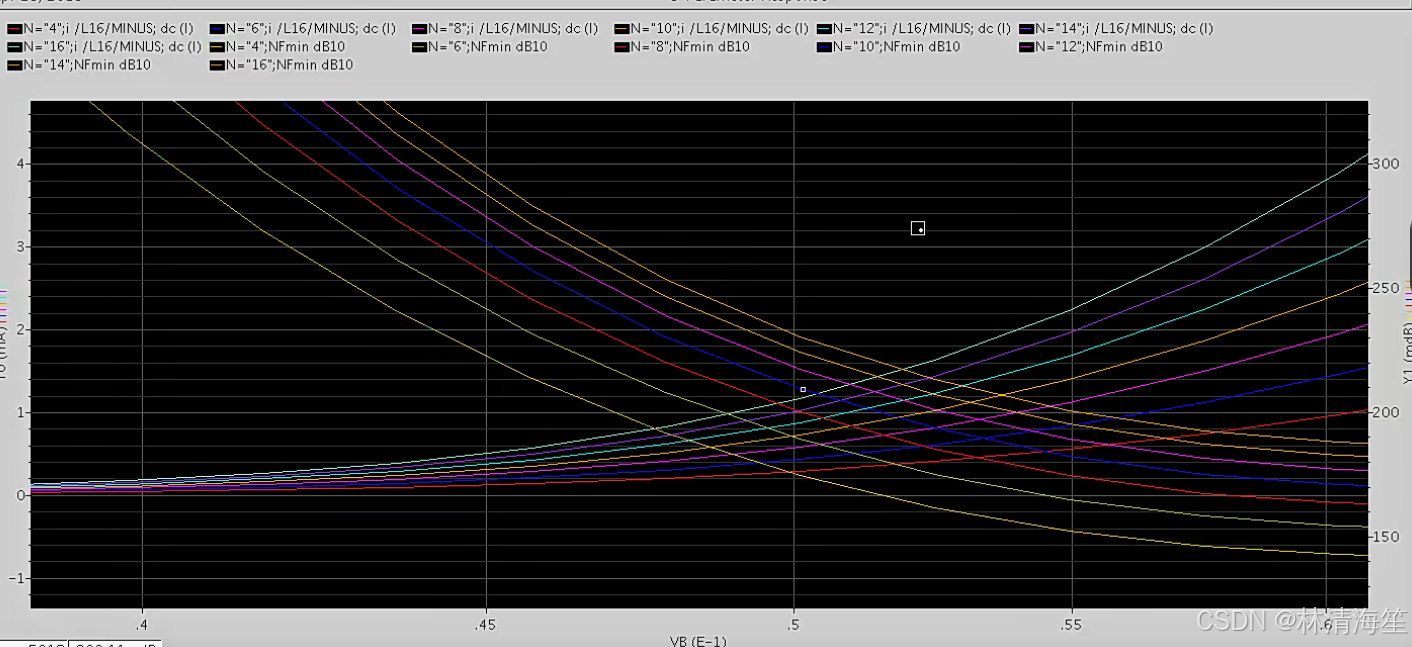

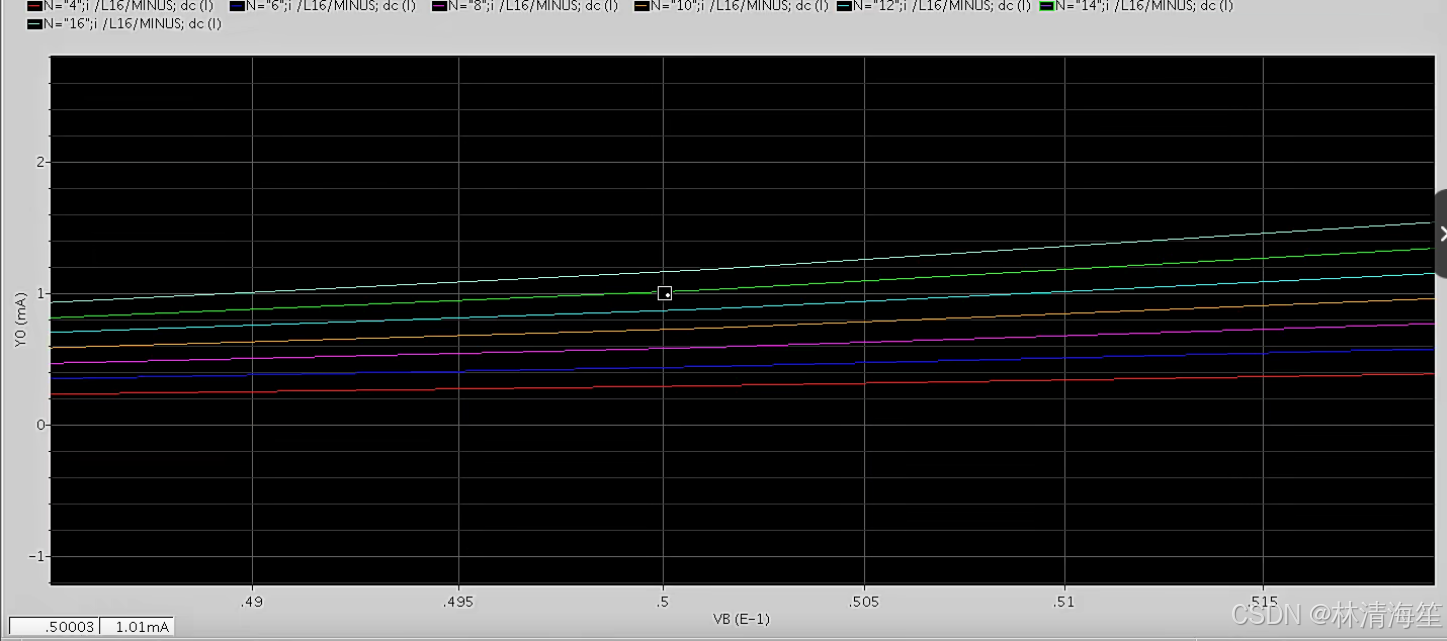

- 然后我们查看扫描后的曲线

- 先查看晶体管漏端的直流工作电流

- 最小噪声系数NF,随着N的增大,NF是越来越大的,

- 最大功率增益的重合度较高,

- 晶体管尺寸越小,寄生参数也会越小,在高频下放大性能会相对好一些,

- 不同尺寸的晶体管,在相同的栅极偏置电压下,最大功率增益是差别不大的

- 我们优先考虑工作电流和噪声的因素

- 随着栅极偏置电压的提高,电流功耗也会越来越大的。

- 设计指标要求晶体管的工作电流要小于2mA,由于低噪放电路有单转双电路,类似差分电路分成两部分,每边的电流是相等的,都为1mA。所以晶体管的偏置电压选择上要确保晶体管的电流不超过1mA。

- 在最小噪声NF曲线中,可以发现在0.6v左右实现最低NF值。但是0.6v的偏置电压太高了,此时电流太大了,达到1.3mA。

- 因此总体要折中进行考虑。把功耗降下来,把栅极电压减小

- 放大波形图可以发现,在相同偏置电压下0.5v-0.6v,最小噪声系数NF随着晶体管尺寸变化是非常小的,处于最低点附件。所以我们这重点考虑功耗的问题,在噪声系数NF相对较小的值下

- 我们查看在0.5v左右的偏置电压下,漏端电流是在1mA以内

- 我们发现N=14的时候,电流基本到1mA左右。

- 选在1mA左右是因为电流越大,线性度会越好。通常让功耗稍微大一些来满足整体的线性度的要求。

- 所以我们将N=14,单个finger的沟道长度为130nm,宽度为5um。这是初步选定的晶体管尺寸和偏置电压。

- 那么单个晶体管仿真参数,扫描设计就完成了。接下来的步骤是进行基本的电路结构的搭建和初步的仿真分析和优化的过程。

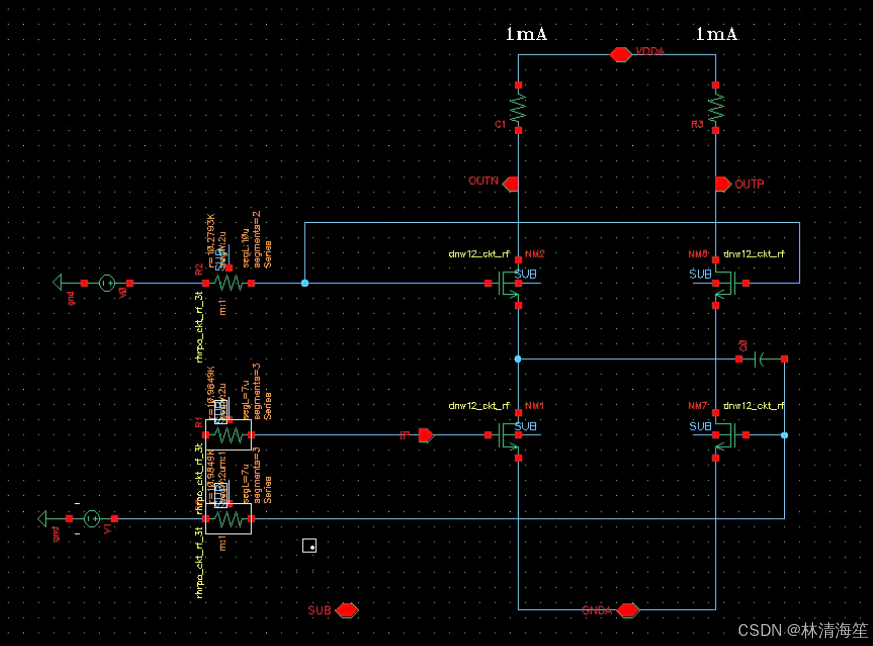

2. 电路搭建

- 打开已经提前搭建好的电路结构

- 可以看到有两个差动输入晶体管,和cascode两极的晶体管,还有差分的负载电阻,以及电源、输出的正负pin、射频输入的单端接口

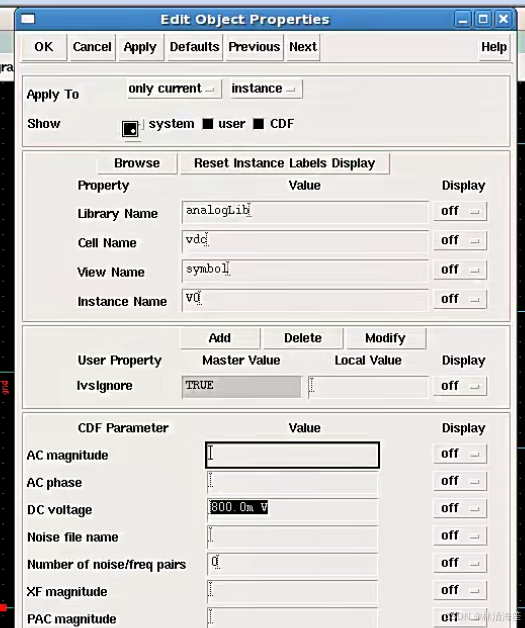

(1)输入偏置电压源参数

- 输入理想的输入电压源,电压值为500mV的VB栅极偏置电压

- cascode理想的输入电压源,电压值为800mv的偏置电压

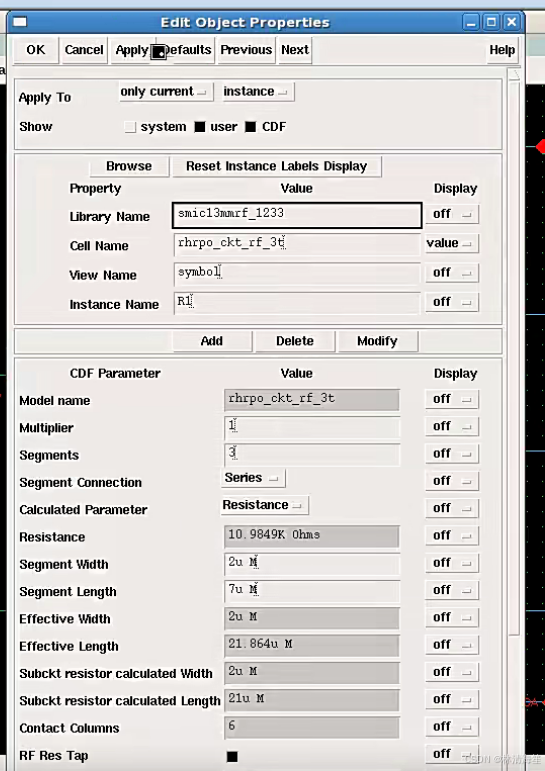

(2)输入隔离电阻参数

- 电压输入进来有隔离偏置的电阻,阻值为10k欧,即减少偏置电路对射频电路的干扰和影响

- cascode的输入电阻也是10k欧

- 这里面是串联了3个电阻(segments)的。

(3)晶体管参数

- 晶体管的尺寸全部统一,减小弥勒效应,finger数量设置为14

1037

1037

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?