一、MOSFET

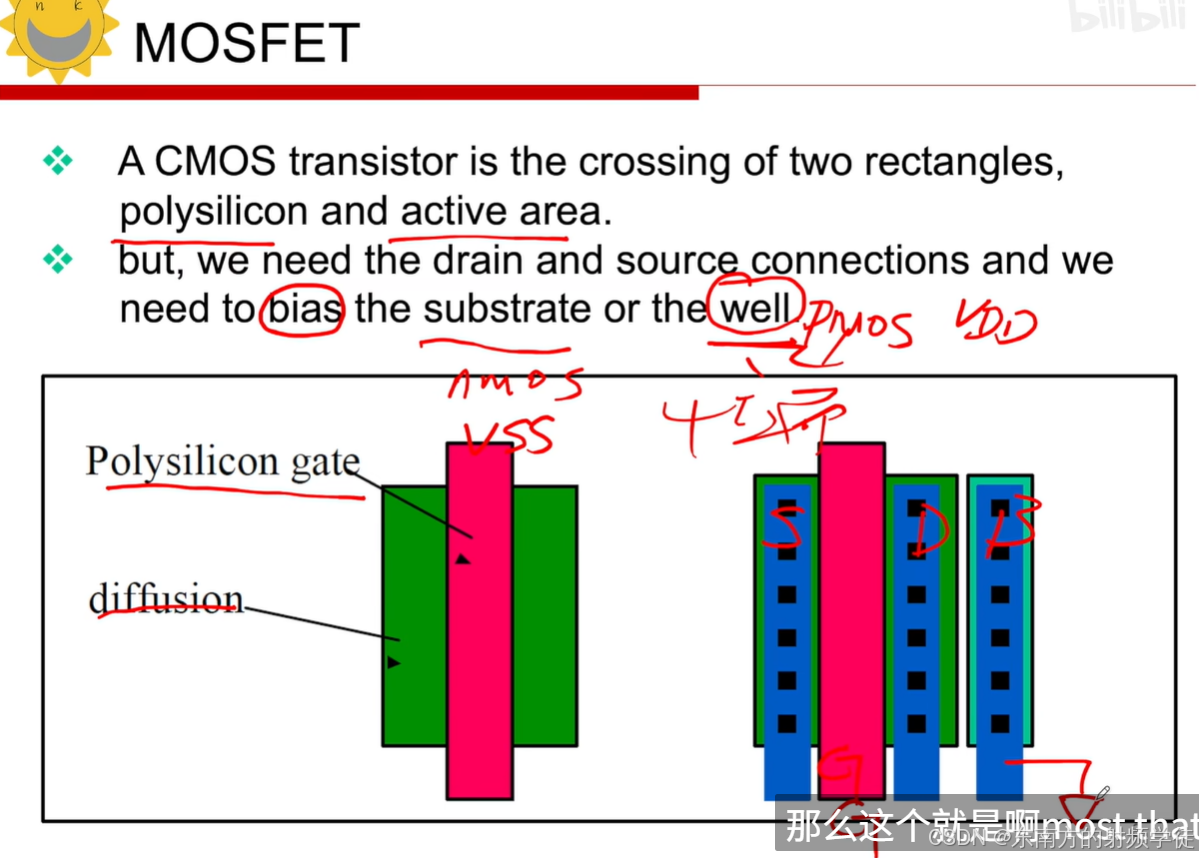

- 在版图设计中,要定义一个mosfet,最关键的层次是polysilicon(多晶硅)和active(有源区)。用有源区定义了一个矩形的区域,在这个区域内才可以形成一个有源器件,然后再用多晶硅画出的矩形与有源区进行交叠,这样就形成了器件的核心区。

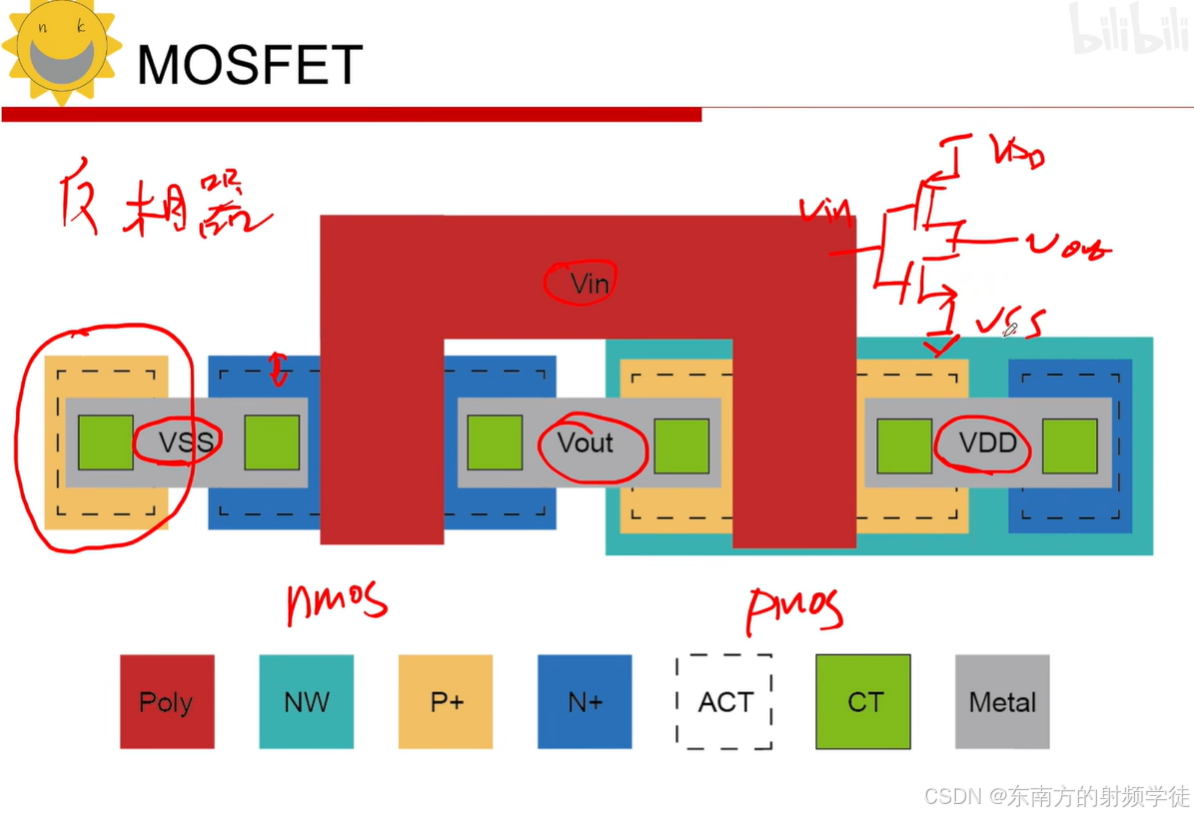

- 下图中,绿色区域是有源区,上面还要覆盖上一层掺杂(diffusion),这样去定义其源漏区。然后再交叠上polysilicon gate(多晶硅栅极),这样mosfet器件的基本结构就出来了。

- 之后我们要将其源漏和衬底进行互连。

- 此外,我们要注意,将衬底(nmos的p衬底)或者阱well(pmos的nwell)进行合理的偏置,即接到相应的电源或者地上。

端口的可靠连接

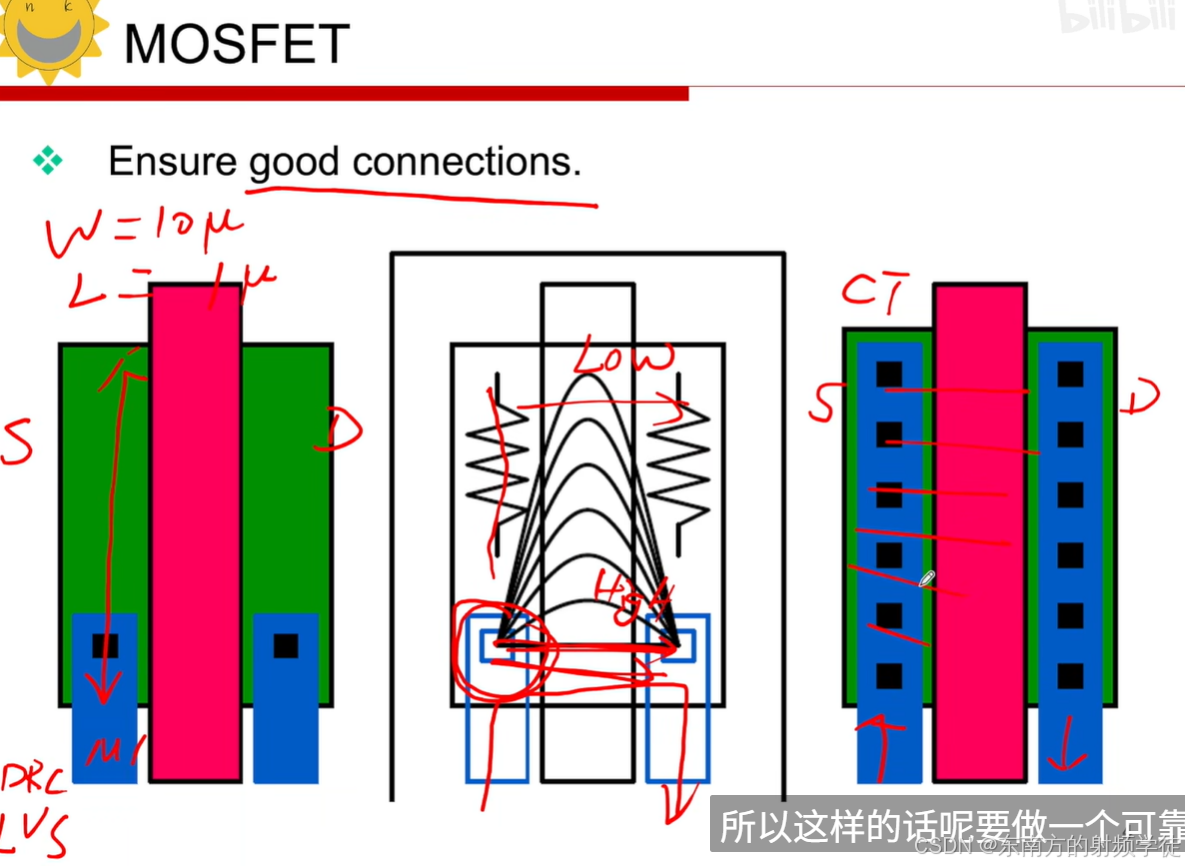

- 当我们做好mosfet的基本结构之后,一定要有可靠的连接。

- 如果一个mosfet的漏源区比较长,然后需要把漏源区进行连接,则要借助contact连接到M1上。如果只是在边缘处用一个过孔进行连接,DRC和LVS检测都是不会出现问题的,因为确实是连接上了。

- 但是这种连接是不可靠的,因为整个源漏区都是通过掺杂连接在一起的,阻抗是比较高的。假如把这种不可靠连接的晶体管作为开关,电流要流通这个晶体管,会导致有金属连接的区域电阻比较低,而越往里的电阻较高,电流会趋向于在有可靠金属连接的区域流动,因此电阻低的地方电流密度大,电阻高的地方电流密度小。这会很大程度上影响晶体管的特性,因此一定要做可靠的连接

- 我们要把源漏区均匀的覆盖上contact,把整个源漏都用金属M1进行覆盖,这样整个源漏区的电位基本上是统一的,因为金属的电阻非常低,做到比较低的压降,电流在晶体管内是均匀分布的。

大宽长比晶体管的问题

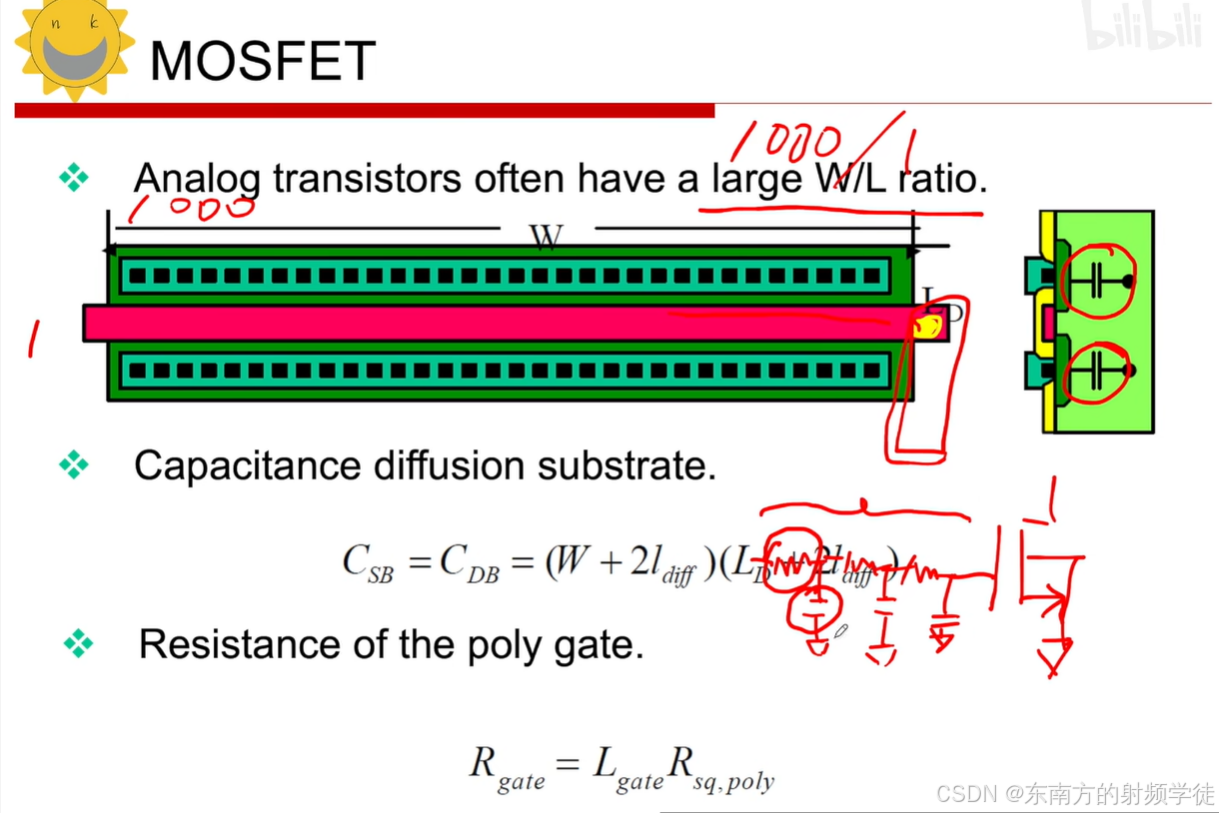

- 当我们在绘制非常大宽长比的晶体管的时候,比如在设计低噪声放大器的时候,输入晶体管会比较大,比如1000/1宽长比,其L=1um,W=1000um,这个晶体管是一个细长的线条,这会导致两个问题

- 问题1:源漏区的面积会非常大,导致源漏的寄生电容会非常大,因为源漏区和衬底之间时会有一个反偏PN结的,就会出现势垒电容,其容值和源漏区的面积相关。

- 问题2:gate会特别长,由于gate需要通过contact连接到金属上,然后在gate另一端用contact连接出去。但是由于gate的寄生电阻和电容是比较大的,当信号从contact传输进去的时候,会出现RC分布延时的问题,相当于是栅极上串联了很多个RC的分布式模型。如果gate比较长的话,则RC的分布式模型也会特别长,那么信号从栅极输入进去,出来肯定会出现一个畸变,如果信号频率特别高的话,很可能出来的控制信号已经消失掉了。(问题2比问题1更严重,因为gate的寄生导致传递信号的速度跟不上了)

- 有一种解决办法是,在gate上多打上contact,像漏源区一样,然后用整个金属把gate覆盖上,实际上信号是通过金属传递到一段一段的gate上的。这种办法在理论上是可以解决这个问题的,但是在design rule不允许在沟道上方画contact的,主要是因为沟道是一个比较敏感的结构,容易影响到沟道的电学特性。

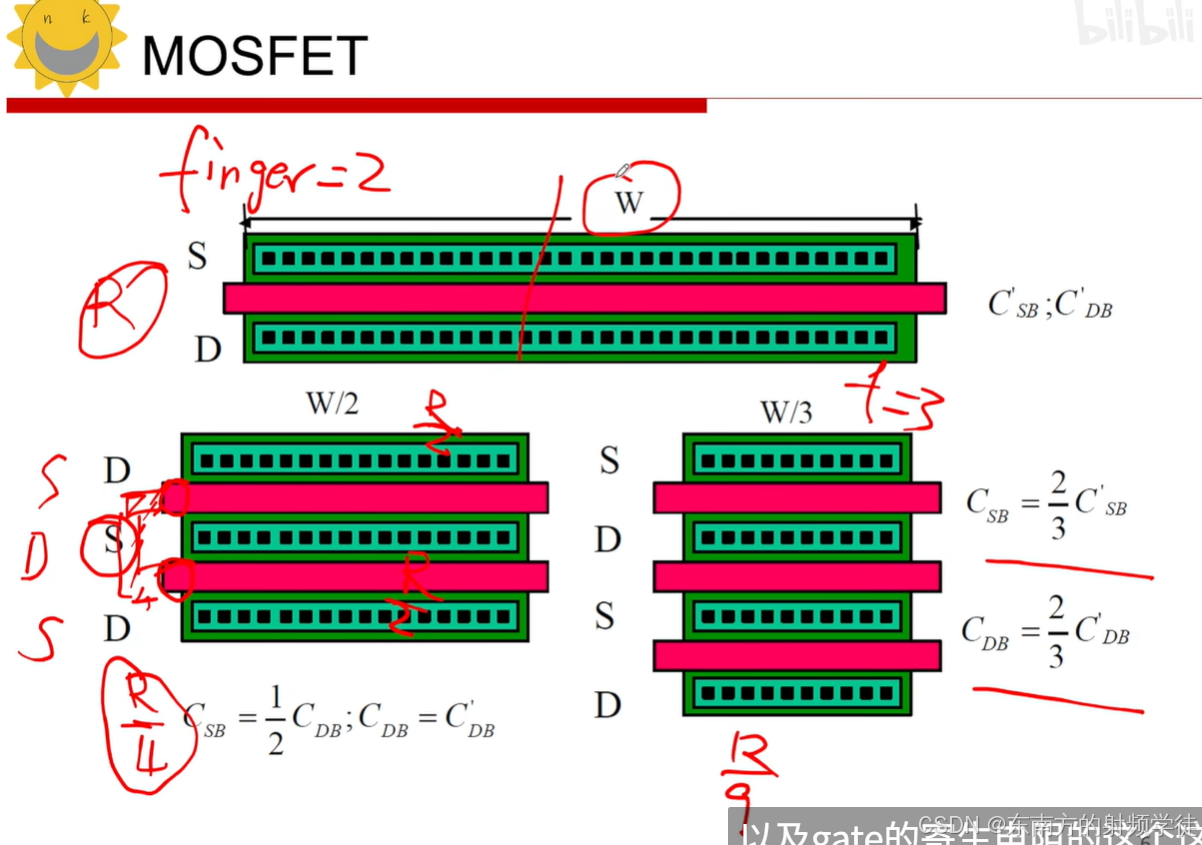

- 在真正去画版图解决大宽长比晶体管的问题,通常采用finger

finger

- 拆分晶体管为漏源漏的方式。

- 当finger为2,原来源的长度变为原来的一半,源极的寄生降低了,漏有两个,因此原来漏的寄生并没有变化。gate被拆成两截,因此我们可以在不同截的端口处打上contact,用金属将他们给并联起来,相当于原来gate的寄生变小了,降低了4倍。

- 当finger变为3的时候,源漏源漏的结构,那么源漏的寄生变为原来的1/3,gate变为原来的1/9。这样gate的寄生电阻将会很大程度的降低。

- finger数越多,gate的寄生就会越小

MOSFET版图的示意图

- 下图是一个反相器的版图示意图,左侧是NMOS,右侧是PMOS。

- 左侧的NMOS用有源区(黑色虚线框)包围了,有源区外有N+(蓝色区域)的注入,即N+要enclosure有源区。然后用gate poly覆盖住有源区的中心位置,形成沟道区,并在两侧画上contact,再用金属连接出去,

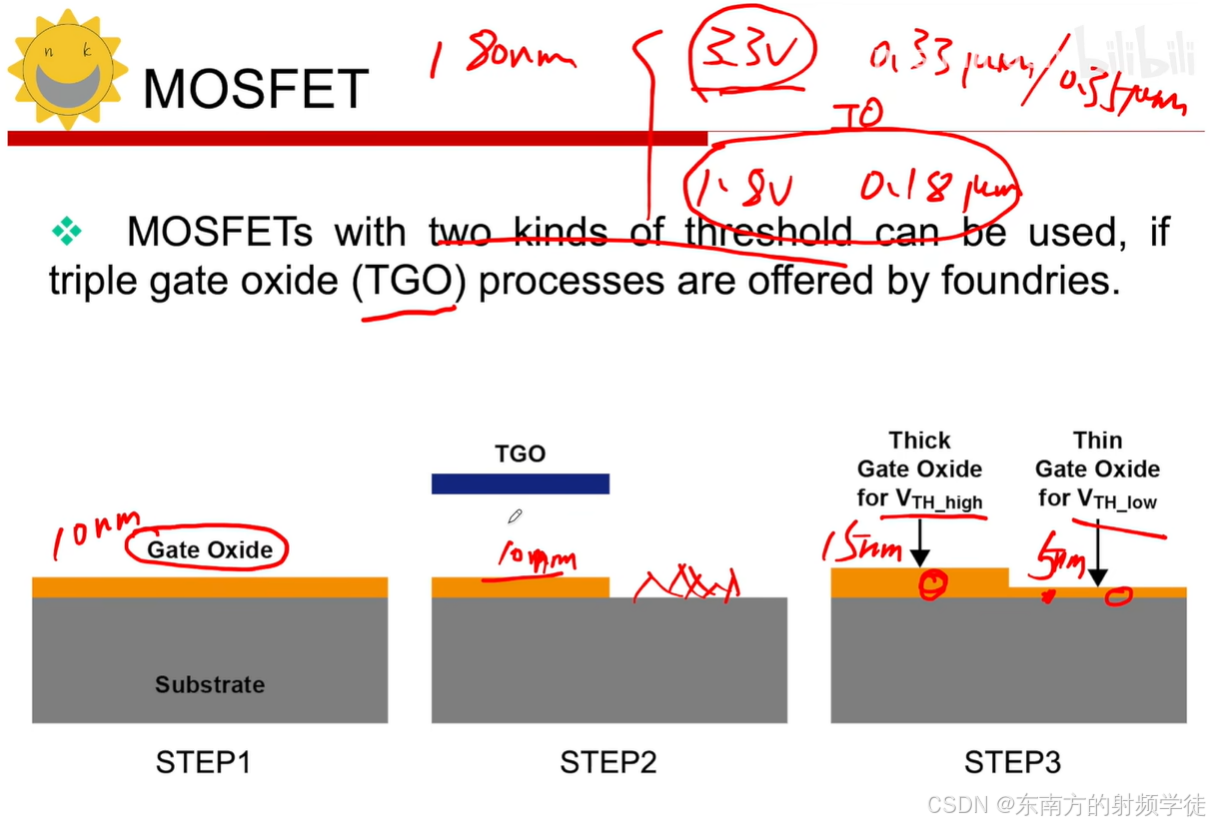

TGO(triple gate oxide)

- 这个工艺主要是为了提供两种不同阈值的晶体管。通常一个工艺中会提供两种不同阈值的晶体管,一个是高阈值,一个是低阈值。高阈值的栅氧厚度要厚一些

- 低阈值的栅氧会很薄,其承受的电压比较低,器件尺寸也会比较小,工作电压也可以更低,这样可以减小功耗,也可以节省面积。一般数字电路常使用这种低阈值的器件;

- 但是模拟电路比较喜欢用具有高本征增益的器件,那么其沟道长度会比较长一些,尺寸也较大;此外为了信号幅度更宽(承受更大的噪声,信噪比更好),但是带来的牺牲就是功耗和面积。或者IO接口电路

- 这就需要一个新的光刻板(TGO)。

- 做栅氧首先会在全芯片上都长出一定厚度的gate oxide,然后再加入TGO这一层光刻板,将TGO以外的栅氧给刻蚀掉。然后再在整个wafer上生成一遍较薄的栅氧

- 由于整个器件经历了三个步骤,因此叫triple gate

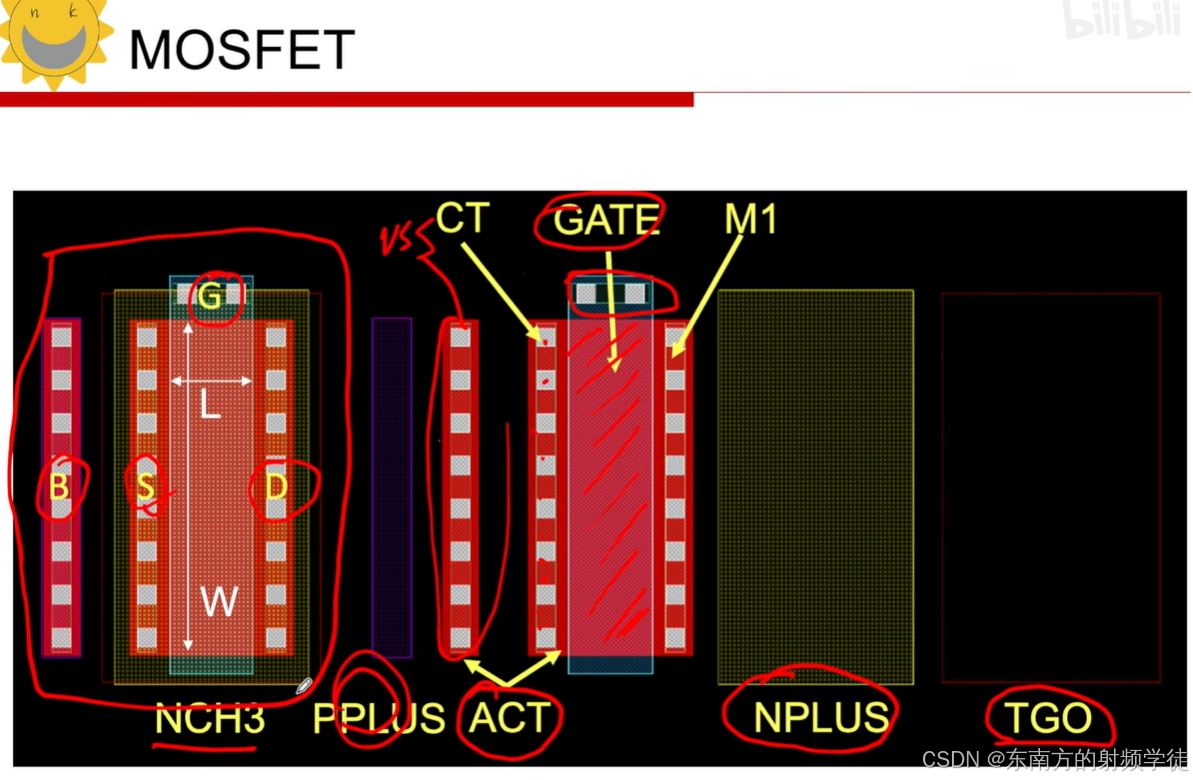

典型NMOSFET版图

- 左侧是完整版图的形状(NCH3),然后把所有器件都大散拆开,看下里面有哪些层次。

- 有源区(active)和栅极(gate)交叠,就构成了沟道区,然后在整个区域覆盖上n plus(n+注入),就定义好了源漏。然后使用contact做可靠的连接,在源漏区均匀覆盖上contact,再使用M1进行连接。

- 还有TGO层的layer,意味着这是高压的厚氧化层的器件。

- 不同工艺器件名字不一样,比如这里的NCH3,表示n channel沟道的mosfet的3.3v的器件。

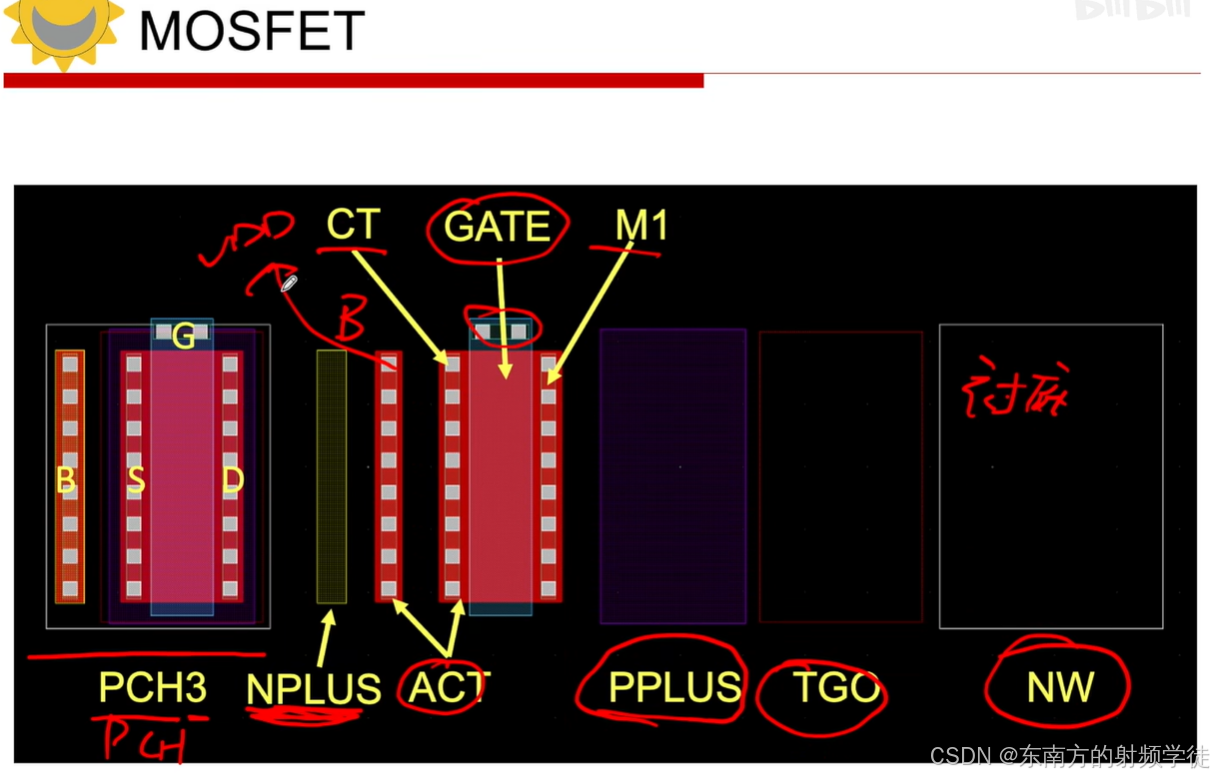

典型的PMOS版图

- PCH3,表示p channel沟道的高压器件,3是高压的

- 核心区域和nmos都是一样的,但还覆盖p plus(P+注入),

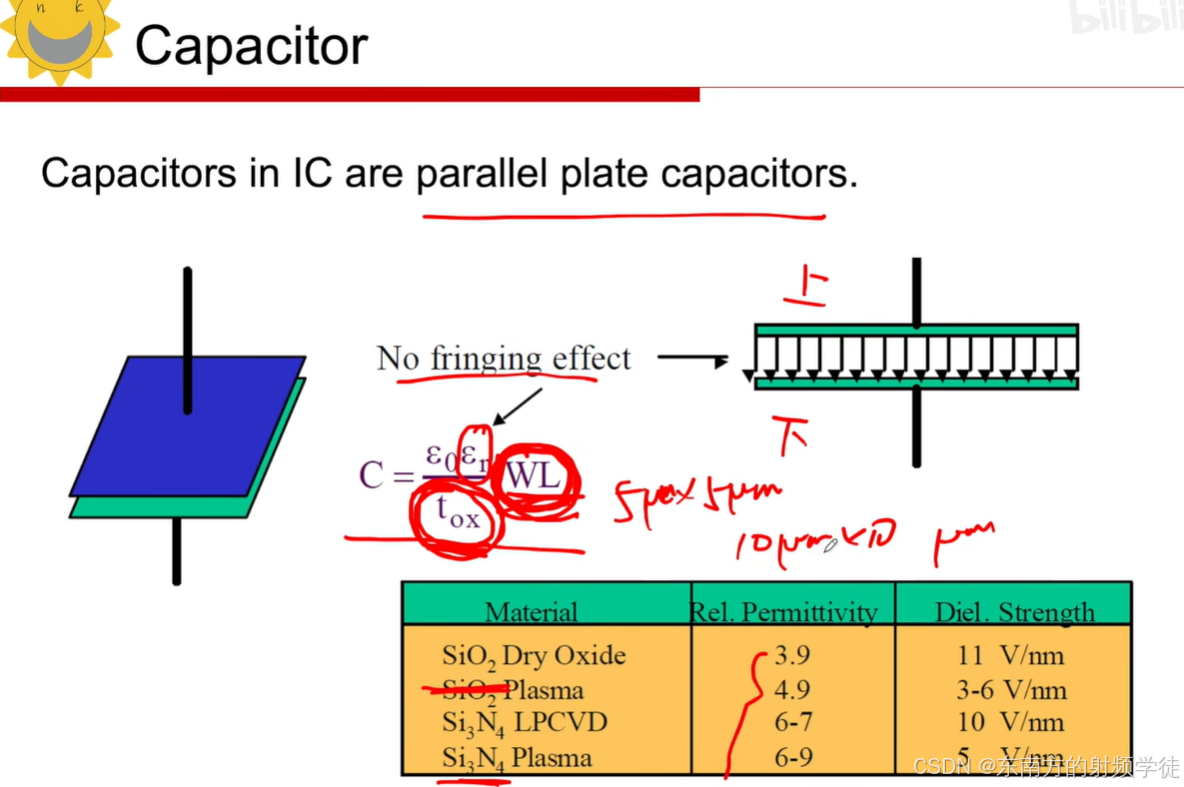

二、电容Capacitor

- 最简单的电容是由两个平行的金属板,中间夹着绝缘的介质层,这两个板就成为了电容的两个电极。

- 在集成电路中,通常的绝缘介质是二氧化硅,或者是氮化硅(Si3N4)。所以在选择好工艺之后,相对介电常数是固定的。

- 对于设计者来说,能改变的只有氧化层的厚度tox,还有金属板的面积W*L

- 厚度tox也不能去灵活去改动,但可以去选择,一般一个工艺会提供不同的厚度

- 所以更多的是去改变金属板的面积

IC电容类型

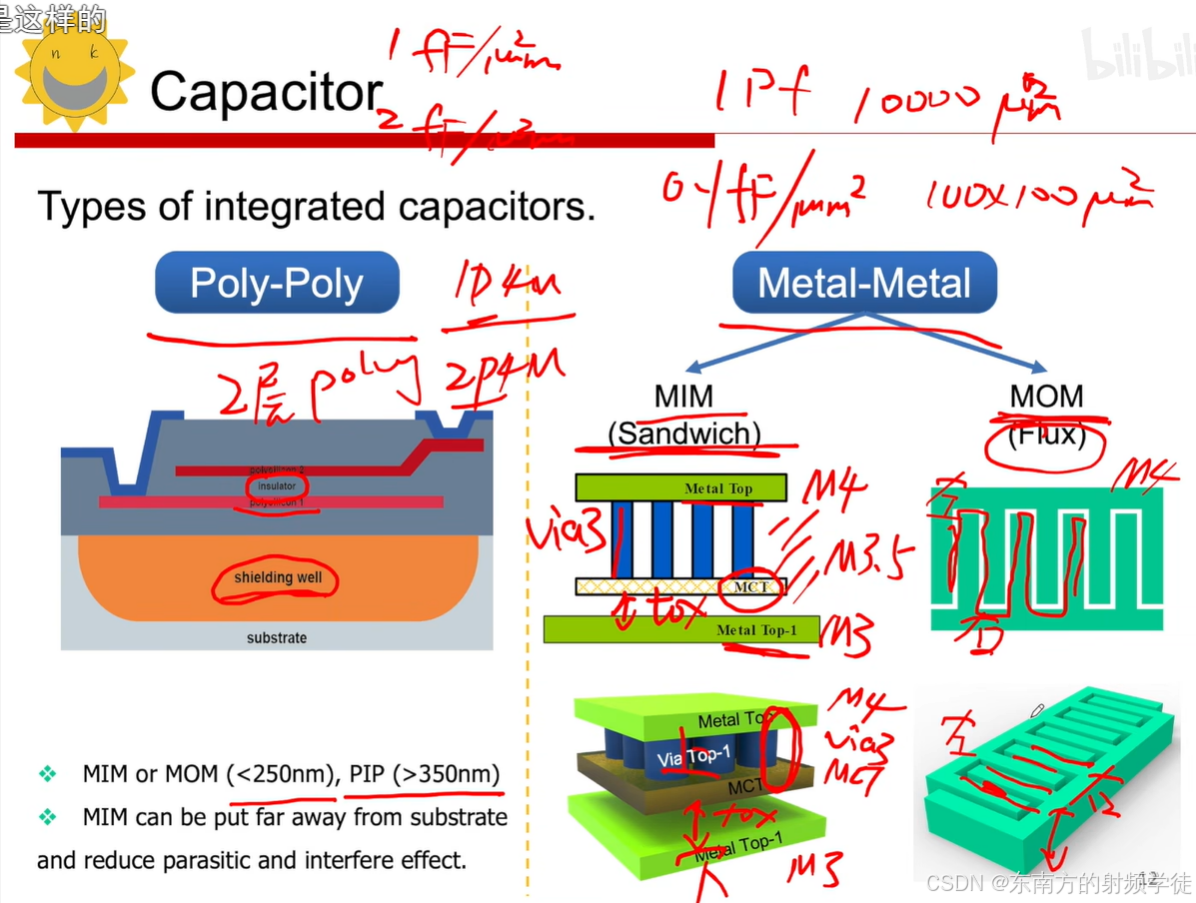

- 集成电路中的电容主要有两大类

- 第一类是poly to poly。是两个poly之间形成的电容,电容上下极板都是poly,中间夹着isulator绝缘介质构成的电容器件。

- 意味着需要有两层的poly,比如像1P4M工艺是做不了的,因为只有一层poly,像2P4M工艺才有可能提供poly-poly电容。

- 但这种电容一般是在特征尺寸比较粗的情况下(大于350nm工艺)

- 这种类型的电容存在一些问题,由于poly与衬底离的比较近,对衬底的寄生是比较大的,串扰是很难规避的。

- 这种天生的缺陷,因此要进行隔离(shielding well)

- 第二类是metal to metal。是两个金属之间夹着的绝缘介质,构成的绝缘器件。先进工艺使用的比较多mim和mom电容。

- 第一种是MIM电容(metal inter metal)金属-绝缘层-金属结构,类似三明治(sandwich)。

- 首先要有两层金属(metal top层金属和metal top-1层金属),如果只使用这两层金属做电容的问题是,产生的电容密度会比较小(单位面积下的容值),比较浪费面积。

- 所以只能降低绝缘层厚度tox了。工艺上会提供MCT层金属,可以理解为M3.5层,介于M3和M4之间,作为电容的上极板。然后通过通孔和Metal top层金属进行连接。MCT和M3之间是绝缘介质,形成电容。

- MCT层的位置是可以移动的,距离M3的高度可调节。通过移动,可以将厚度tox降到很低很薄,提高电容密度。这样就意味着一道工艺可以提供不同电容密度的电容。但是要注意MCT在加工过程中是全芯片的,只能是同一个MCT。所以这次流片只要选定好这个距离后,整个芯片的距离都是这个距离不能再改变了。一次流片不能提供两种距离

- 第二种是MOM(metal outside metal),这是flux(叉指)结构。即将同层金属做成这样的叉指架构交错在一起。他们是通过叉指中间的缝隙形成的电容。可以通过叉指的个数和叉指的长度控制电容的大小。

- 第一种是MIM电容(metal inter metal)金属-绝缘层-金属结构,类似三明治(sandwich)。

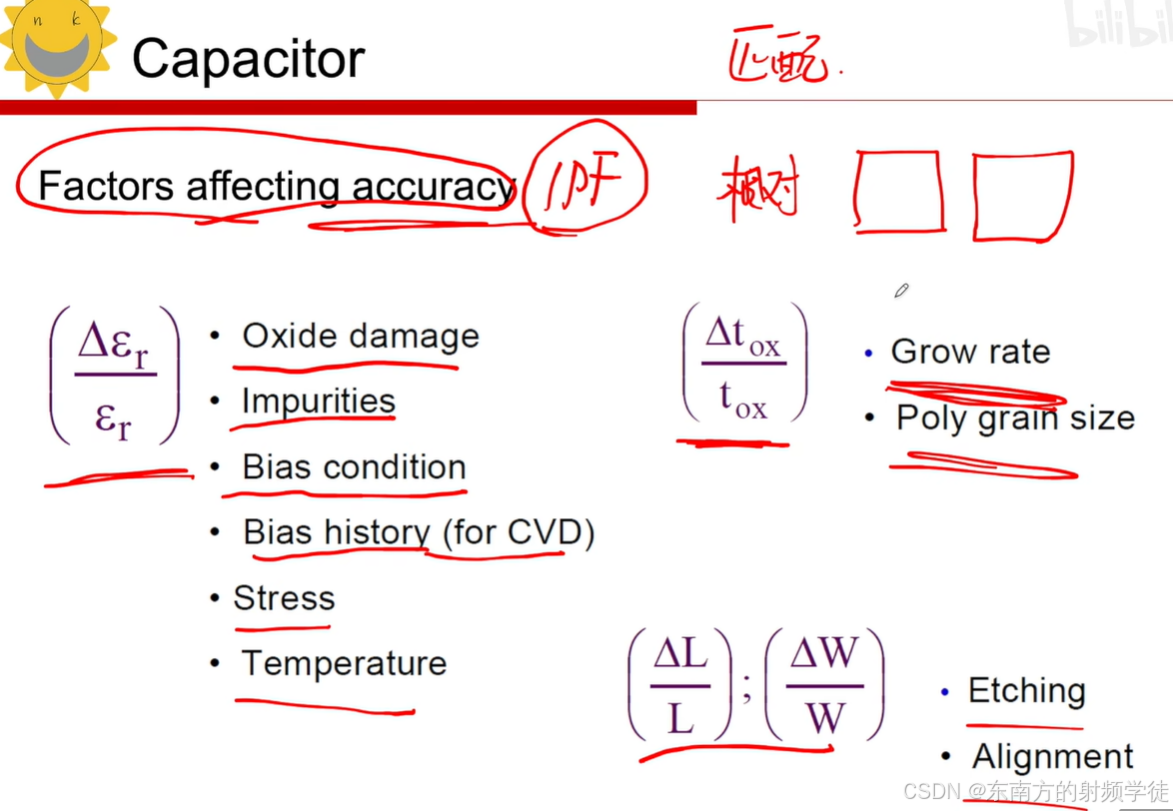

影响电容的精度

- 集成电路加工出来的电容是有一定的误差的,影响电容的参数主要有以下几种

- 第一个是相对介电常数。比如下面这些情况可能会产生影响

- Oxide demage(氧化层的损伤)

- Impurities(氧化层中的杂质)

- Bias condition(电容的电学偏置状态)

- 氧化层在淀积的时候用到的CVD(化学气象电机)

- stress(应力)和temperature(温度)

- 第二部分是氧化层的厚度(tox)

- grow rate(生长的速率)生长的快慢厚度会不一样

- poly grain size(精力的大小)

- 第三部分是金属板的宽和长,尺寸带来的变化

- etching(刻蚀)和alignment(对齐)带来的误差

- 第一个是相对介电常数。比如下面这些情况可能会产生影响

- 在集成电路中可以比较好的保证相对精度,即做两个电容的容值接近的程度

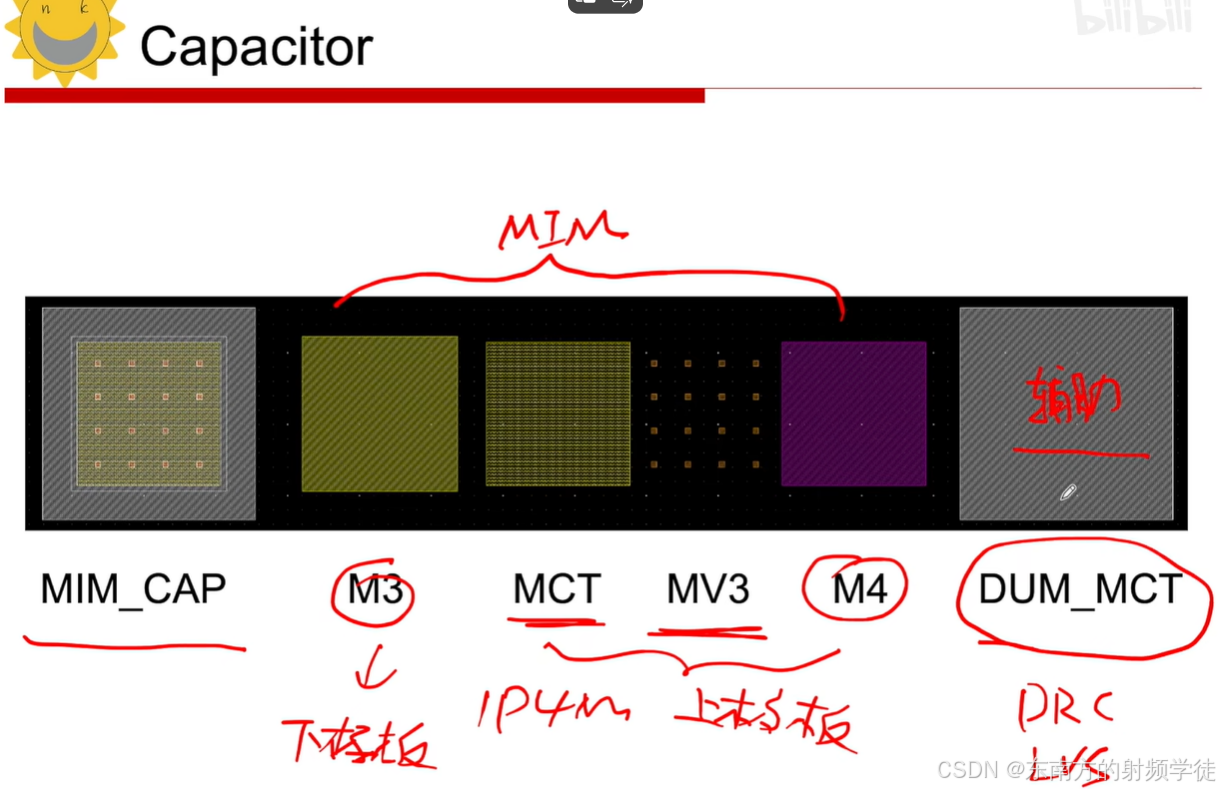

典型MIM电容的版图

- MIM结构类似三明治,所以有顶层金属M4,然后是MV3过孔,再下面是MCT,三层结合在一起构成电容的上极板,M3层金属构成下极板。这些layer其实已经可以构成MIM电容了

- DUM_MCT层实际上是辅助层,并没有真正的掩膜板mask与之对应。主要是为了让DRC和LVS工具能够识别出来这部分区域是电容。

三、电阻Resistor

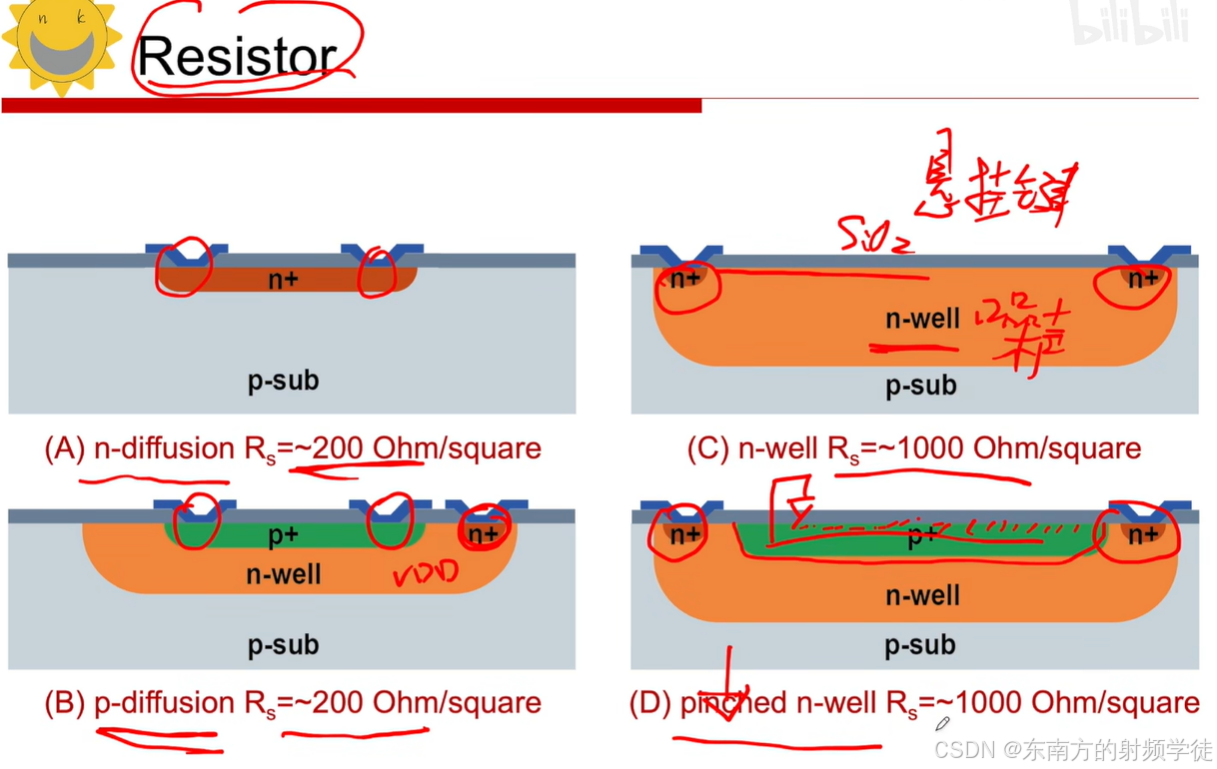

电阻的类型

- 在集成电路工艺中,电阻的类型是比较多的,

- 第一种是N+注入形成的电阻,实际上就是在P衬底上画一块N+注入,然后再两端用金属连接出去。其方块电阻大致为200欧

- 第二种是P+注入形成的电阻,首先得画上N阱,在N阱里面画上P+注入,此外N阱还要做N+的连接,形成合理的偏置到VDD上。靠注入形成的电阻,其方块电阻值一般都在200欧左右

- 第三种是N阱形成的电阻,画一块N阱,然后在两边画上N+注入连接出去。N阱形成的电阻较大,其方块电阻可以达到上千欧。由于第三种直接在N阱形成的电阻,其表面是wafer的表面(二氧化硅),所以这样的N阱表面的晶格是断裂的,就会有很多的悬挂键,就会成为失主或者受主,随机的释放或者捕捉电子,影响到噪声的特性,且电阻表面的电流是会有波动的,加剧电阻的噪声。

- 第四种是Pinched(前卫)N阱,即在N阱的表面加上P+的注入,把P+也接到VDD上。为了降低第三种电阻的噪声,在表面加入P+的注入,这样表面的噪声都通过P+流入到地上了,而且N阱和P+之间的晶格是完美的,没有缺陷,这样N阱的表面就不会有悬挂键了,就不会有因为悬挂键和表面缺陷造成的噪声了。但是方块电阻还是没有太大的变化,也是在上千欧的量级上。

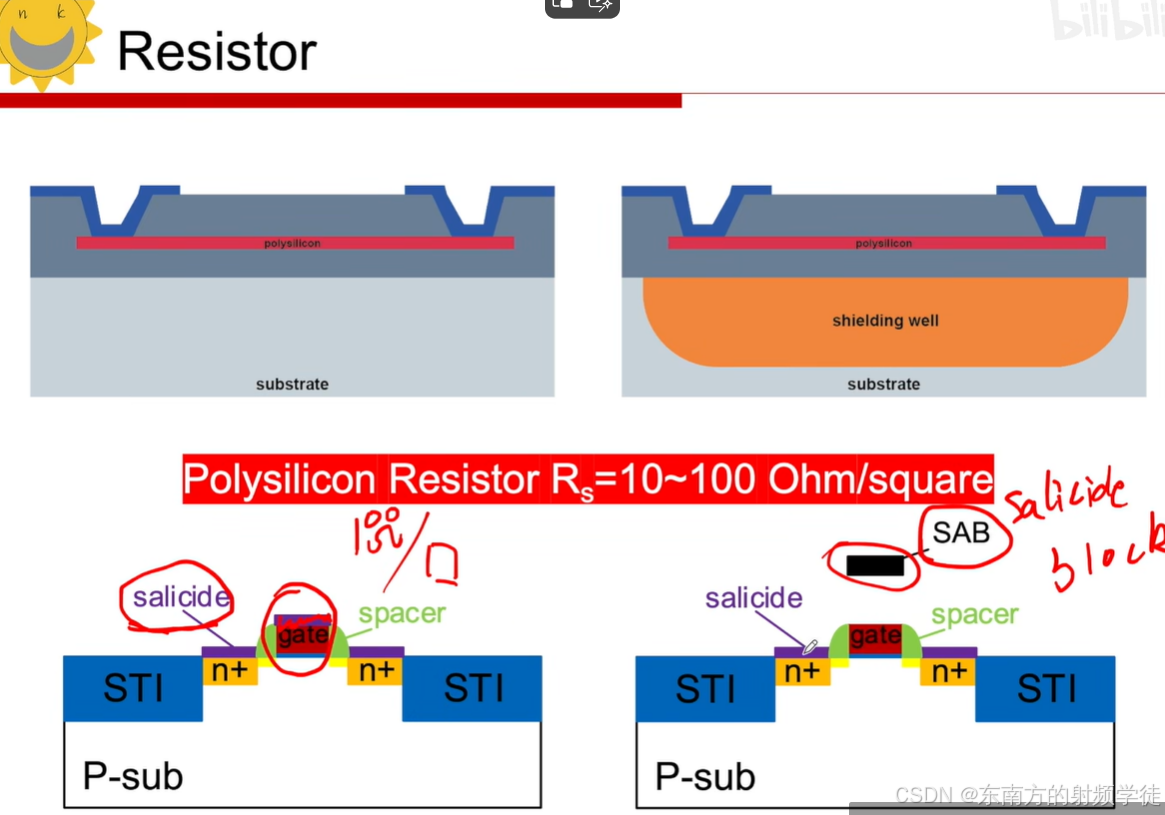

- 还有就是多晶硅(poly silicon)形成的电阻,然后在两端用contact连接出去,形成poly电阻。

- 为了屏蔽衬底下的噪声,也可以在poly层下面加上保护阱(shielding well)。

- poly型电阻分为有注入型和无注入型,因为纯poly的电阻太高了,所以一般还会在上面加上一层P+或N+的注入。

- poly类型的电阻的方块电阻值范围很大,取决于是否有注入和salicide。

- 此外还有salicide(金属硅化物)工艺,有了这个工艺可以进一步的降低电阻。

- 实际上在集成电路加工过程中,会把整个wafer都涂上salicide,然后再把具有电学连接的位置保留下salicide,剩下的都刻蚀掉。这意味着有源区上的源漏区和gate上面都是覆盖上salicide的。

- salicide是一种电阻率比较低的材质,覆盖上它的目的就是为了降低寄生电阻,让源漏之间的连接更好。

- 方块电阻值越大,占用的版图的面积就越小,希望gate层不要用salicide涂上。所以需要对gate做特殊的处理,有一个特殊的层次是SAB(salicide block)金属硅化物阻抗,有SAB的区域就不会加工salicide了,其他区域才加工。这样就能提升方块电阻

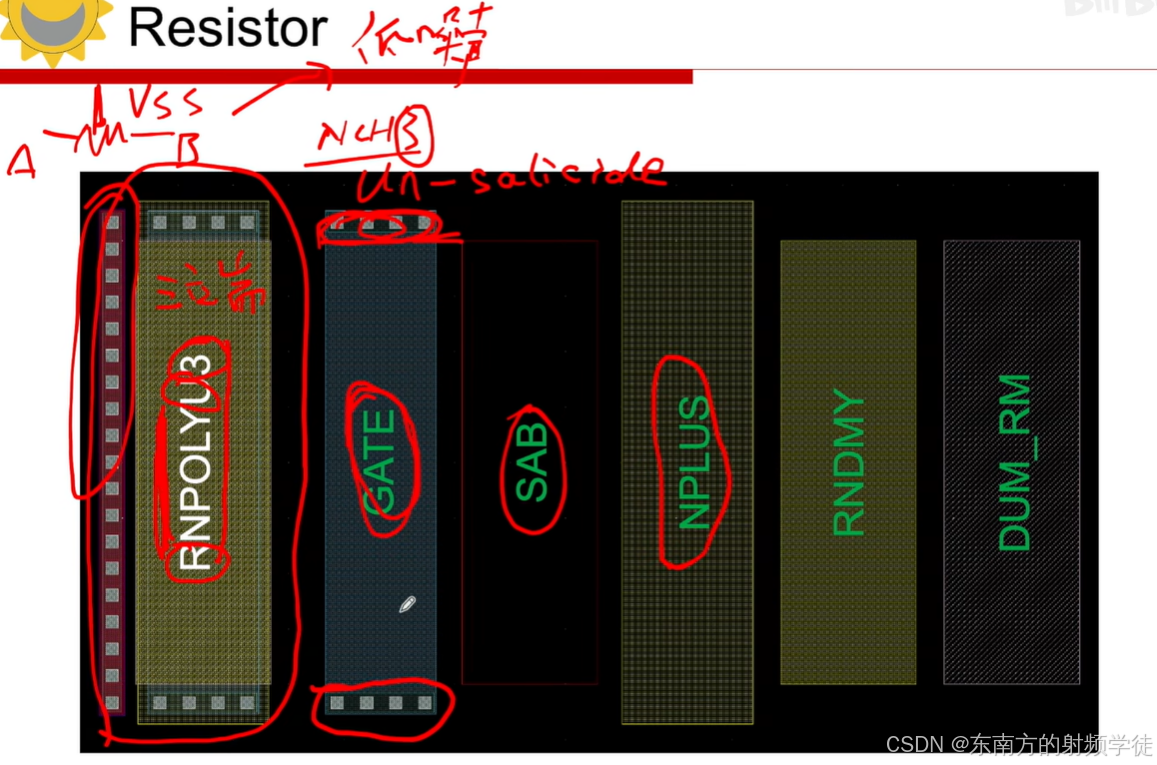

电阻的版图

- 左边的器件名字叫做r npoly U3,开头的r表示resistor电阻,npoly表示有poly且上方有N+的注入,U表示un-salicide(不加salicide)也就是电阻的gate poly上要画SAB,3表示三端口器件,第三端口主要为了接地,即这个电阻周围要做接地的处理,目的是为了让电阻下面的衬底电学特性更好一些,接地后底下的衬底不会有电压的波动,降低电阻的噪声。

- 拆开后有几个层次,gate层作为电阻,N+注入(Nplus)(电阻的两端也要有NPlus的覆盖,SAB不能覆盖到端口连接区),SAB增加方块电阻,这些层次在一起就可以构成电阻器件了。

- RNDMY和DUM_RM是作为辅助层次

6286

6286

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?