Chris射频IC教程学习笔记

1. 教程简介和BLE射频收发机系统结构介绍

2.1 低噪声放大器电路结构以及单晶体管仿真分析

2.2 LNA的testbench搭建及S参数仿真优化

2.3 LNA噪声、线性度及稳定性仿真分析

2.4 LNA增益控制,工艺角偏差,高低温对性能的影响

2.5 LNA完整电路设计及蒙特卡洛仿真

2.6 LNA版图设计及DRC/LVS验证

4 D类功率放大器PA电路设计/loadpull仿真/输出功率及效率PAE计算

(未完待续,还会继续更新)

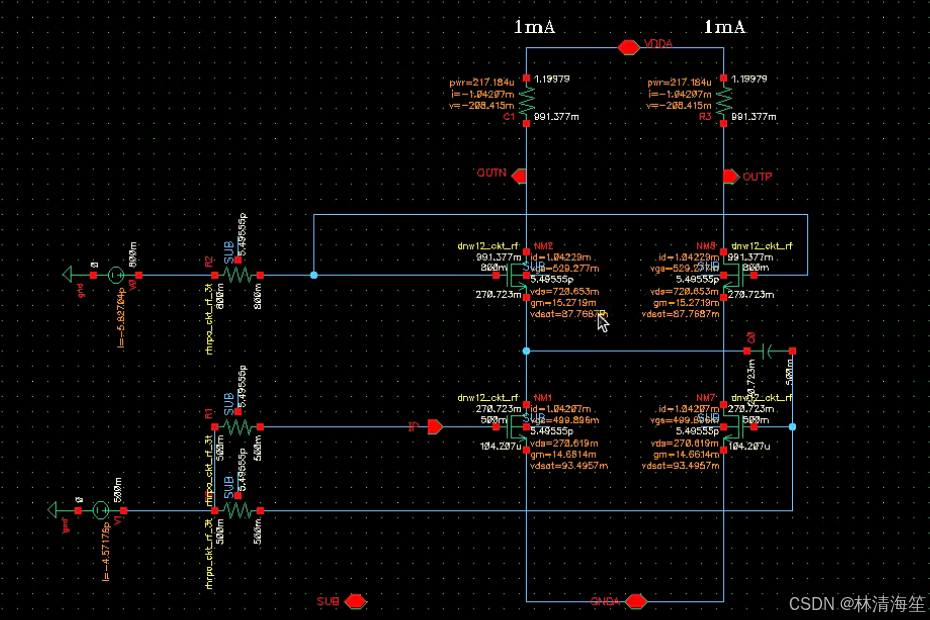

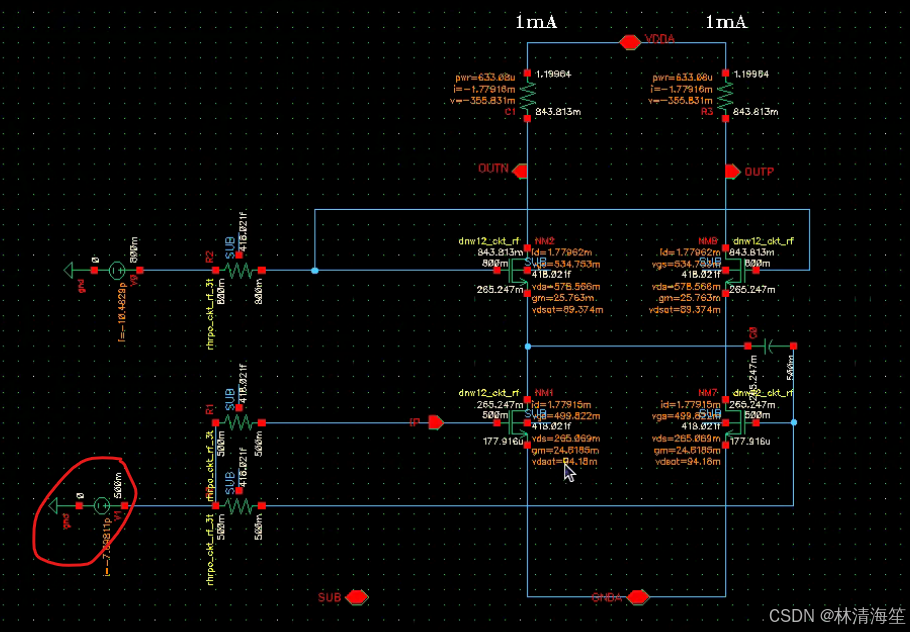

一、LNA核心电路设计

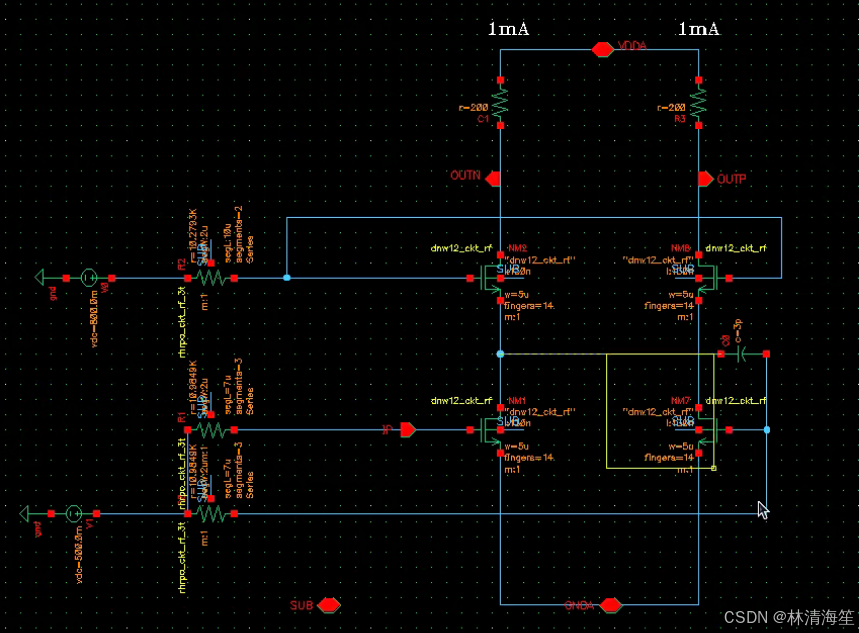

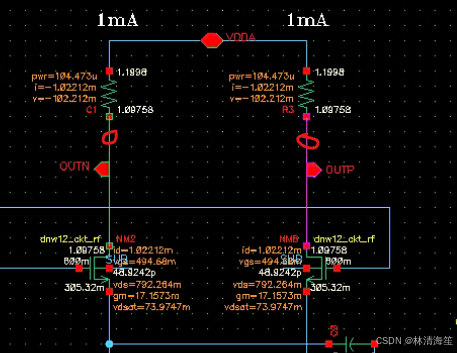

1. 电路原理图介绍

-

打开LNA电路原理图

-

左边和右边cascode采用3pF的隔直电容

-

负载电阻选用200欧姆。由于电源电压为1.2v,单边流过的电流是1mA,所以负载电阻上的压降为200mV。输出端OUT的电位为1v。后期会对负载电阻进行调整优化,保证拥有足够的增益。

-

输入晶体管的栅极电压通过直流仿真分析设置的0.5v,过驱动电压大概再100mv左右,Vth在450mv左右。

-

由于阈值电压为100mV,而漏端Vds要大于过驱动电压100mV,因此漏端电压Vds要在200mv左右,留足余量。

-

对于上面的cascode晶体管,由于源极还是有一定电压的,存在一定的衬偏效应,等效的Vth会更高一些,应该会达到500mV左右。然后再加上过驱动电压,所以M2的栅极电压为800mv。所以V0设置为800mV。

-

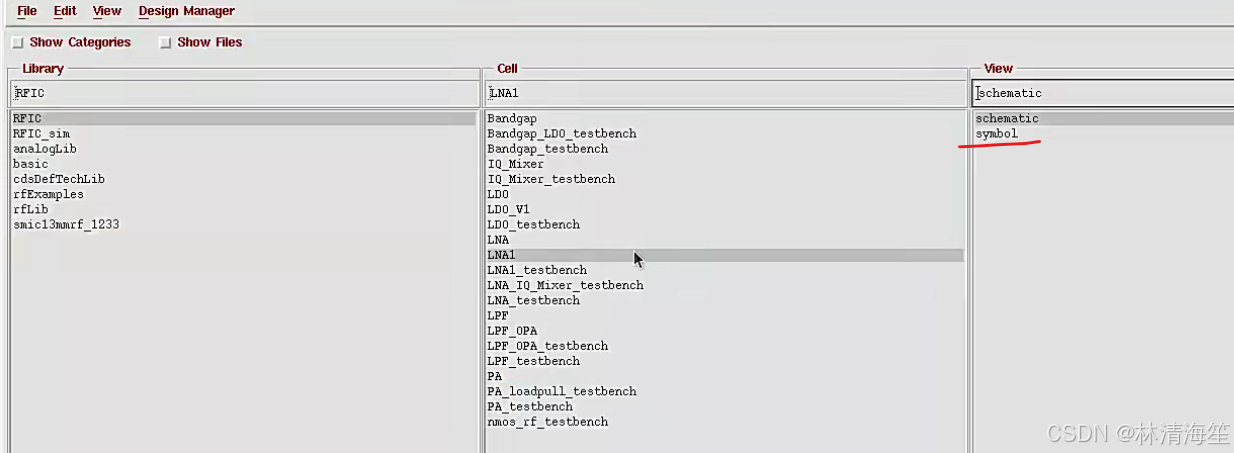

搭建好原理图后,就可以生成symbol。

-

由于已经有现成搭好的symbol,所以直接打开即可。

-

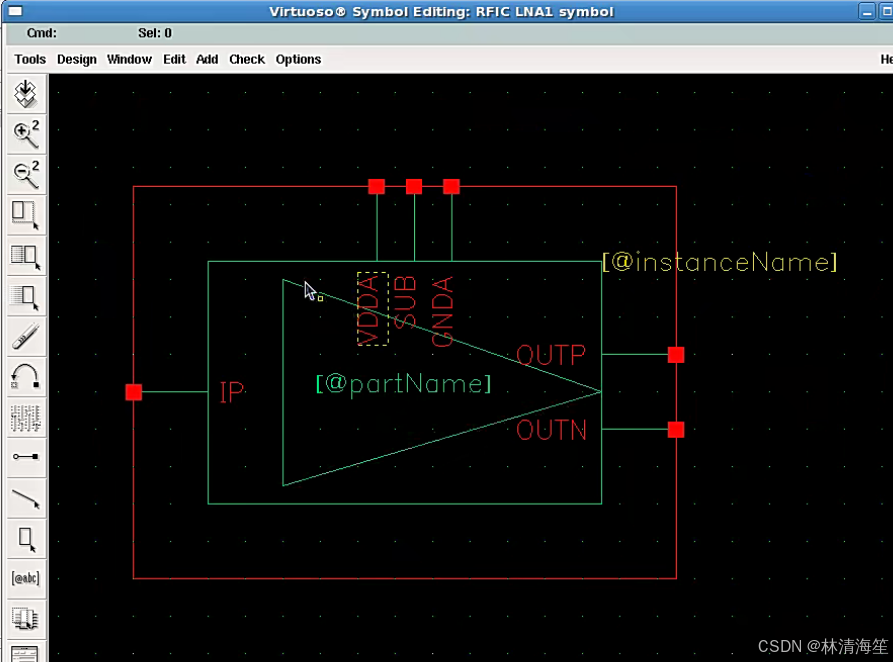

生成的symbol如下图所示

-

上面三个端口主要是VDD,GND和SUB,来给内部电路进行偏置

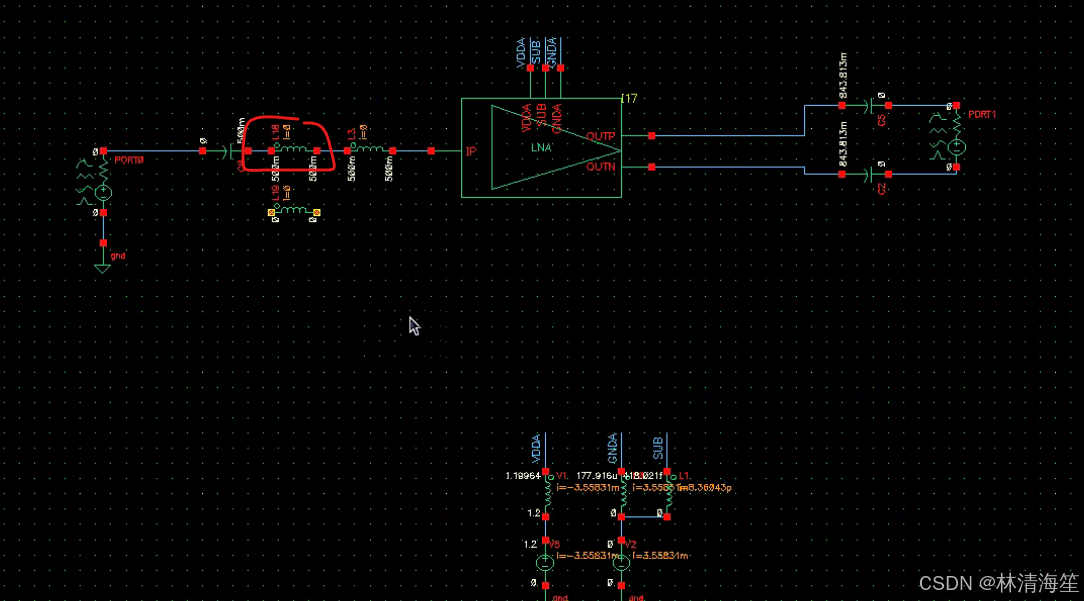

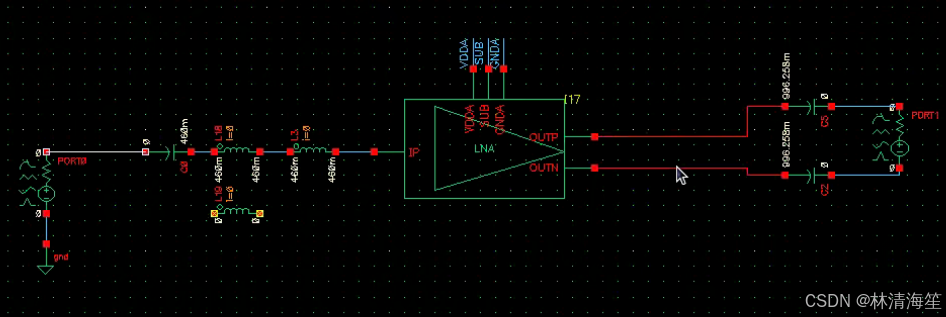

2. testbench搭建

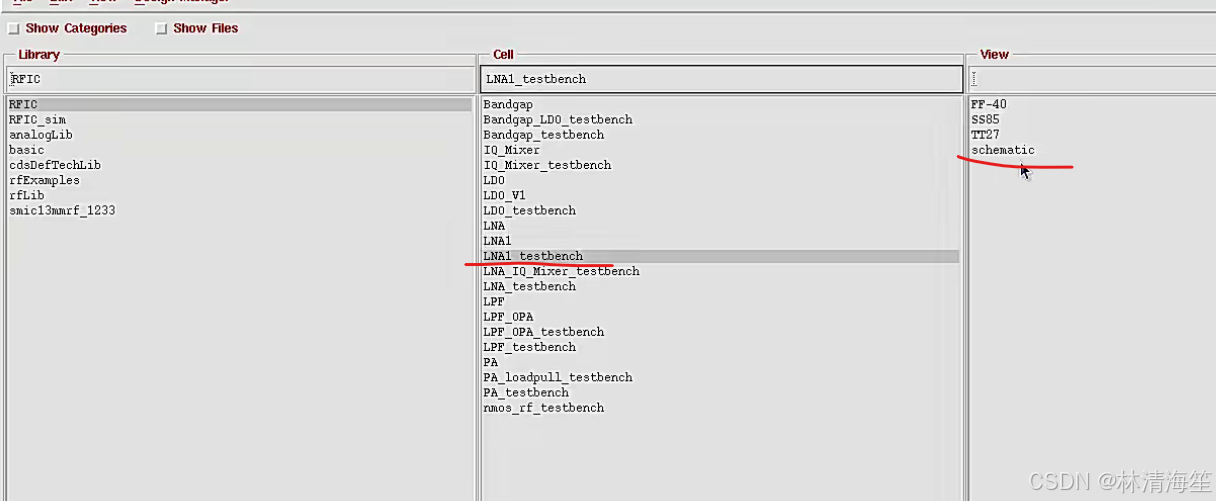

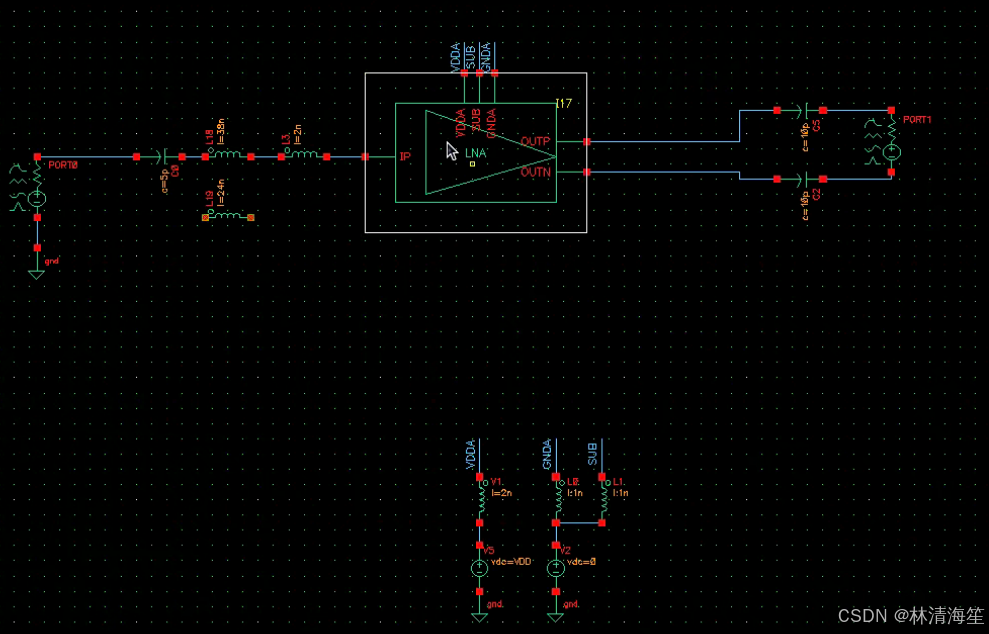

- 搭建好symbol之后,就可以去搭建仿真测试电路图,通过仿真去严正电路设计最终的性能参数指标能达到什么水平

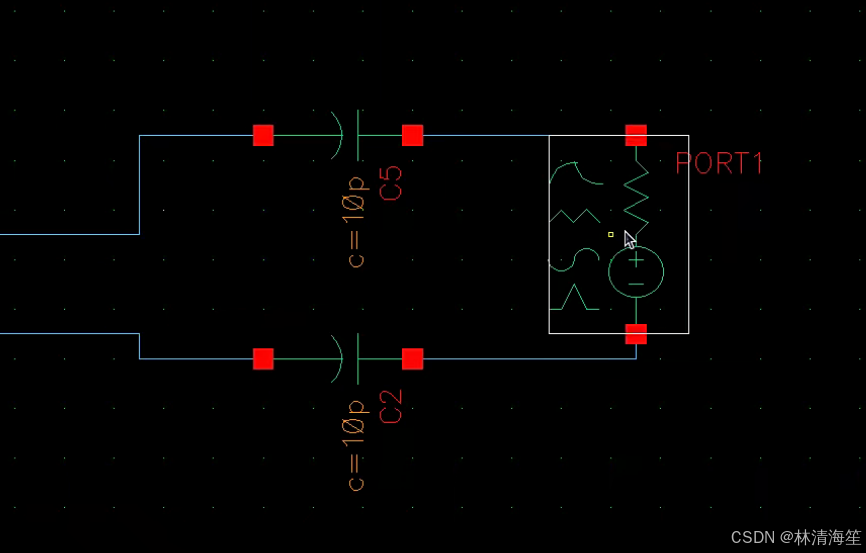

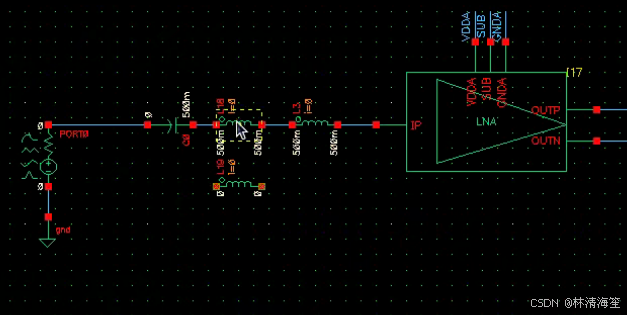

- testbench如下图所示,首先把刚搭建好的symbol调入进来。

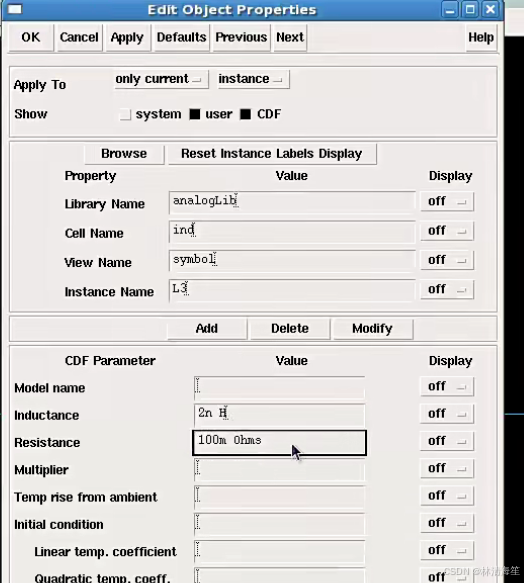

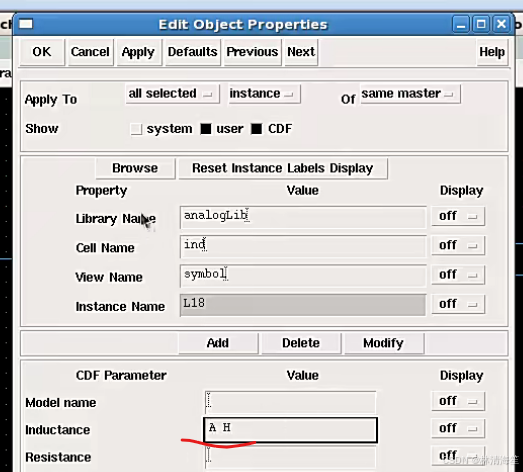

- 在输入端做了引线电感L1的模型,感抗值为2nH,内部寄生电阻设置为100m欧

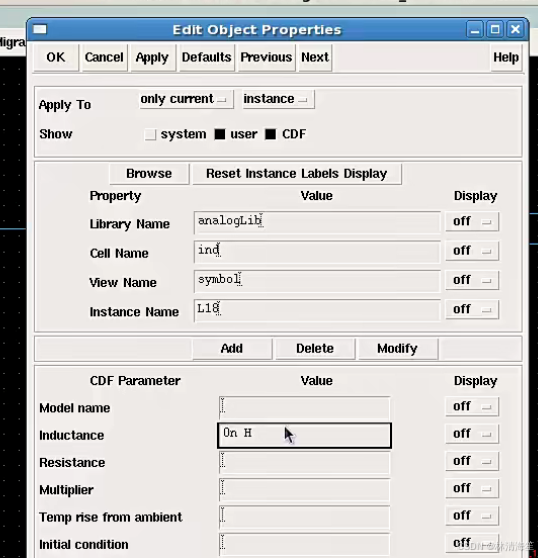

- 输入端还接入了匹配用的电感L0,首先我们把感抗值设置为0nH,之后再进行调整

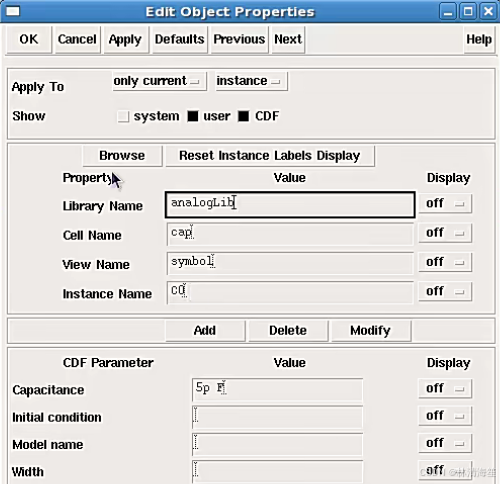

- 隔直电容C0选用5pF的大小。在2.4GHz的工作频率情况下

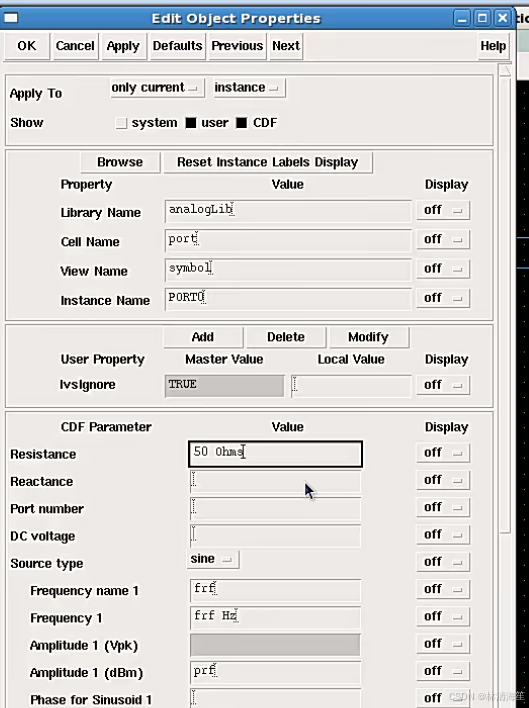

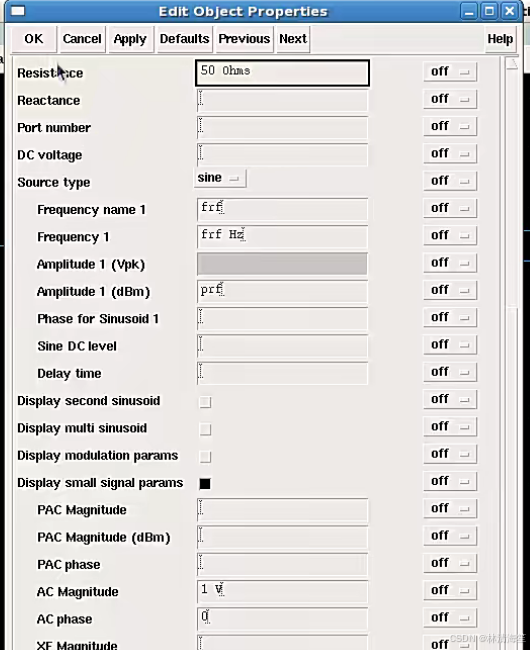

- 端口的设置跟单个晶体管仿真参数设置的一样

- 负载端由于是差分的输出,所以有两个隔直的电容,为10pF

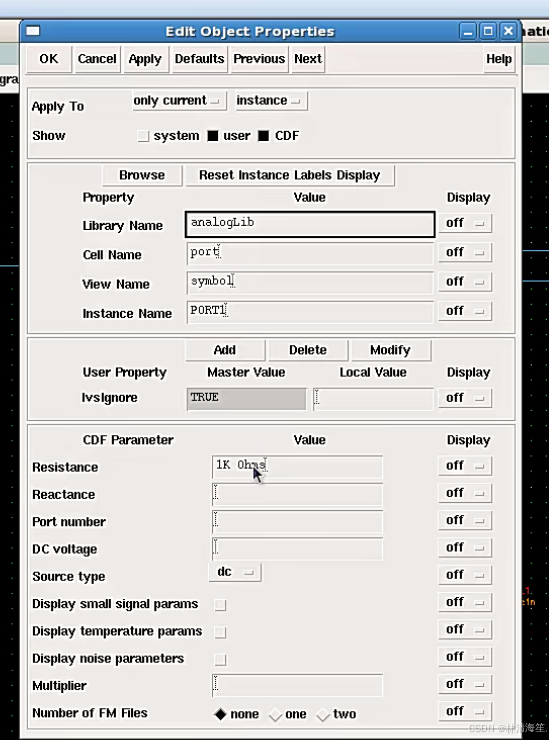

- 负载端口模拟混频器基本输入的阻抗,为1000欧姆。

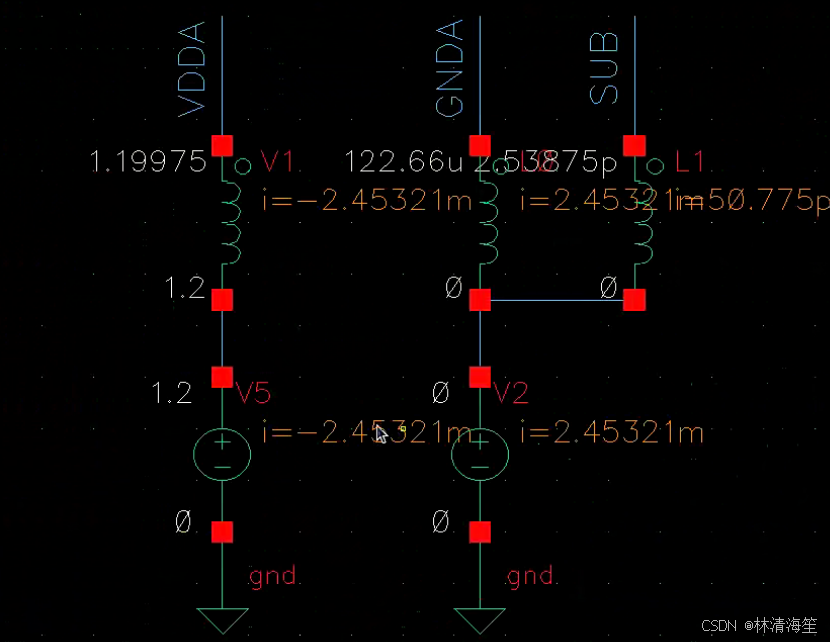

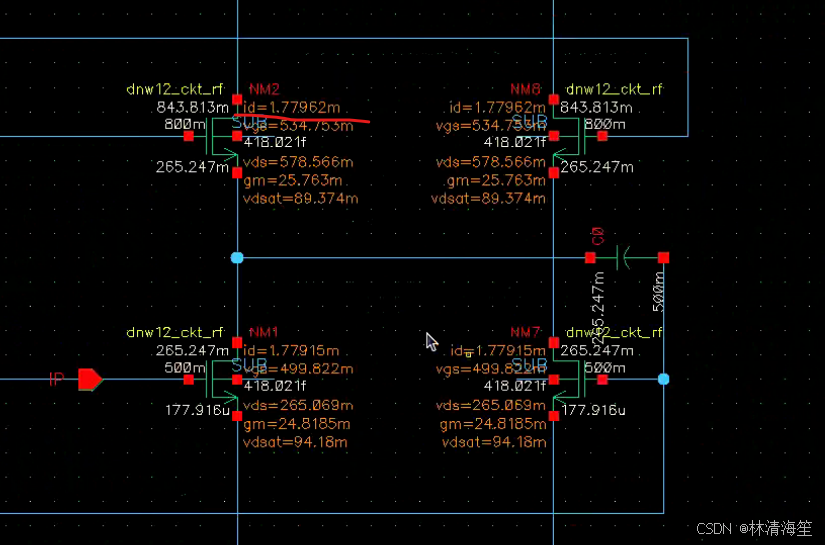

3. 直流仿真

- 以上就是testbench的元器件基本参数的设置

- 然后打开仿真器,把参数调入进来。

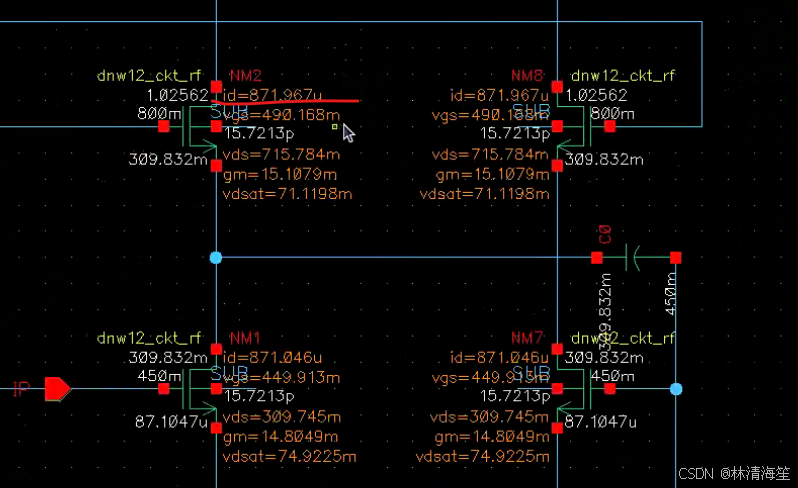

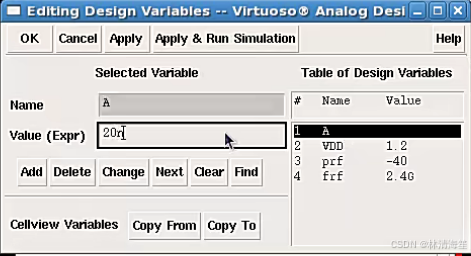

- 初始的变量参数如下所示

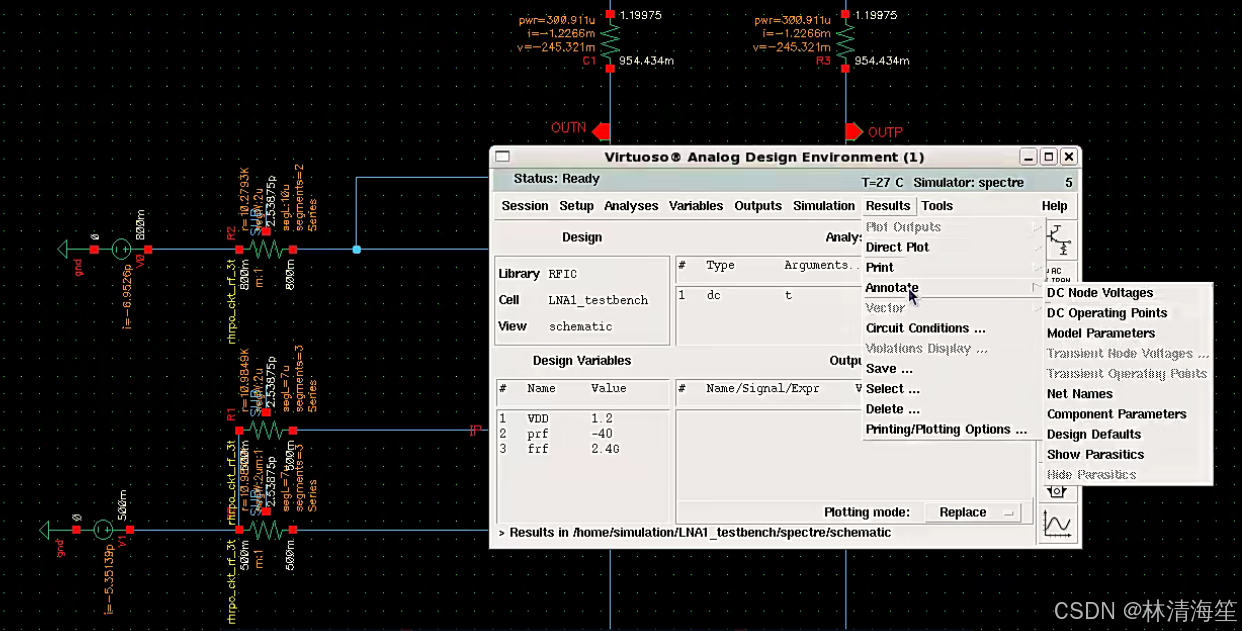

- 首先先运行dc仿真,查看直流工作状态是否正确

- 并显示出各节点电压和整个的工作电流情况。

- 可以看到总的工作电流是2.45mA。输入的栅极电压为500mV进入到子电路中

- 我们可以通过按键盘上的e键,进入查看symbol中的子电路模块。

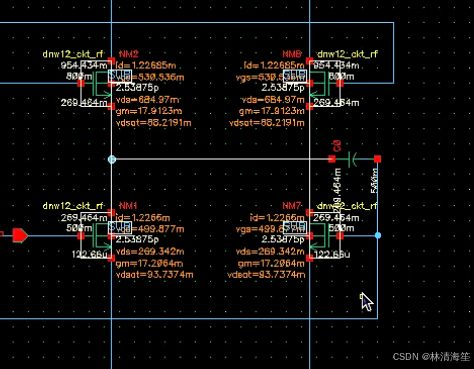

- 然后显示出子电路中所有的直流工作状态。

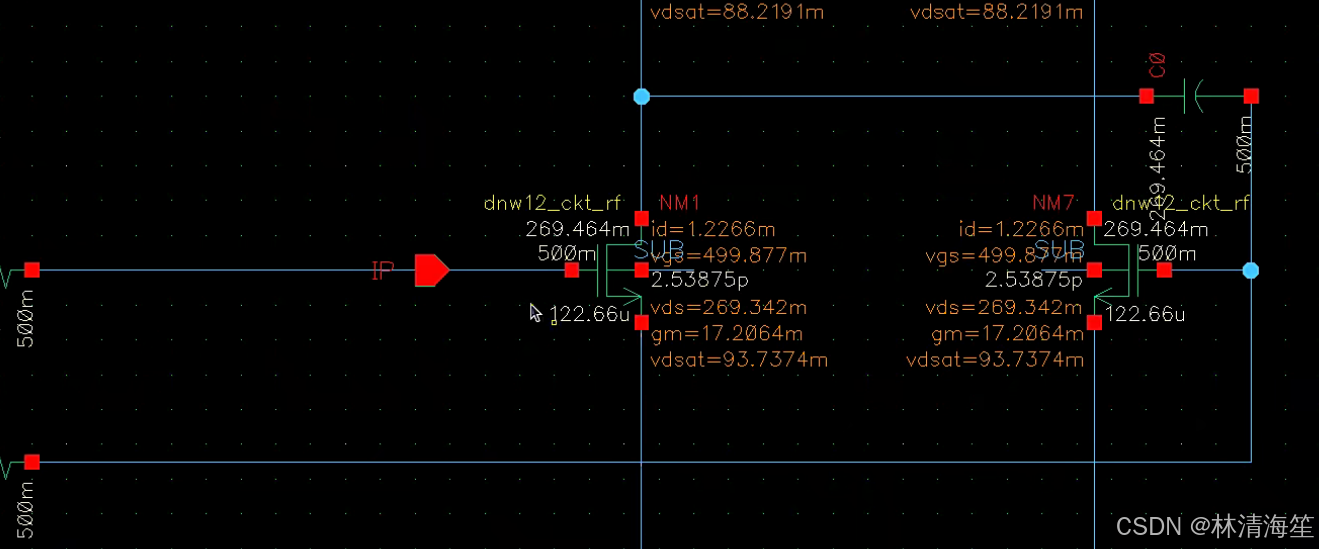

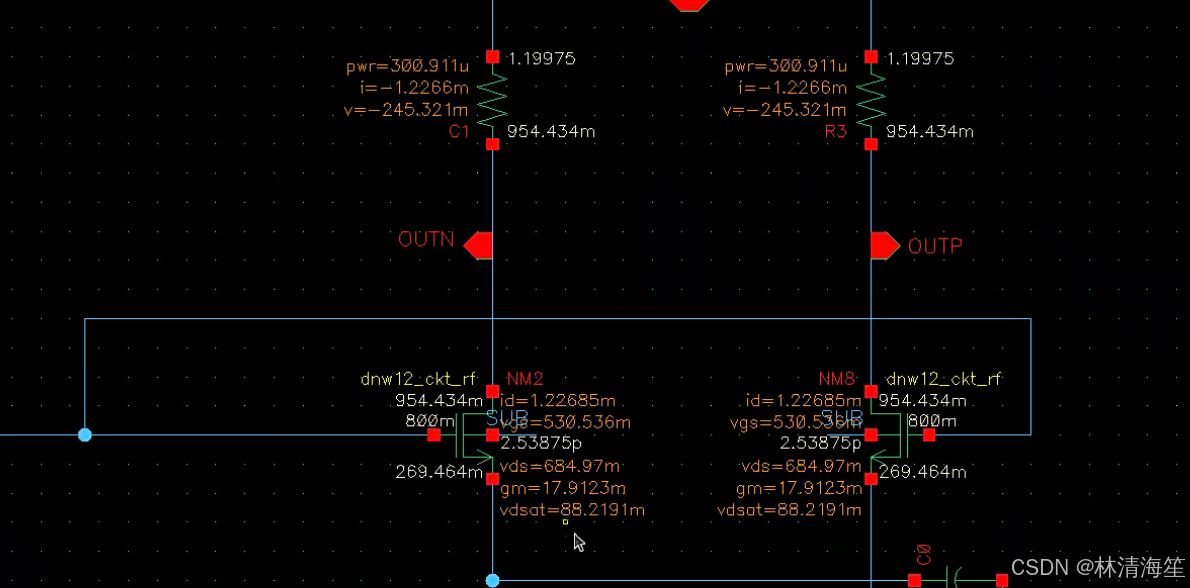

- 首先来看输入晶体管的栅极为500mV,漏极电压为269mV。过驱动电压Vdsat为93.73mv。因此这个晶体管是工作在放大区域的。

- 然后查看cascode级的晶体管,负载经过电流产生的压降后,在晶体管的漏端电压为954.43mV,然后这个晶体管的Vdasat为88.219mV。都是在正常的工作状态中

- 由于整体性能指标要求电路的功耗要做到2mA以下,当时刚才看到发现电流已经达到了2.5mA左右了,工作电流是偏大的,因此需要减小晶体管的尺寸,把电流给降下来。

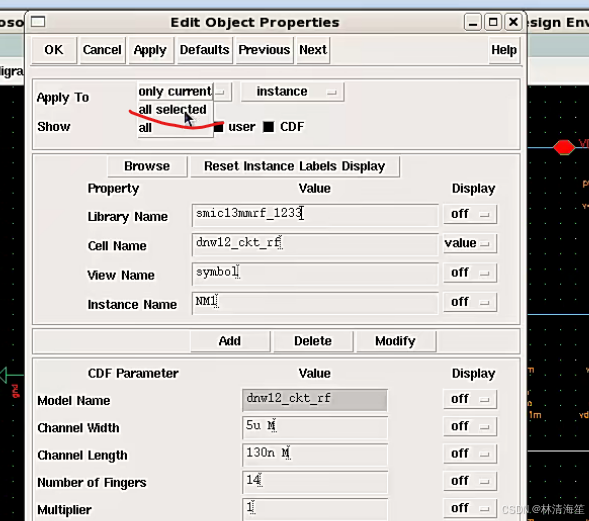

- 这里有个便捷方法是,用鼠标把四个晶体管都框住,然后按住键盘上的Q键

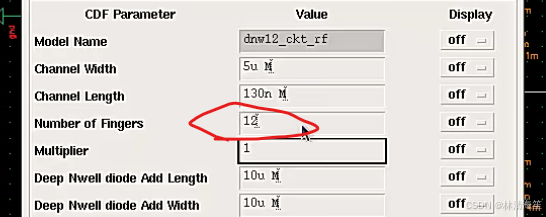

- 打开后选择all selected,先减小finger数到12个

- 然后保存并运行仿真

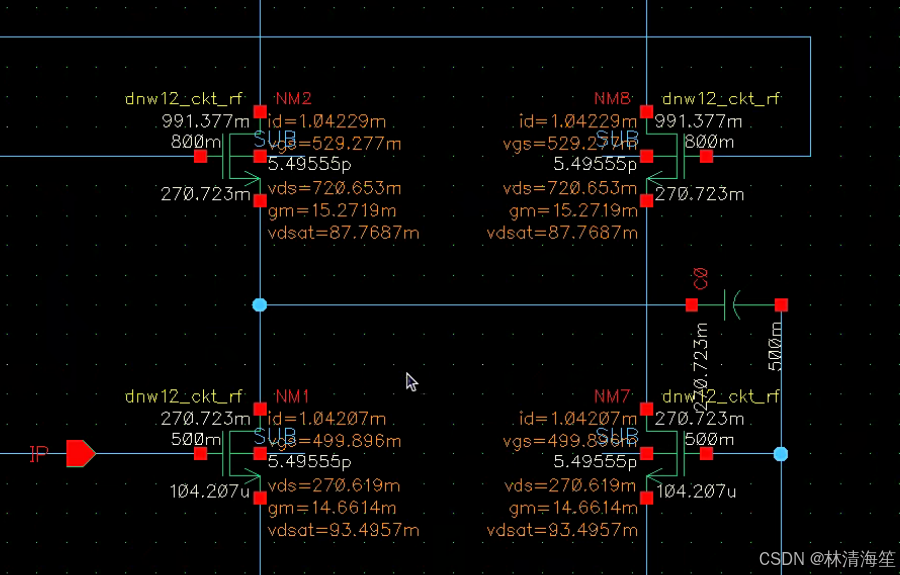

- 然后可以看到单片的电流为1.04mA,基本上是跟设定的值是比较接近的

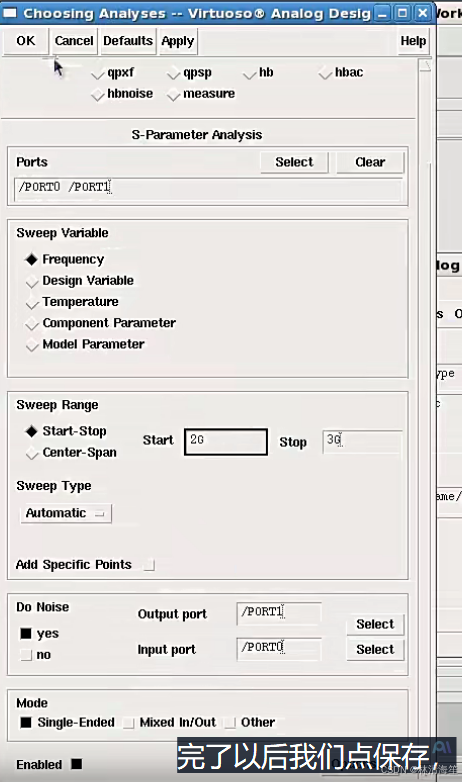

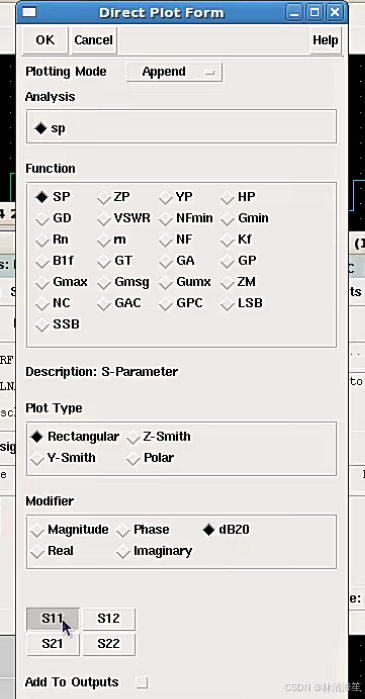

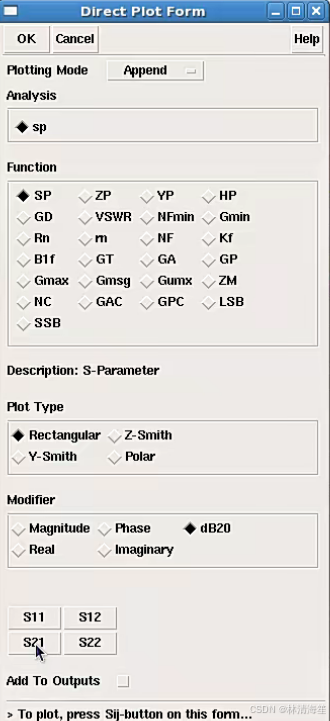

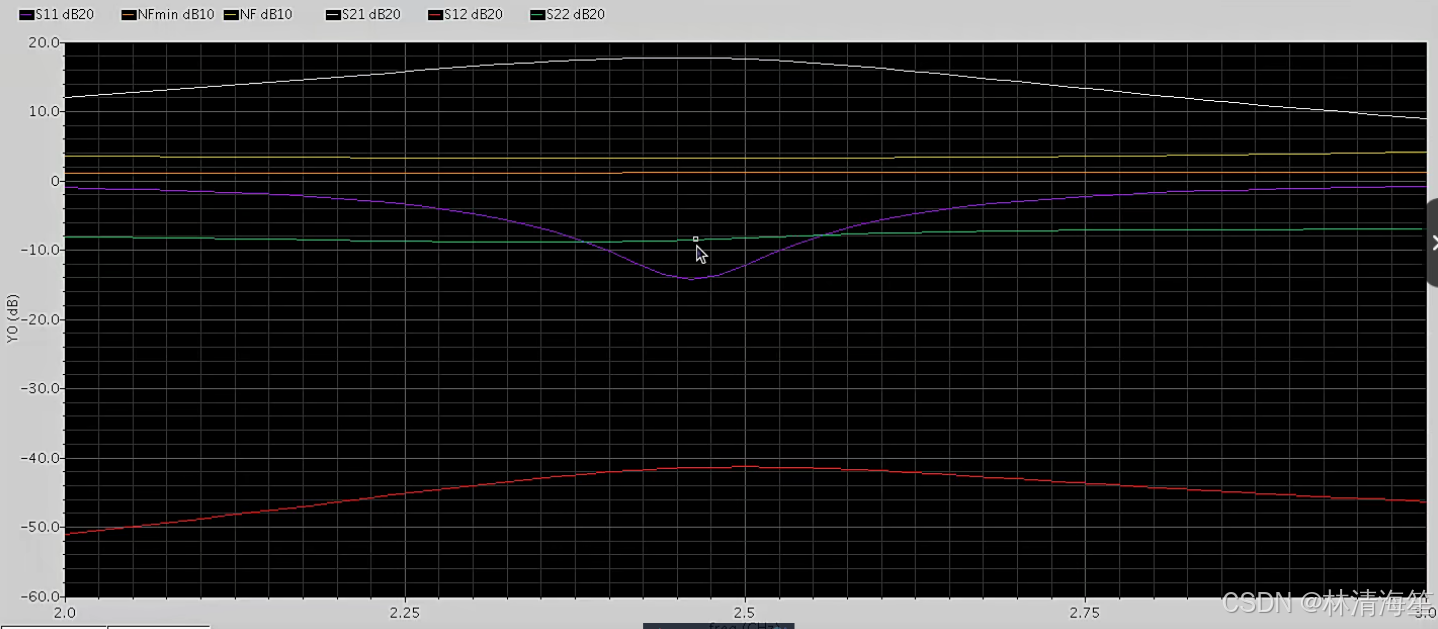

4. SP仿真

- 然后我们返回上一层的电路图中,查看S参数仿真,来看一下低噪声放大器的输入匹配,噪声系数和增益的一些相关情况。

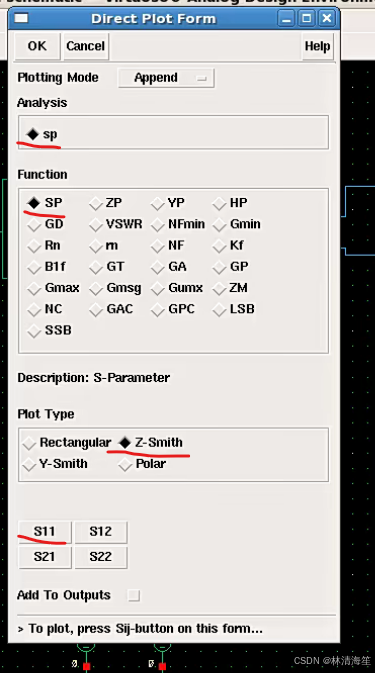

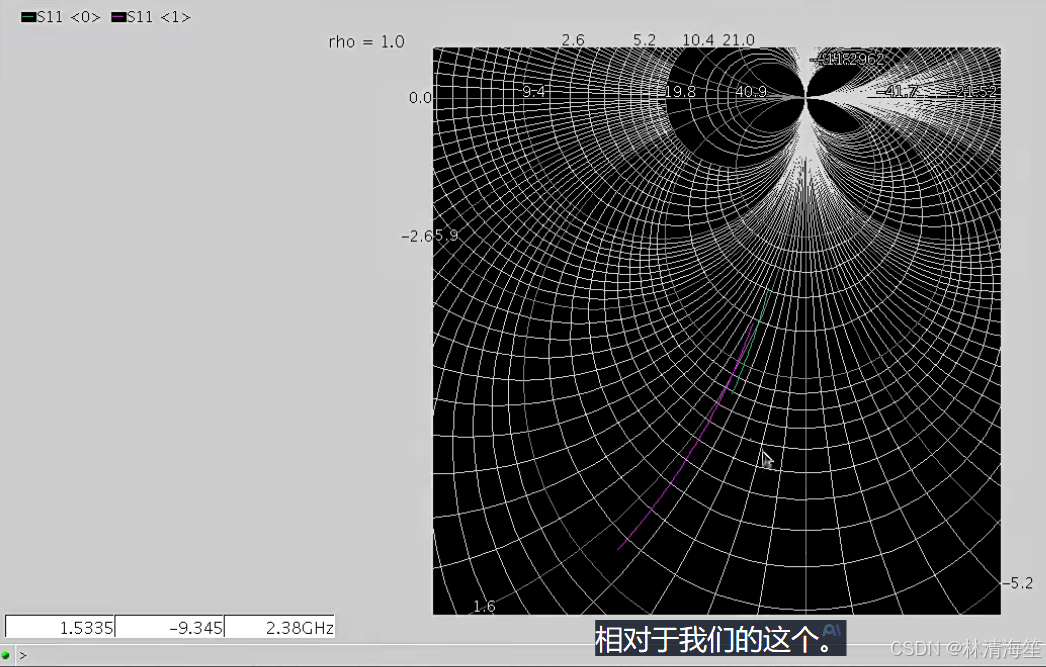

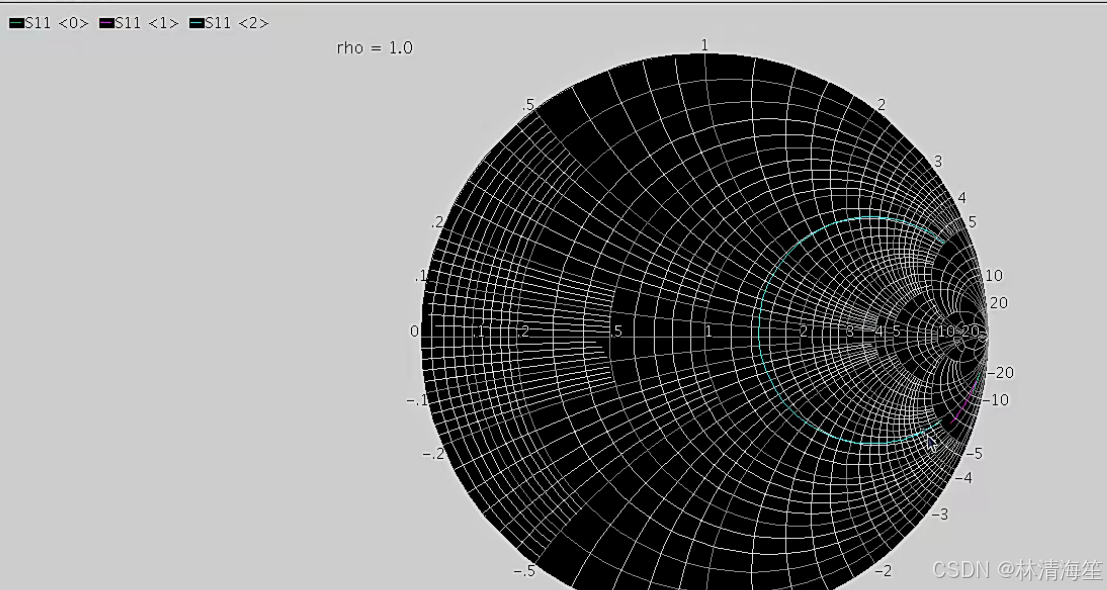

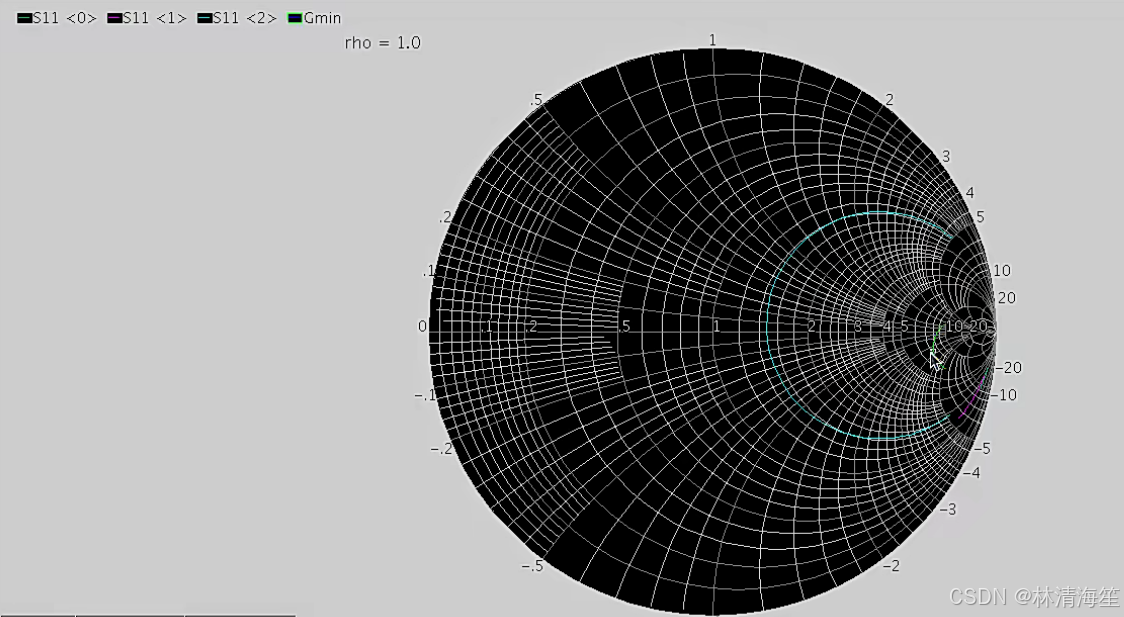

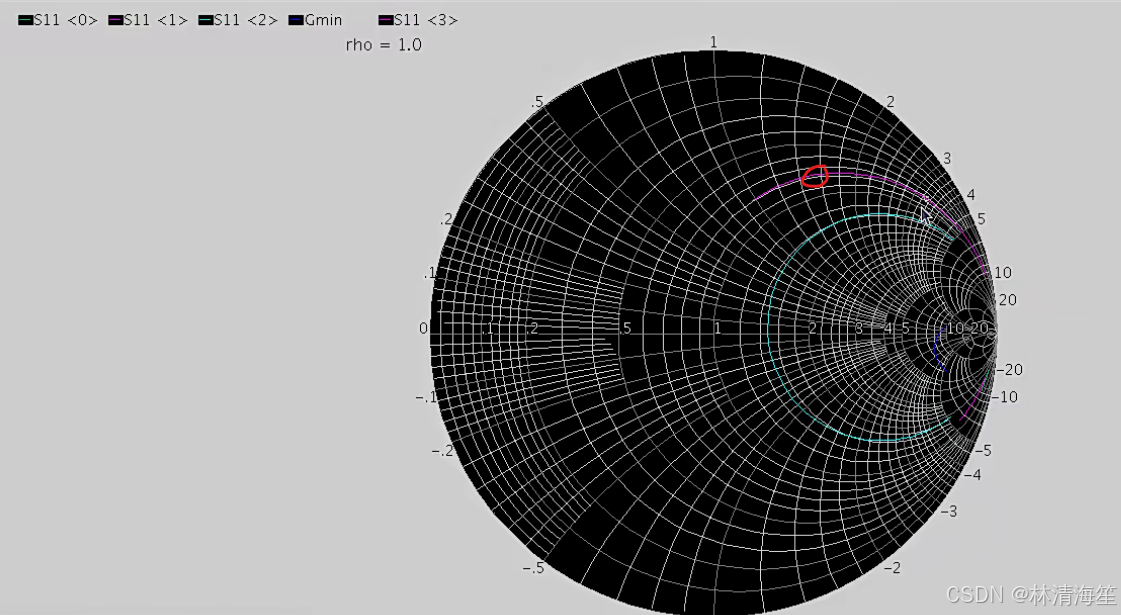

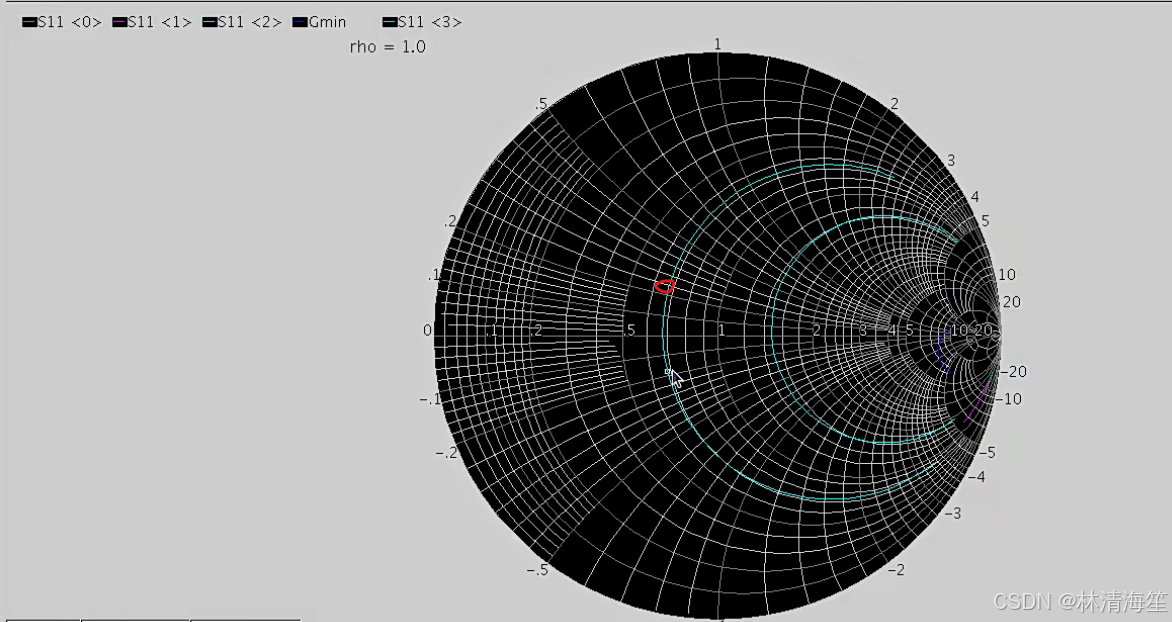

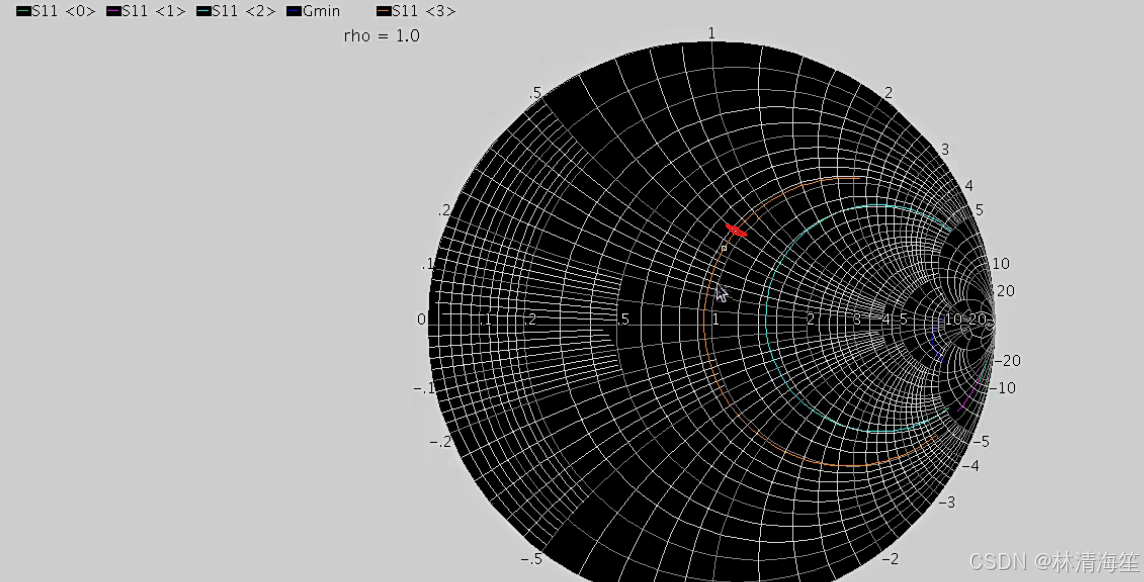

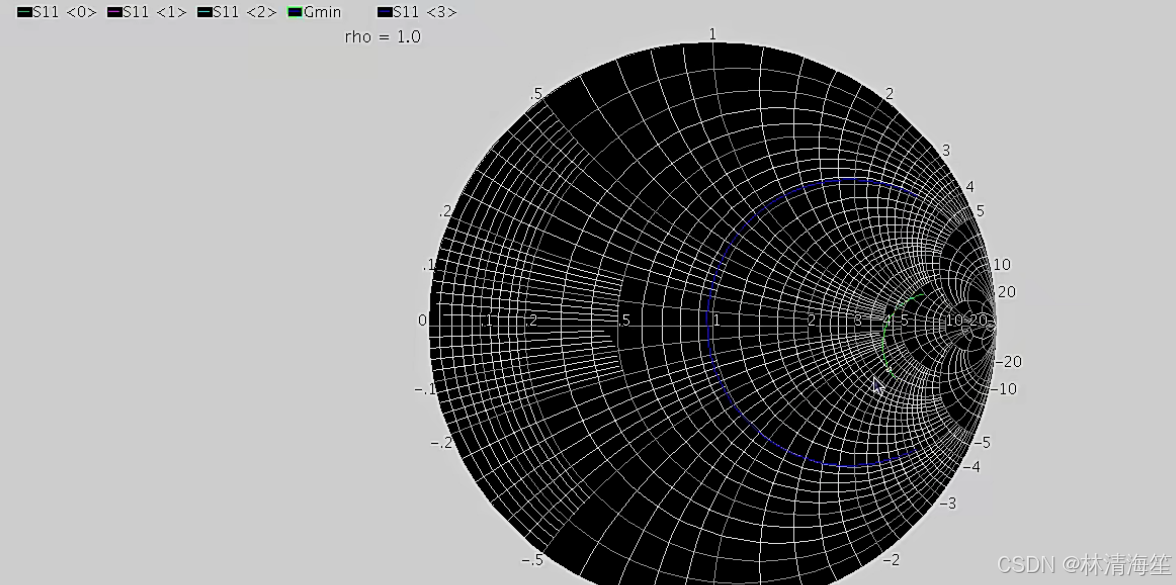

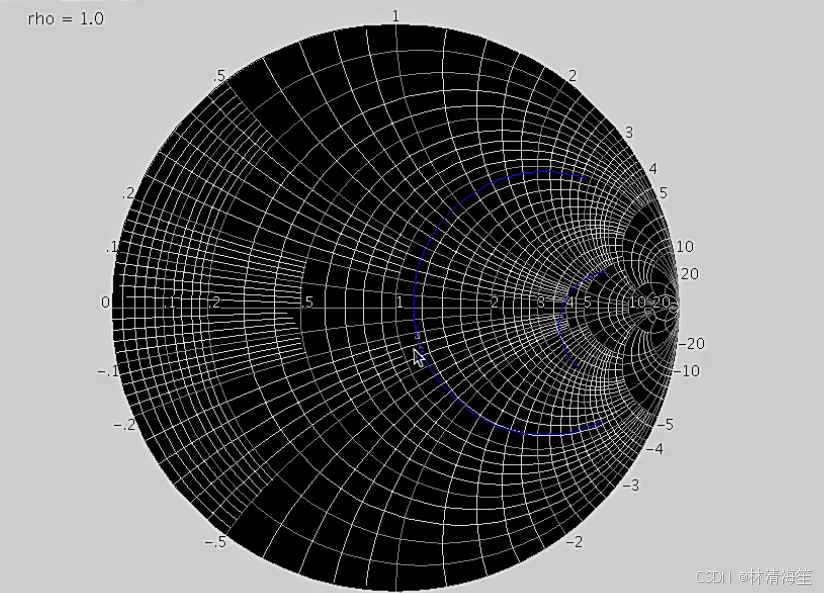

(1)输入阻抗匹配S11(史密斯圆图)

- 首先要做的就是对输入阻抗进行匹配。之前的电路参数指标里面有一个很明确的要求是S11反射系数要小于-10db。这里就需要用到史密斯圆图了,做阻抗匹配的话,

- 可以发现S11比较靠近史密斯原图最右边点的位置,在这个位置上的点做匹配相对来说会比较麻烦一些,匹配出来的带宽会非常的窄,电路Q值会非常的高。

- 我们放大史密斯原图,左下角有反射系数的实部、虚部和频率的值,可以发现在2.4GHz上,阻抗的实部为1.51,虚部为-12.1,所以虚部是电容特性,是一个负值。

- 我们需要做阻抗匹配,然后把虚部这部分给抵消掉。实部是一个归一化的值,所以它要乘以端口阻抗(50欧),所以实部还需要x50才是它实际的阻抗值。虚部也是一样的。

- 匹配是要求S11曲线从史密斯原图上面原来的位置,让他旋转(通过阻抗变换)移动到史密斯圆的中心位置(1的位置,即最佳匹配点)

- 阻抗匹配是,串联电容或是电感,输入的s11或是输出的s22,它的匹配的特性会沿着我们的等阻抗原图进行旋转。如果在输入端口并联电容或电感,那么它是会沿着等导纳圆图进行旋转。

- 实部在50欧左右还是比较接近匹配点,偏差不大。

- 但是由于虚部是负值,所以需要通过串联电感来使S11往等导纳原图进行顺时针的旋转。

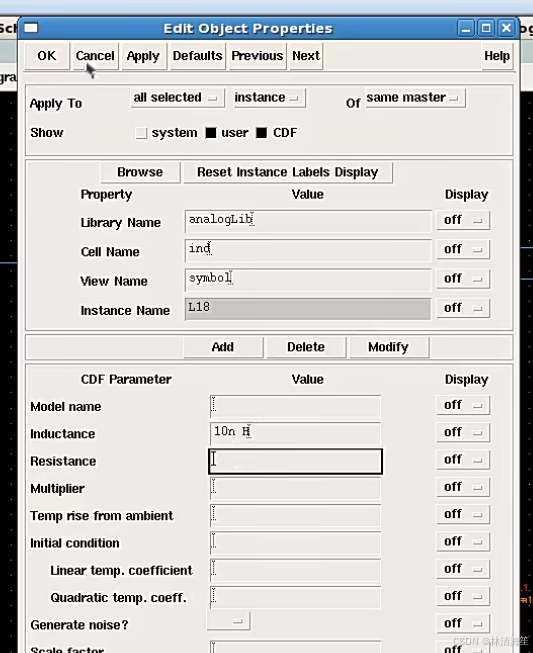

- 这里先串一个10nH的电感,

- 串入电感后的曲线(红色)相较于绿色曲线是有沿着等阻抗圆顺时针移动的

- 由于加的值不够大,李中心点还比较远,所以还需要进一步去加大输入的匹配电感为38nH

- 然后可以发现,整个S11曲线(浅蓝色)会被拉的很长。蓝牙的工作频段2.4G-2.5G已经非常靠近史密斯原图的中心点了。

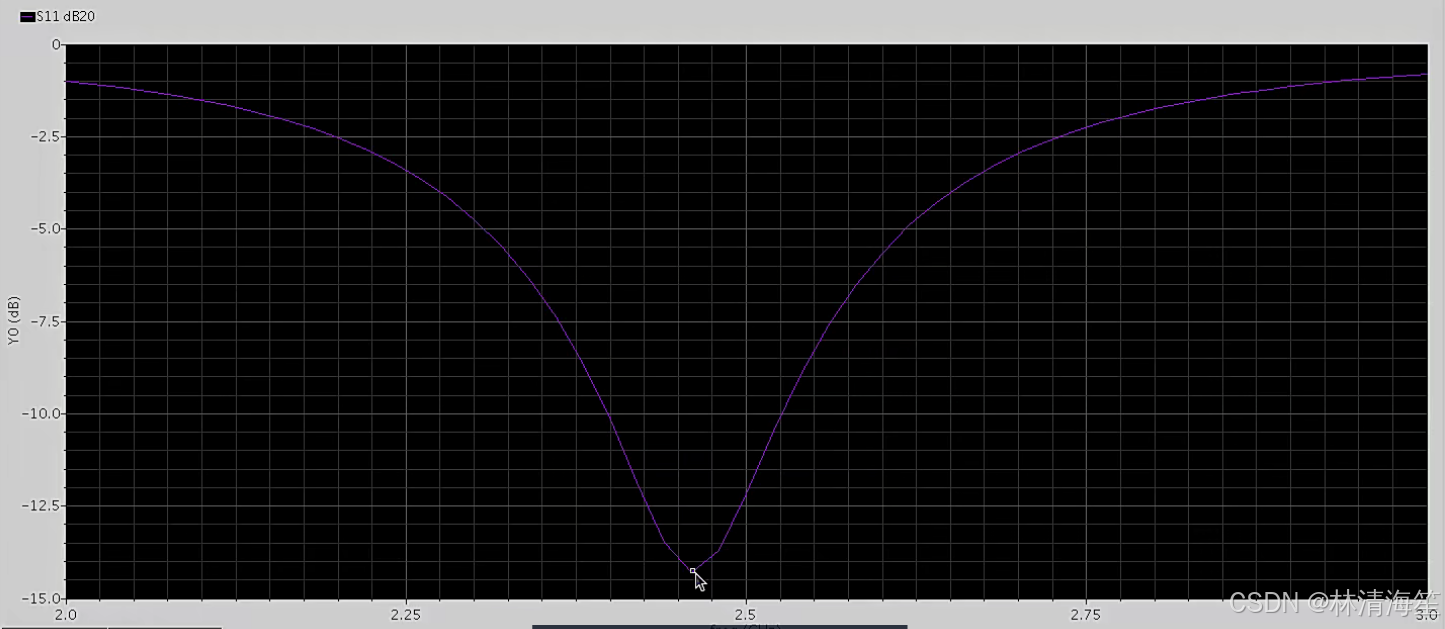

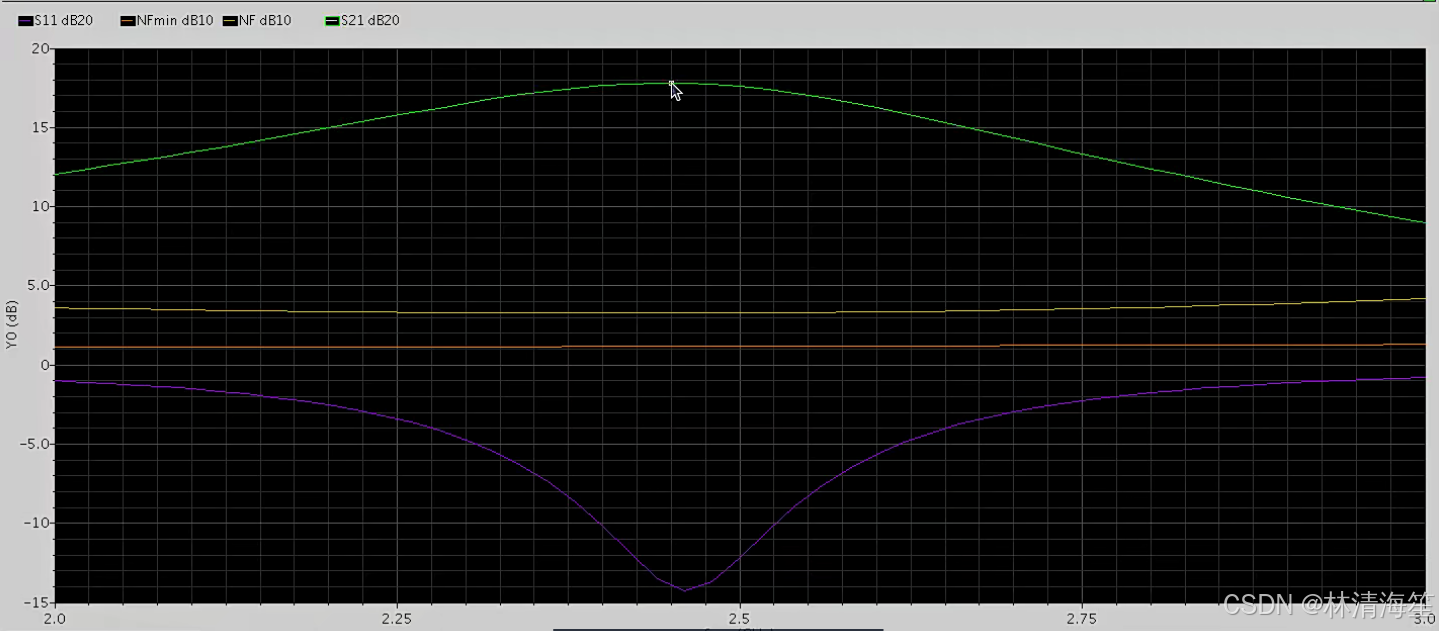

- 那么我们现在查看S11输入特性曲线

- 能够看到在2.45GHz的时候,S11的值为-14dB。匹配的-10dB在2.4GHz到2.52GHz的频率范围,S11是小于-10dB的。

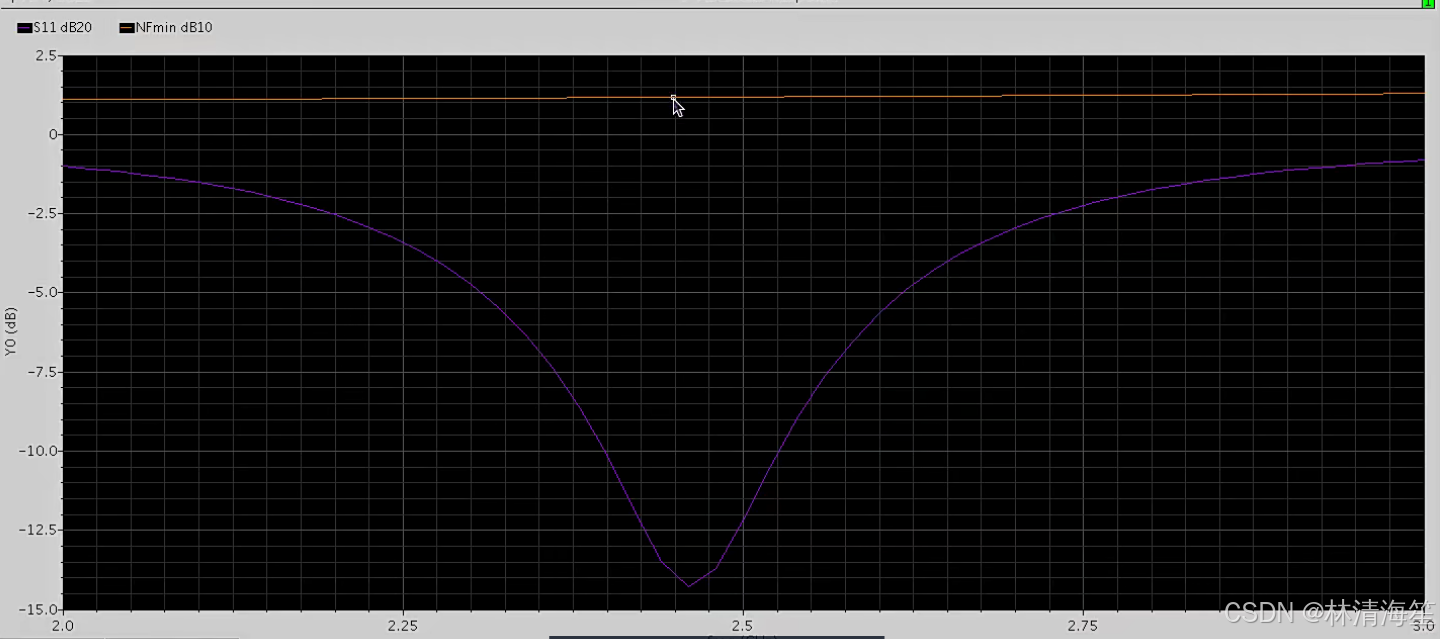

(2)最小噪声系数NFmin

- 接下来查看最小噪声系数NFmin

- 能够发现最小噪声系数NFmin在1.17dB左右。

- 然后我们查看实际的噪声系数NF

- 可以发现实际的噪声系数NF在2.4GHz上是3.27dB。因此我们要去优化噪声系数

(3)最佳噪声系数匹配点Gmin

- 首先我们要查看最佳噪声系数匹配点所在的位置

- 点击Gmin,也就是最小噪声系数所能实现输入源阻抗的共轭值。

- 可以看到最佳阻抗匹配曲线Gmin,随着频率不一样,最佳噪声系数源阻抗的值也会不同的。

- 可以看到Gmin和S11的匹配上相差非常远的,这样会使整个最终的实际噪声系数NF和最小噪声系数NFmin的差异会非常大。

- 我们在实际电路设计的时候,既要去保证有小的噪声系数,同时也要去确保输入S11的匹配性要有足够的匹配程度(小于-10dB)。这时候就需要去优化整个电路的参数来对噪声系数和输入匹配进行更好的优化

- 如果Gmin和S11在原图上是出于完全共轭匹配的,那么他们所能达到的噪声系数就是最小的噪声系数。因为在低噪放里面输入阻抗要与源阻抗进行共轭匹配的,即实部相等,虚部为相反数。

- 反映到史密斯圆图上面,就是S11曲线与Gmin曲线要出于一个共轭对称(也就是上下半平面对称的位置)。如果共轭程度越好,匹配程度越好,那么噪声系数就会越小。

- 首先看S11的实部实在1.5左右,虚部为0。在2.4GHz左右Gmin阻抗值实部为8,虚部为1.6。所以主要还是实部的差异比较大,导致噪声系数偏离NFmin比较远

- 这些是需要我们去修改晶体管尺寸参数和匹配电路,使Gmin和S11尽量的靠近,达到共轭的状态。

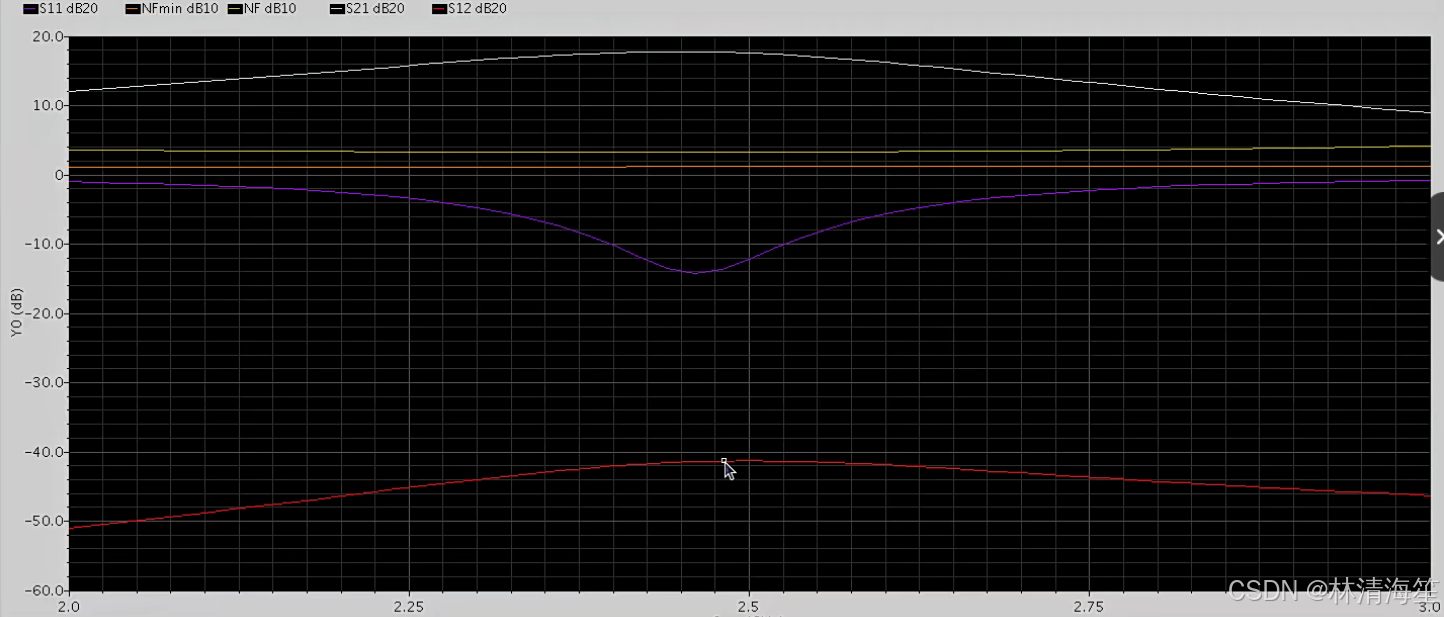

- S21(正向增益)S12(反向隔离度)S22(输出匹配)

- 由于我们已经做好了匹配了,也可以来看下S21,也就是正向增益部分

- 能够看到S21是在17.8dB左右

- 同步来看反向隔离度S12大概是在-40dB左右,已经足够高了

- 输出匹配S22。因为在芯片设计上面输出匹配是直接接混频器的输入端晶体管栅极,并不是接到芯片外部的50欧的阻抗上面。所以输出匹配这部分不会去单独做成跟混频器的输入去做共轭匹配,只要电压能够传递过去,那么就没有什么问题。所以我们这里面输出匹配对于我们LNA来说并不是太重要。

- 通常情况下,在芯片内部做级间匹配,频率不是特别高到微波频段上时,通常是不会去做级间共轭匹配的。而是直接让一个电压传递过去,或者负载并联谐振的网络,能够让后级负载电容能够吸收进来,让整个并联谐振网络能够共同谐振在一个所需要的频率点上面,信号就能够顺利的传输过去。级间级联更多考虑的是电压传递的过程,而不是整个信号能量的传递过程。

- 能够看到下图中,S22的性能不是太好,大概是在-8dB左右。

- 因此我们只关心S21,噪声系数,以及输入匹配S11。

- 目前输入匹配相对来说不是太好,噪声系数也不是最优的值(虽然能够满足性能参数的要求,但还需进一步去优化)。

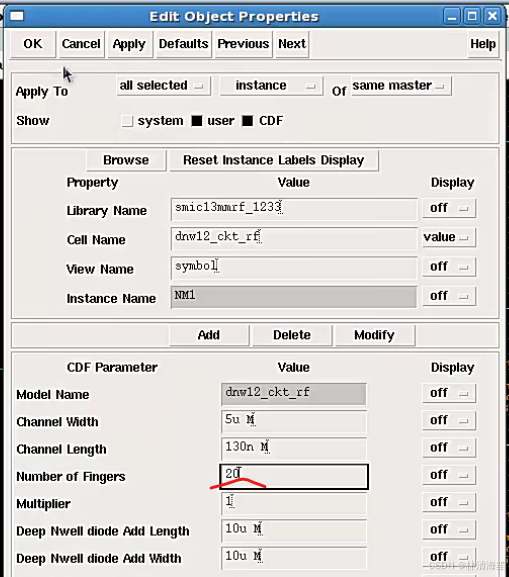

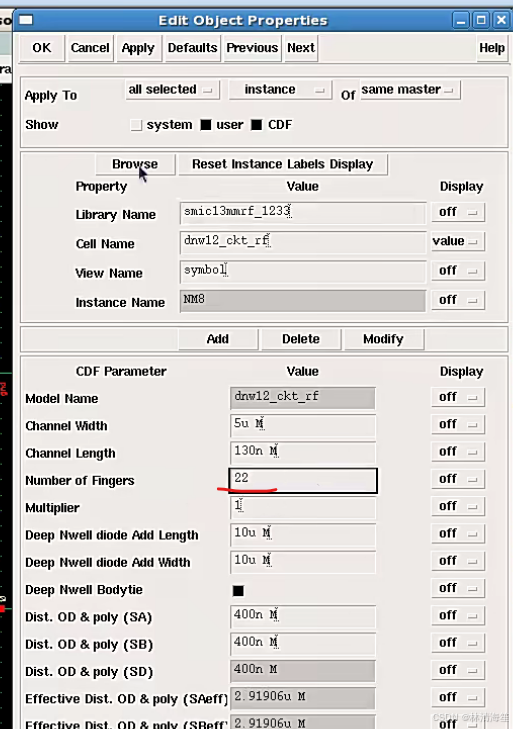

(4)调整优化晶体管参数

- 进入到子电路模块中,尝试把晶体管的尺寸加大

- 将finger数量加大到20

- 然后回来看看史密斯圆图上新的匹配曲线。

- S11(紫色曲线)在2.4GHz的时候,实部是在0.7左右,虚部是在4左右,是因为在输入匹配的串联电感太大了,导致史密斯圆图旋转以后超过了

- 所以我们来修改输入匹配电感为20nH

- 重新画出S11,可以发现整个曲线相对来说已经比较接近驶入匹配点了。但是实部值是偏小了,只有0.7左右,主要原因还是电流值太大了。

- 查看子电路,单边晶体管的工作电流已经达到1.7mA了,因此需要同时减小偏置电压

- 我们来减小输入晶体管的栅极偏压为450mV

- 重新仿真可以发现单边工作电流只有870mA

-

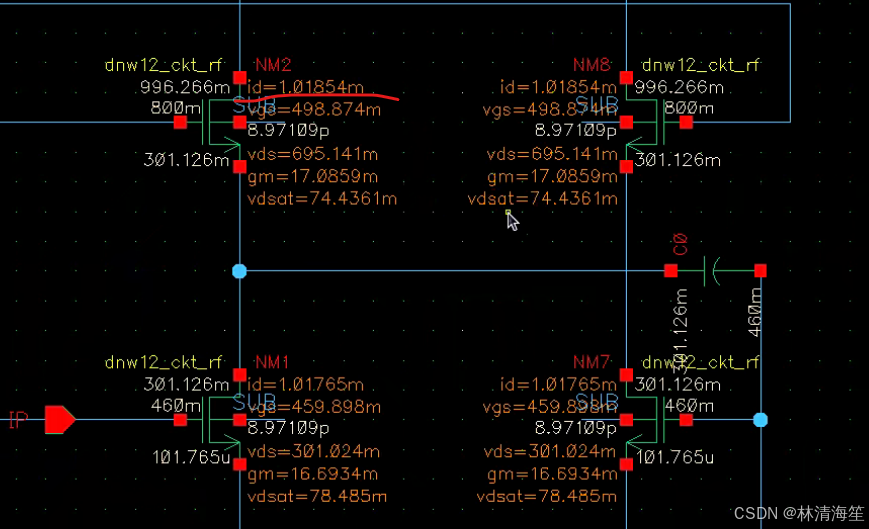

稍微加大一些输入晶体管栅极偏置电压为460mV,增大单边工作电流至1mA左右

-

然后仿真S11曲线

-

此时S11在2.4GHz的时候,实部在0.9左右,接近于1,匹配特性较好。

-

但虚部是负值,说明还需要去进一步加大输入匹配的电感值

-

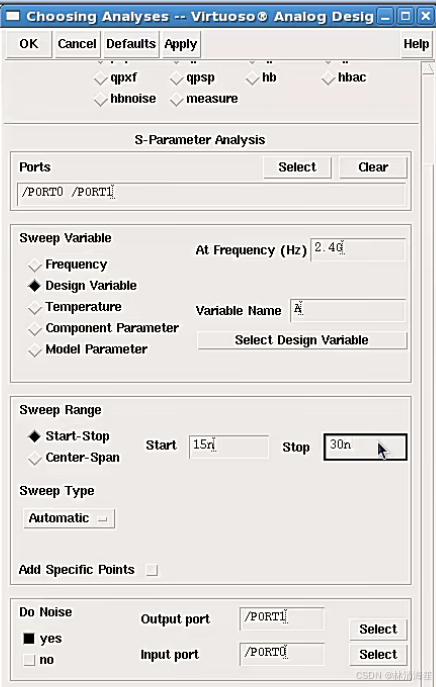

这里我们直接对输入匹配电感进行参数扫描,设置变量为A

-

设置变量初始值

-

运行S参数

-

来看S11扫描旋转的结果,都是2.4GHz的工作频率。

-

在24nH左右,S11就会旋转到输入匹配点上的位置。

-

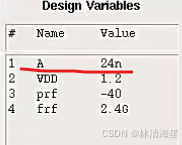

更新输入匹配电感的初始值为24nH

-

然后再重新运行频率扫描的S参数,S11(紫色曲线),然后点击刷新所有参数曲线

-

可以发现最佳匹配点是在2.44GHz,

-

但是Gmin曲线还是跟S11偏差比较远的,即最小噪声系数NFmin和实际噪声系数NF还是有一定的距离的。

-

因此这些是需要反复优化迭代的过程

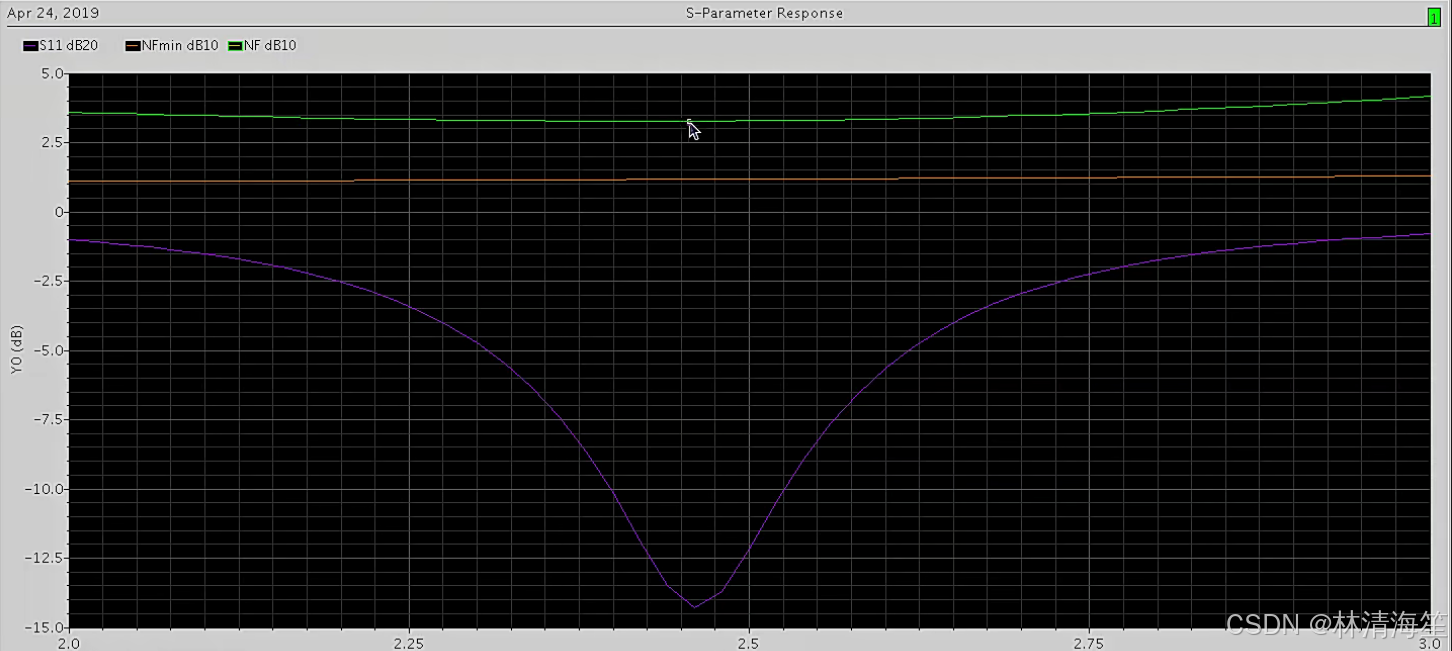

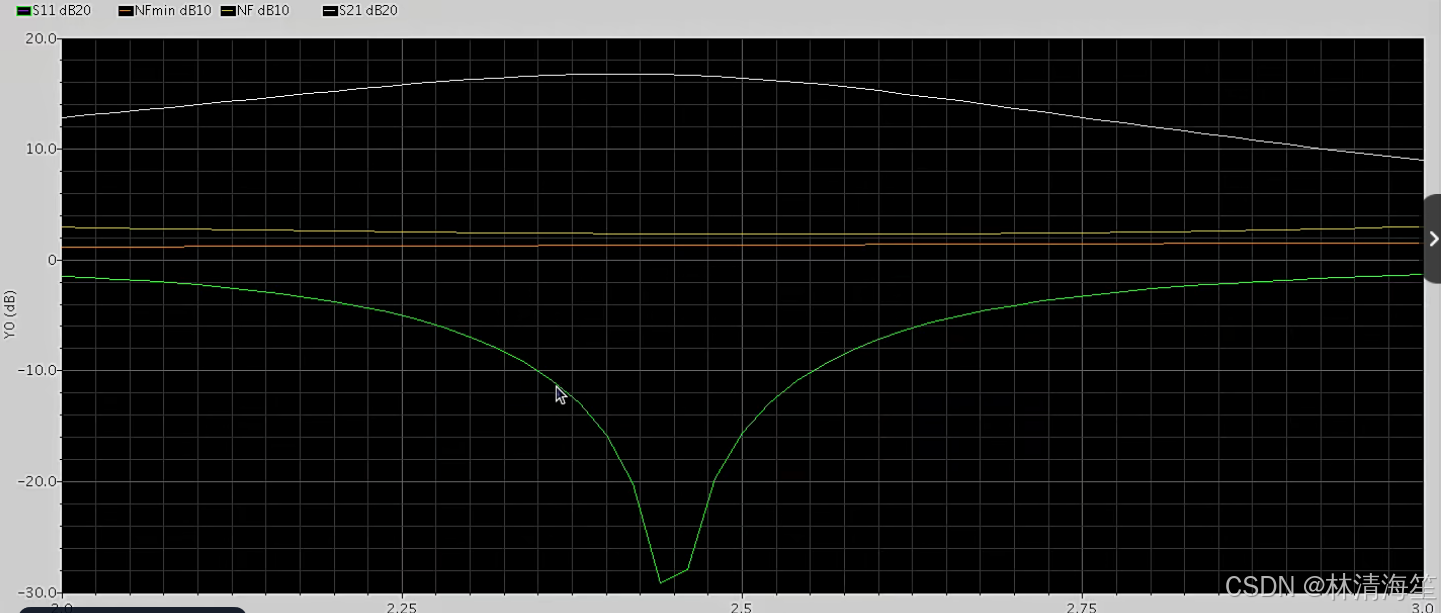

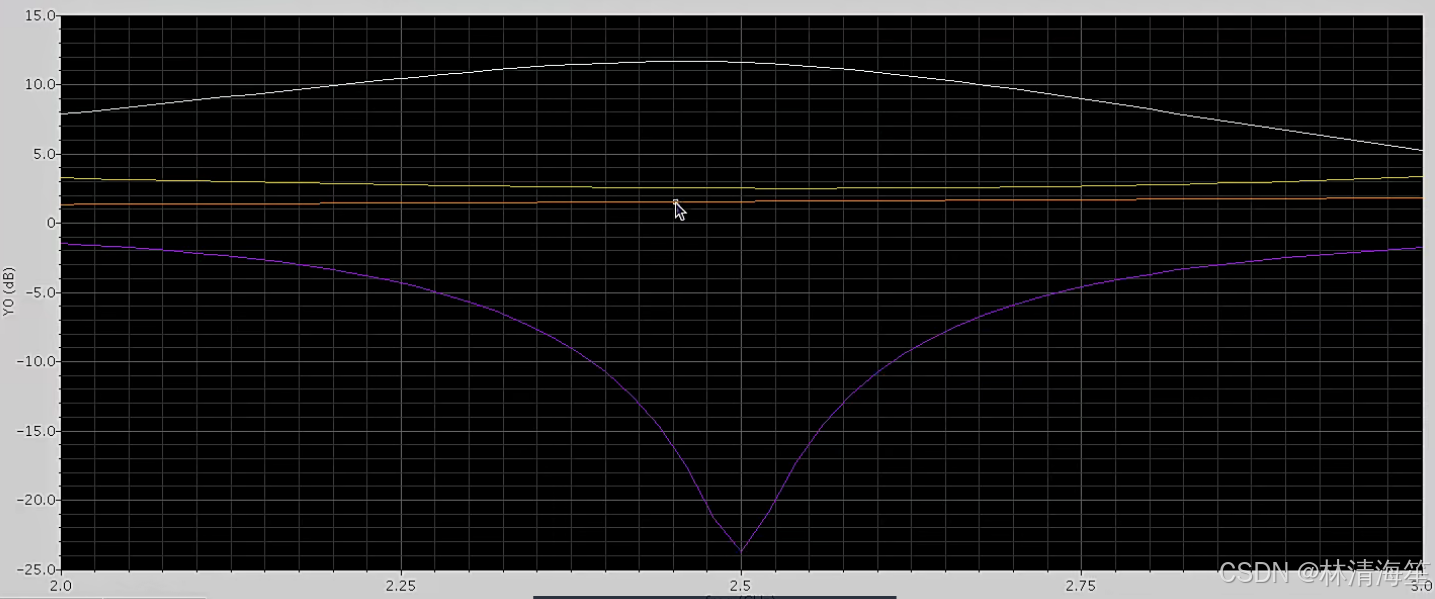

- 刷新加载在rectular上面的s参数

- 可以发现输入匹配S11(绿色)在2.4GHz左右能够达到-20dB。最低能够达到28dB左右。小于-10dB的频率范围是在2.35-2.55GHz,能够完全满足工作频段的要求了。

- 最小噪声系数NFmin(橙色)是在1.33dB左右,较上一次有了一定的下降。

- 实际噪声系数NF(黄色)在工作频段上是2.35dB左右,能够满足系统定义的模块指标要求。

- 增益S21范围(白色)在工作频段上是16.7dB左右,等效功率增益的值。

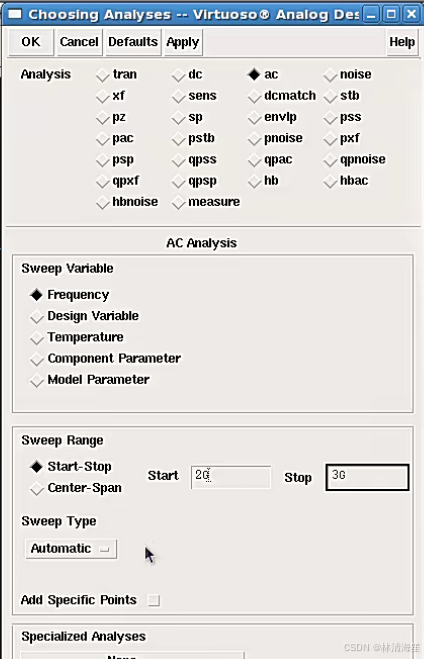

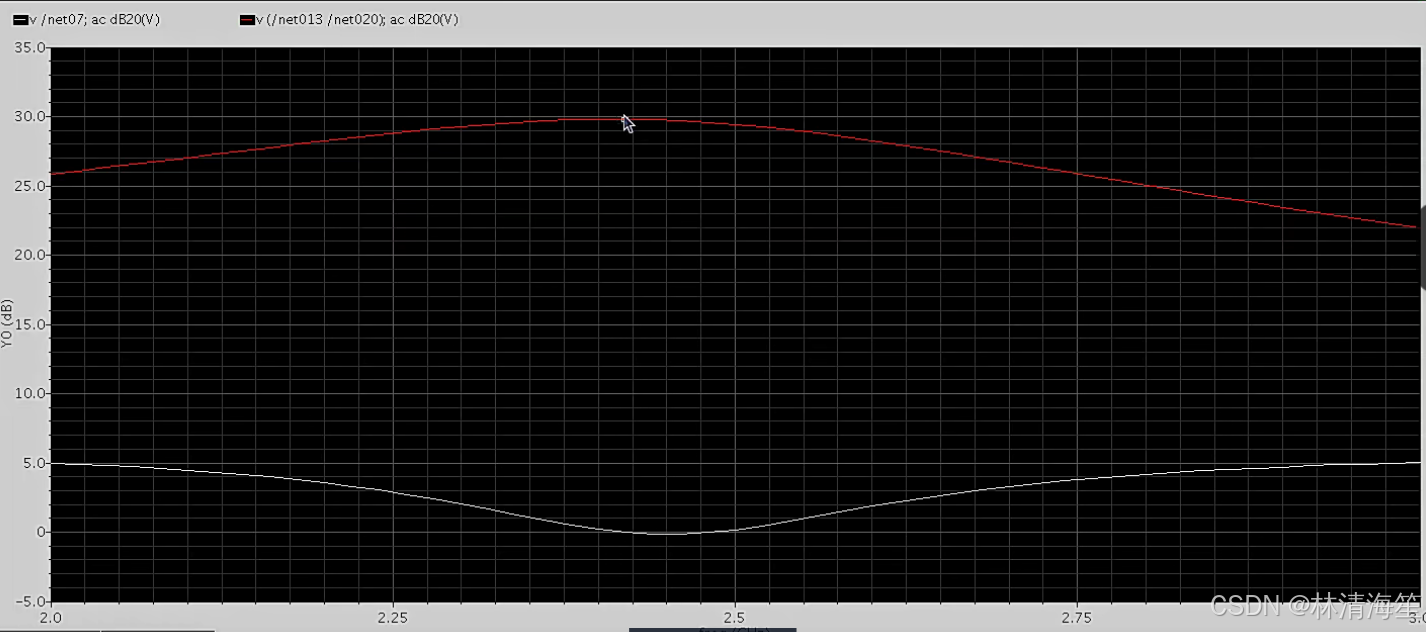

5. 交流AC仿真

(1)电压增益

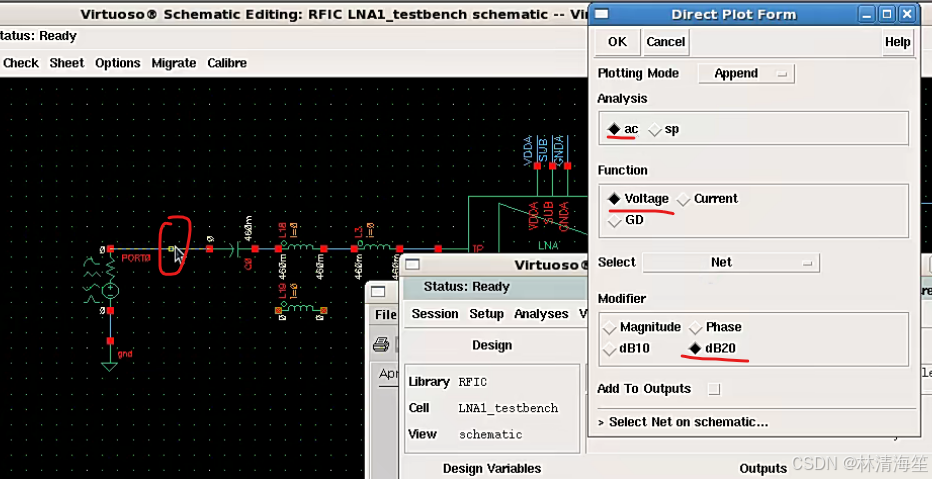

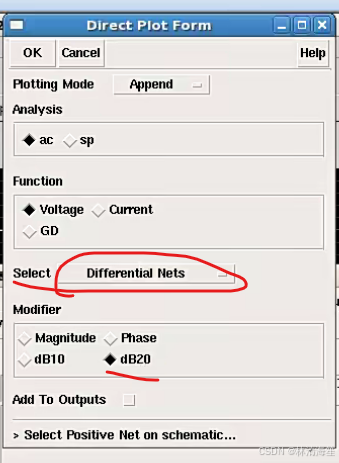

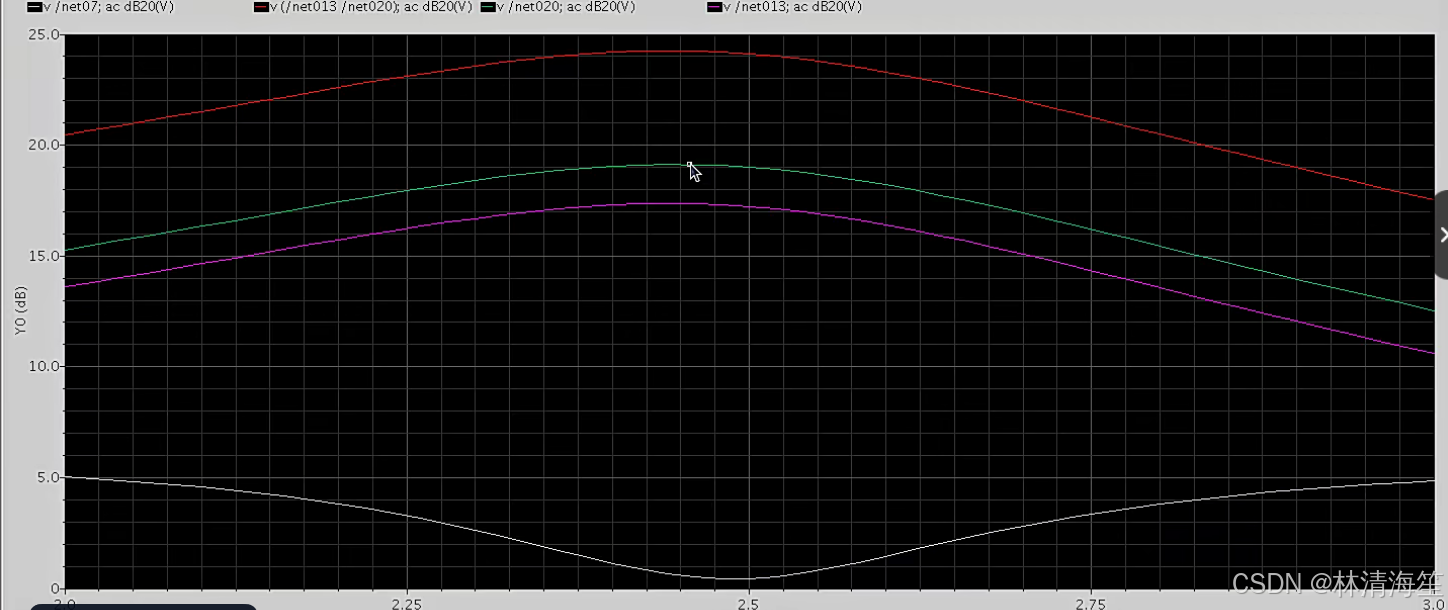

- 我们再来看交流AC小信号的仿真,来查看电压增益为多大的值。

- 添加AC仿真器

- 在testbench里面,只有输入的port设置了1v小信号,输出port和偏置电压都是直流

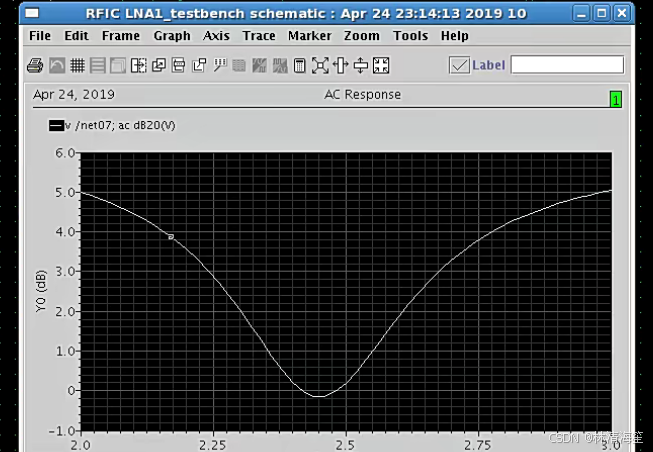

- 首先我们把输入的ac电压幅度给画出来

- 能够看到输入port在不同频率点范围内由于阻抗匹配不一样,在输出端信号的幅度是不一样的。

- 在输入匹配较好的一段2.4GHz左右,基本上是等于0dB的值,即对应幅度为1v。

- 在输出端,由于是差分信号

- 能够看到增益是非常高的,达到30dB左右。

- 增益可以通过子电路的负载电阻进行调节

- 当我们把负载电阻从200欧减小到100欧时,即减小一半,增益会下降6dB,到24dB左右。跟设计参数要求比较接近。

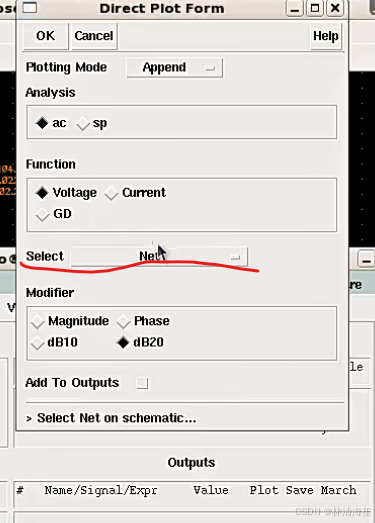

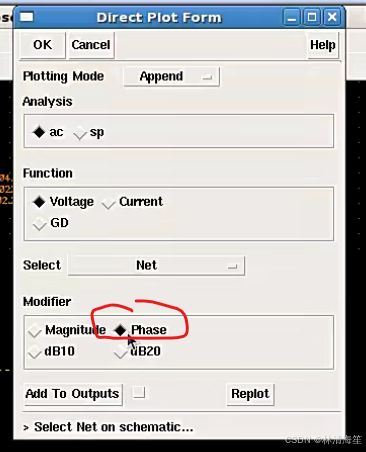

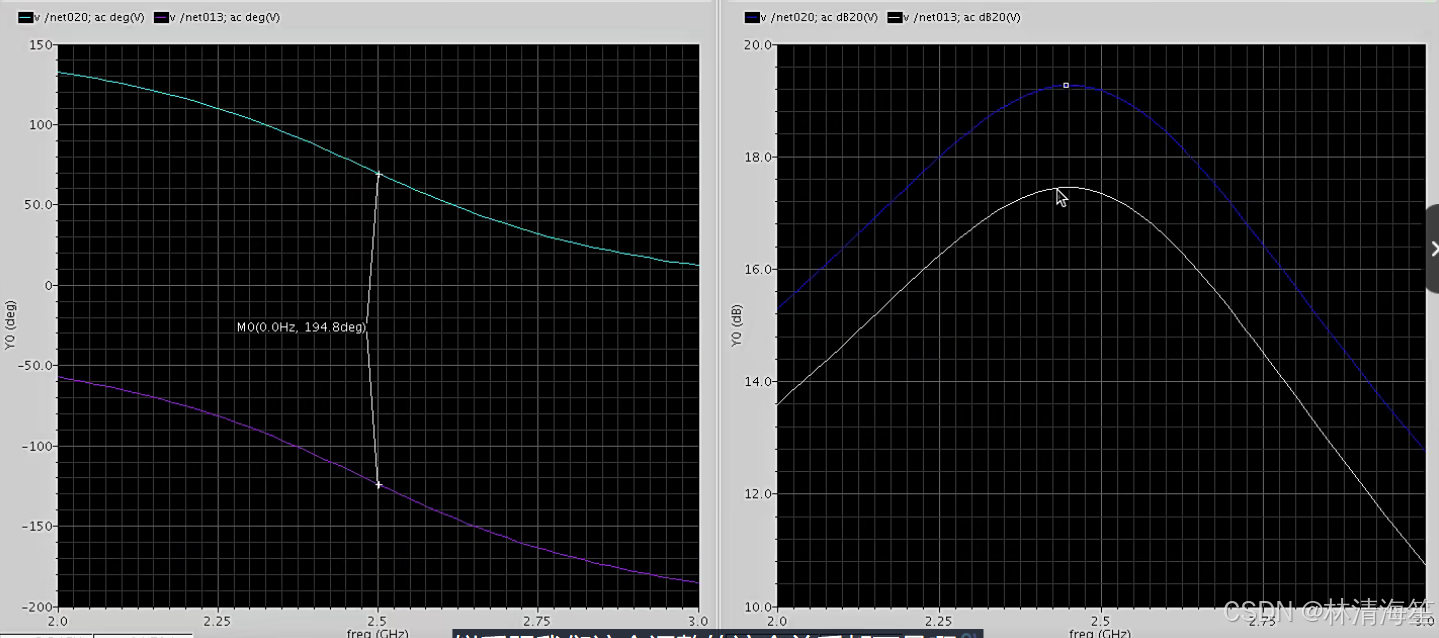

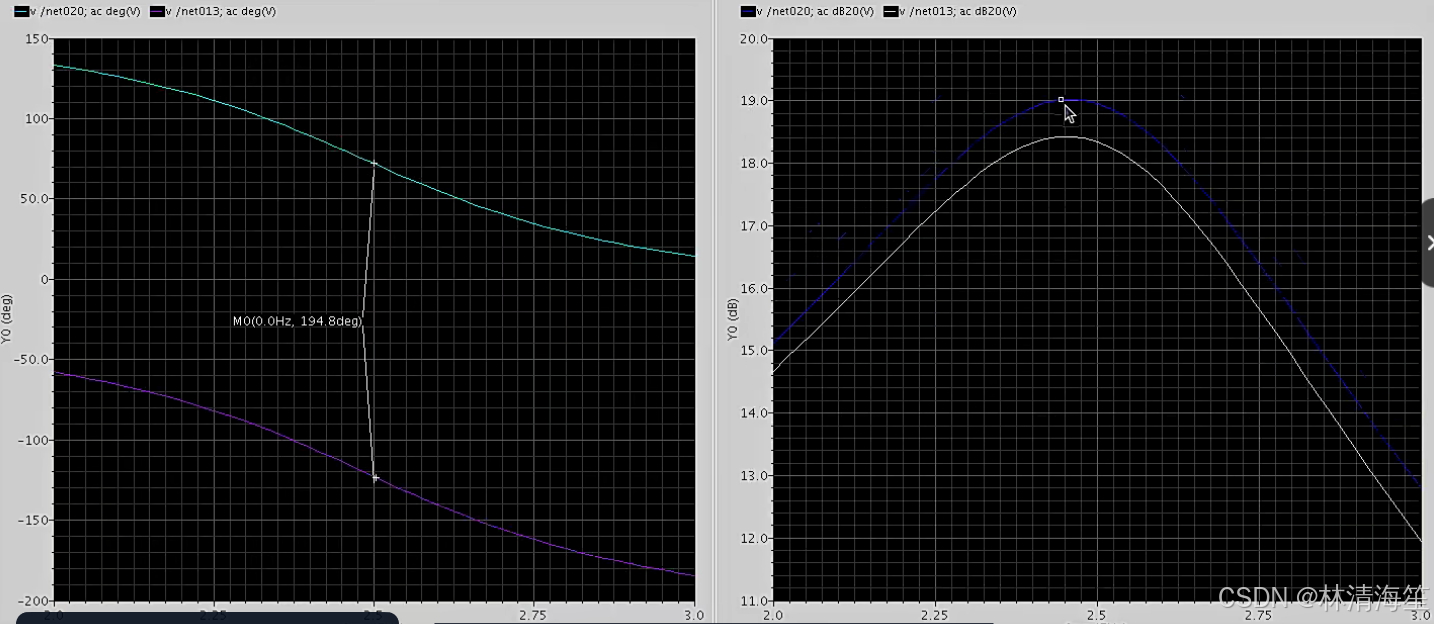

(2)相位和幅度平衡性

- 由于我们设计的低噪声放大器是一个单端转差分输出的结构,因此还需要去关心它的另外一个指标值是输出差分信号的幅度平衡性和相位平衡性,即幅度是否相等,相位是否相差180度反相。

- 修改ac仿真器的网络为单端,然后分别选择N端和P端,绘制出两条曲线。

- OUTN大概是在19dB,OUTP大概是在17.3dB,存在1.6dB的增益差。因此需要调整两边的平衡性

- 调整平衡性有很多的方法

- 方法1:调整P端的晶体管尺寸

- 方法2:调整隔直电容的尺寸

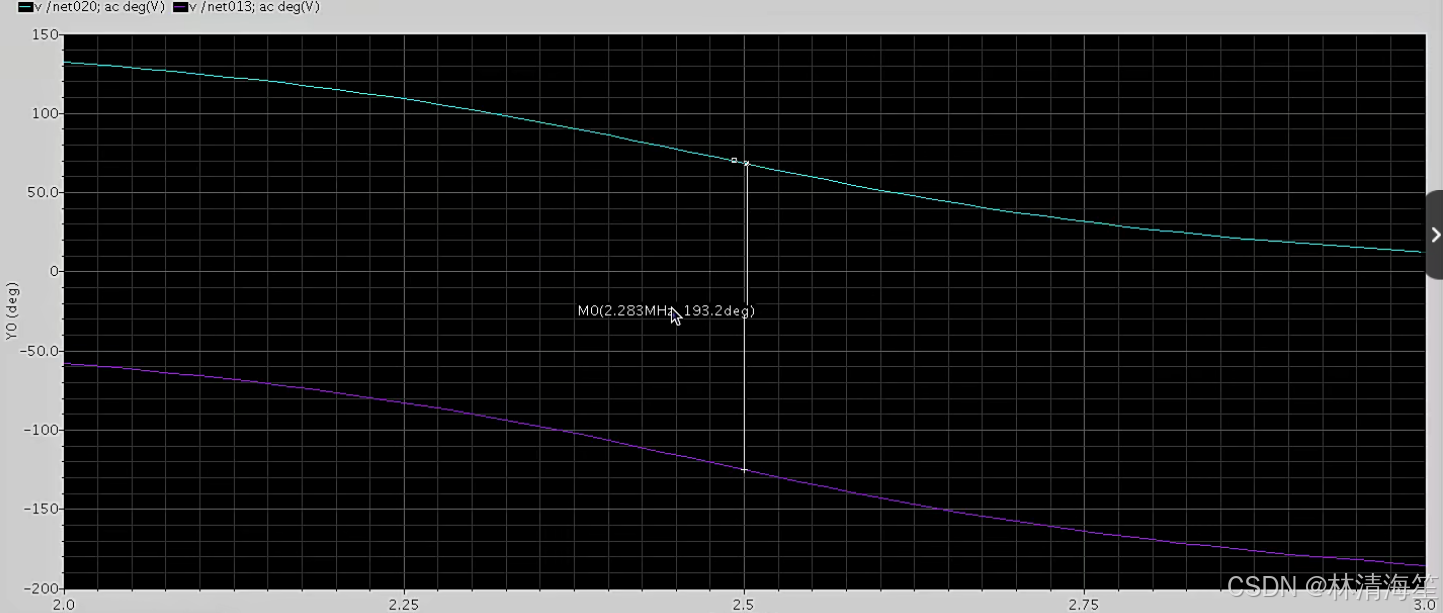

- 然后我们再来看相位平衡性。

- 可以看到负端(浅蓝色)在2.5GHz时为68度,正端(紫色)在2.5GHz时为-125度。两个的相位差是在193度左右。这里并不是严格的180度相位差,是由于一些寄生参数的影响。

- 我们需要加大负端的晶体管尺寸,将finger数增加到22。

- 重新加载,负端增益为19.2,正端增益为17.45。还是差了2dB的值,没有太大的变化。

- 因此,我们可以尝试去改变P端的负载阻抗的大小。将前面修改的负端晶体管尺寸调整回来,在尺寸相等的情况下,去调整负载阻抗的大小。

- 将负载阻抗的值修改为130欧姆,再去看调整后增益变化情况。

- 能够看到,增加负载以后,增益的差值有了一定程度的减小,但是相位还是没有太大的变化。

- 然后我们再来看看调整阻抗后输入匹配的特性,输入阻抗的实部有了一定程度的增加

- 再来看看增益曲线和噪声的特性。输入匹配的频率偏高了一些,然后噪声系数也有了一定程度的恶化,已经恶化到2.5dB。

- 所以目前来说调整这些参数作用不大。

- 我们暂时先不去管这一部分的增益差异,负载阻抗先还是设成相等的值100欧。然后隔直电容同样的还是设成3pF。

6. 晶体管参数调整(multiplier并联形式)

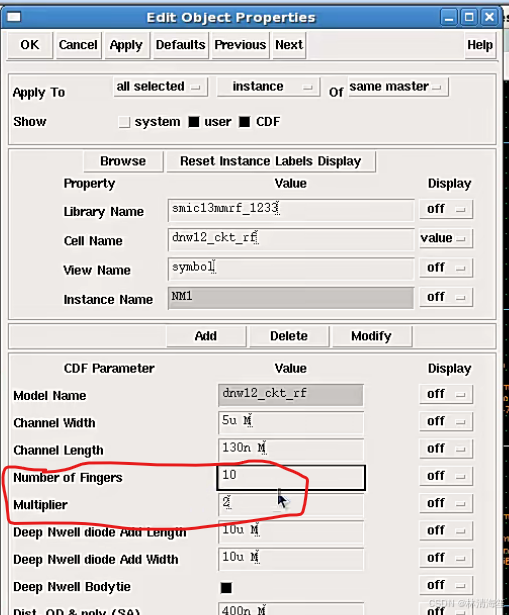

- 为了晶体管能够更好的去匹配,我们可以把晶体管的个数(multiplier)改成偶数个,特别是在做这种差分电路这种结构的时候。那么在做版图布局的时候可以做到更好的十字交叉匹配,这样电路的匹配特性就能够做得更好。所以不是很建议晶体管个数都设为1,通常设置成2或者是4。

- 我们对晶体管参数进行修改,原先finger数为20个,我们可以设置成单个晶体管10fingers,两个晶体管并联的形式。

- 由于晶体管的个数发生了变化,因此我们还需要再去重新仿真确认一下电路性能参数是否还满足之前设置的要求。

- 仿真结果来看,基本没有什么太大的变化。

1004

1004

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?