Chris射频IC教程学习笔记

1. 教程简介和BLE射频收发机系统结构介绍

2.1 低噪声放大器电路结构以及单晶体管仿真分析

2.2 LNA的testbench搭建及S参数仿真优化

2.3 LNA噪声、线性度及稳定性仿真分析

2.4 LNA增益控制,工艺角偏差,高低温对性能的影响

2.5 LNA完整电路设计及蒙特卡洛仿真

2.6 LNA版图设计及DRC/LVS验证

4 D类功率放大器PA电路设计/loadpull仿真/输出功率及效率PAE计算

(未完待续,还会继续更新)

一、完整LNA设计介绍

- 首先打开LNA核心电路设计文件

- 由于在高低温变化和工艺偏差下,工作电流要保持在恒定的值,因此在实际电路设计中不会采用这种偏置电压的方式,而是另外采用偏置电流产生的方式。

- 然后打开本节课用到的LNA完整电路设计文件

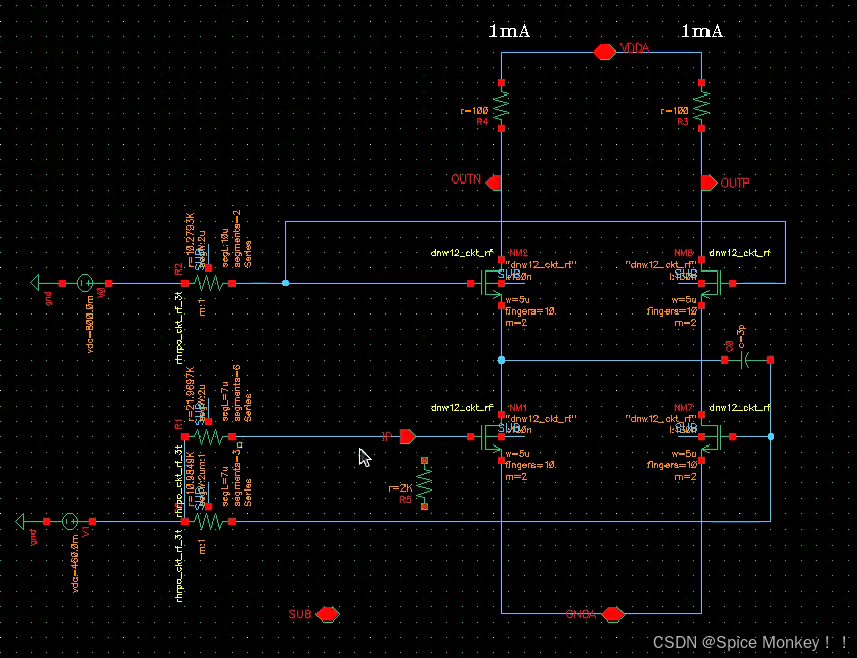

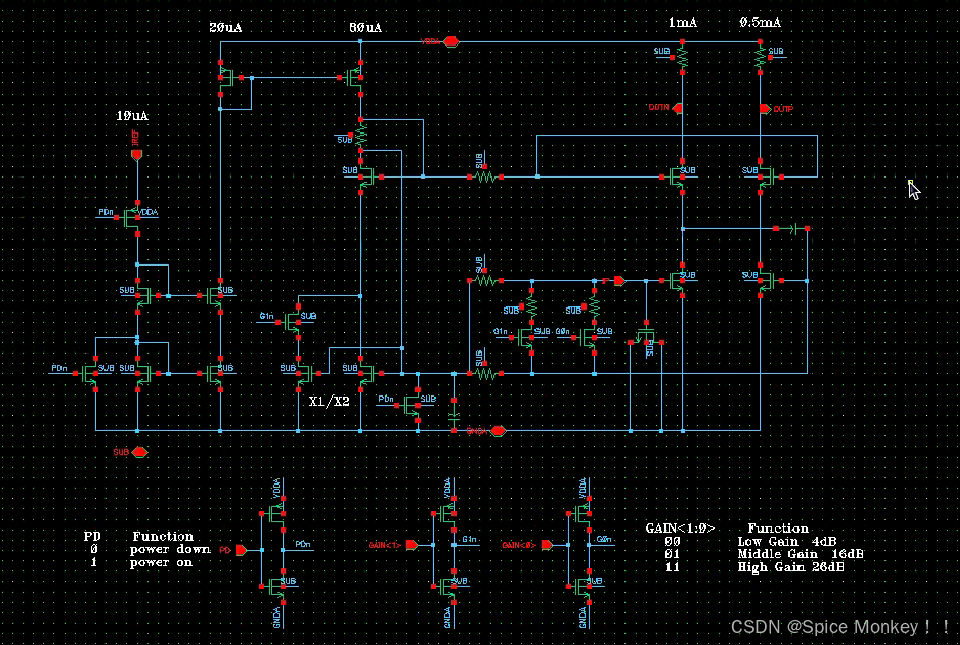

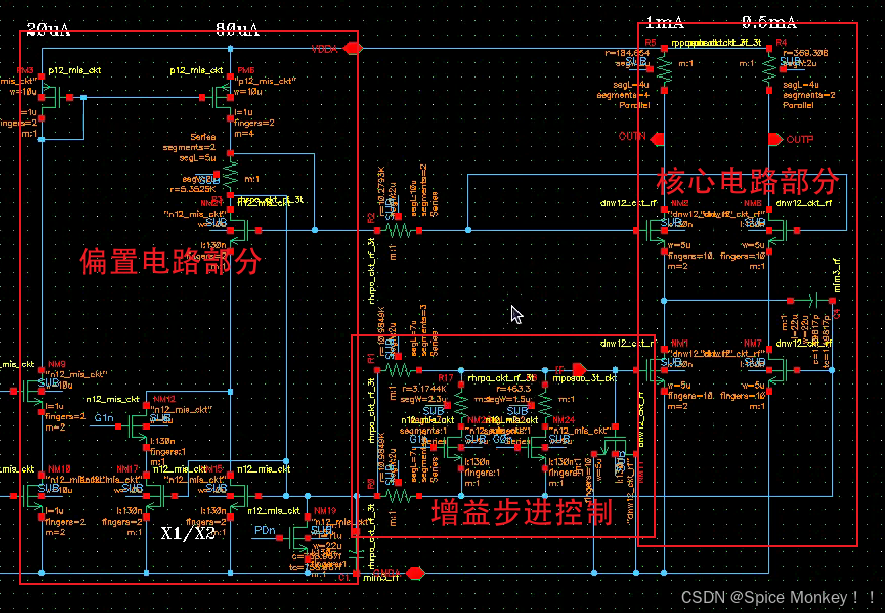

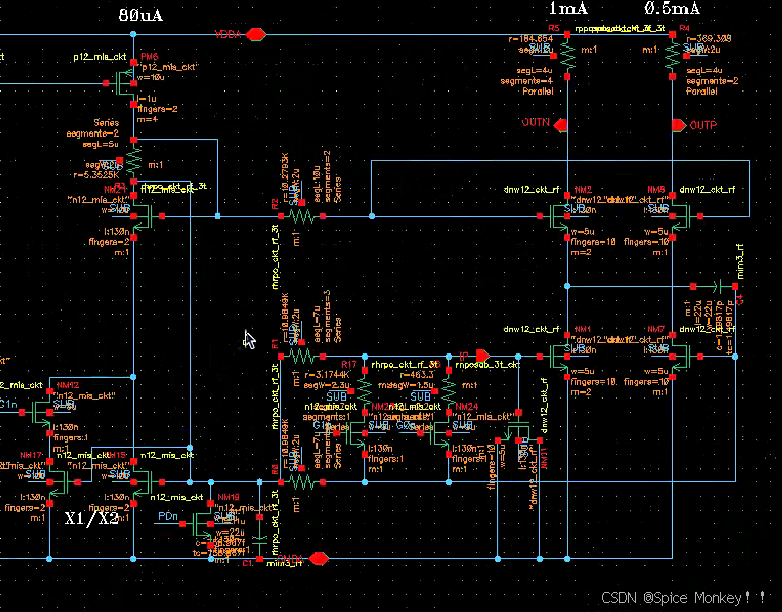

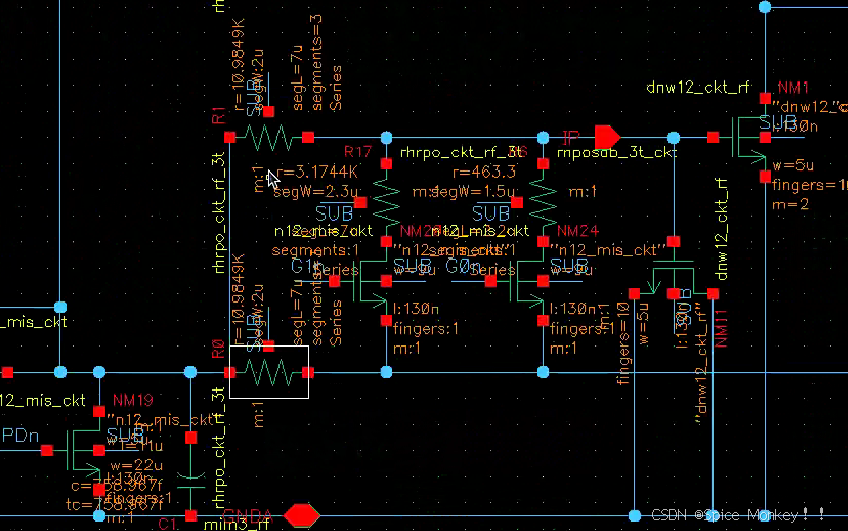

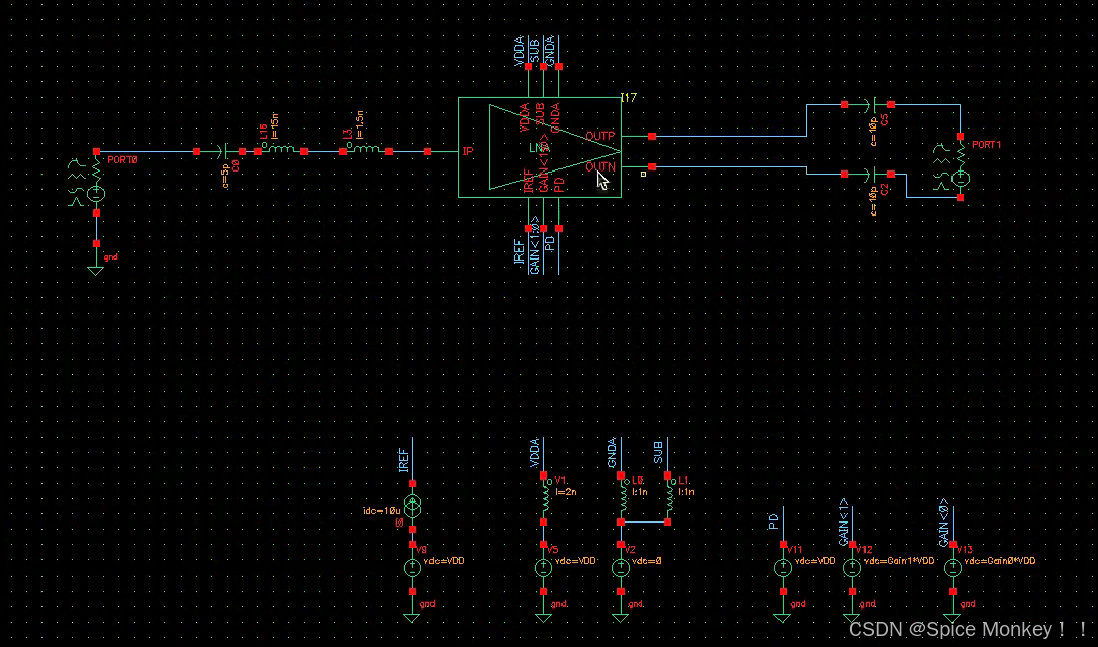

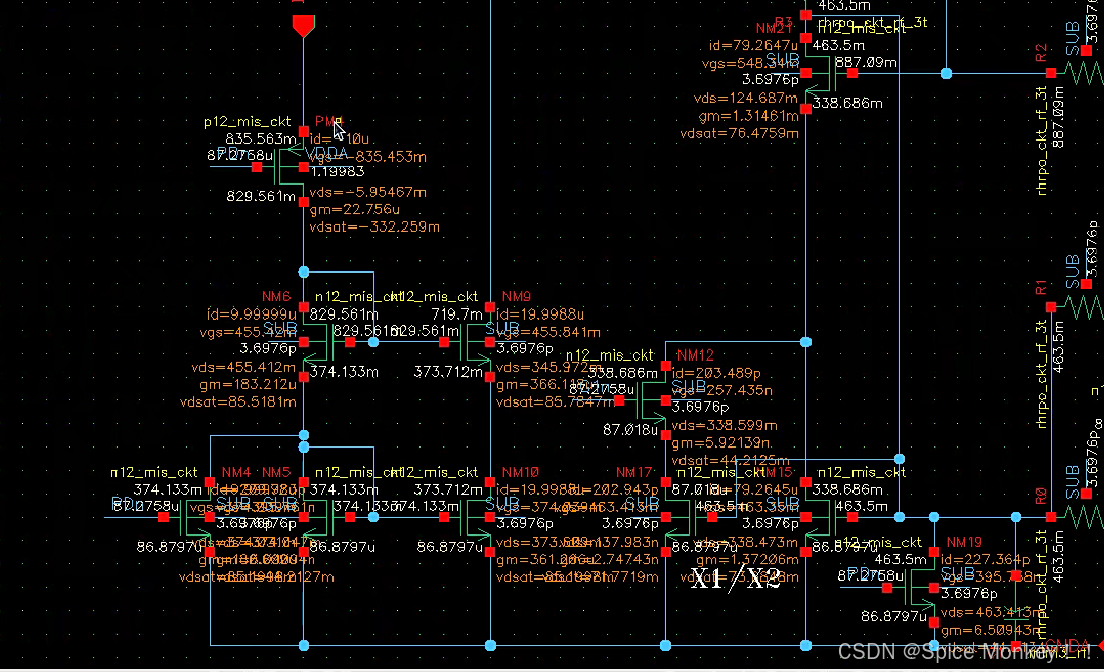

- 下图为完整的LNA原理图设计

1. 整体电路布局介绍

- 在核心电路部分的电路是和前面所仿真的电路完全一样的,但是另外还增加了增益步进的控制,和偏置电路部分

2. 偏置电路部分

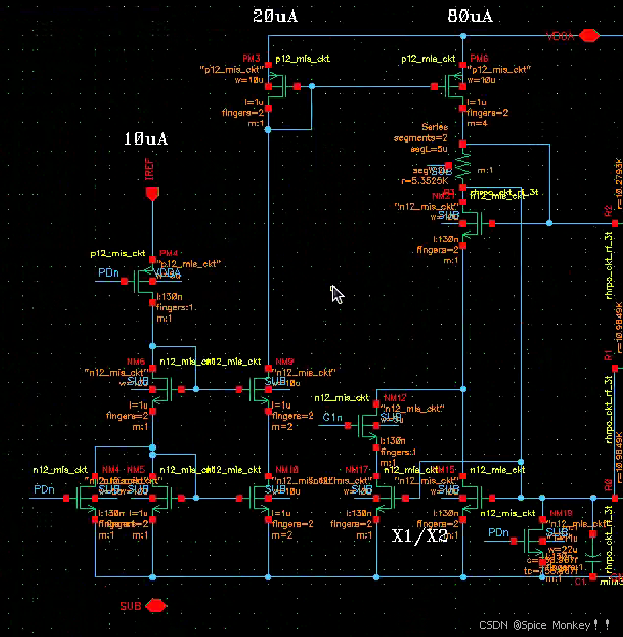

(1)产生偏置电流的电流镜(两次)

- 由于核心电路采用恒电流源的偏置的方式,因此需要有外部输入的参考电流10uA,这个电流通常是由Bandgap电压,然后再经过恒定的运放,再经过恒定的电流源去作为参考的电流源。

- 可以看到参考电流源输入到低噪放内部的时候,是做了两次电流镜的。

- 第一次的电流镜采用两层的层叠结构,准确度会更高。电流镜两边的电流比例关系,主要是有底下这一层的晶体管尺寸比例关系。而沟道长度调制效应来决定准确度的问题,因为在上面增加了cascode这一层,所以底层的电流镜晶体管的漏端电压能够保持相等,因此沟道长度调制效应对电流镜两边都是相同的影响,电流镜的镜像比例会准确一些。

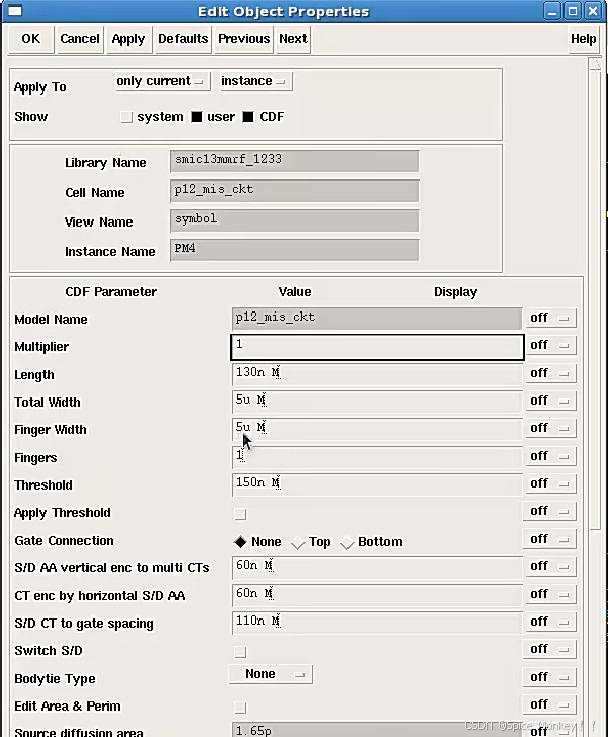

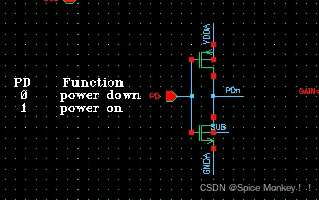

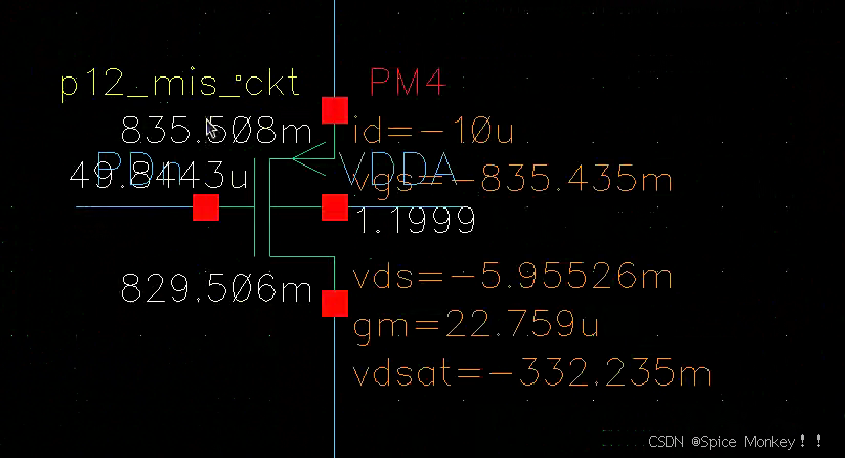

- 输入的电流元件里面,对低噪放做了power down的控制,也就是关闭和开启的电源开关(PNn信号)。通过PMOS(PM4)去切断输入的偏置电流。

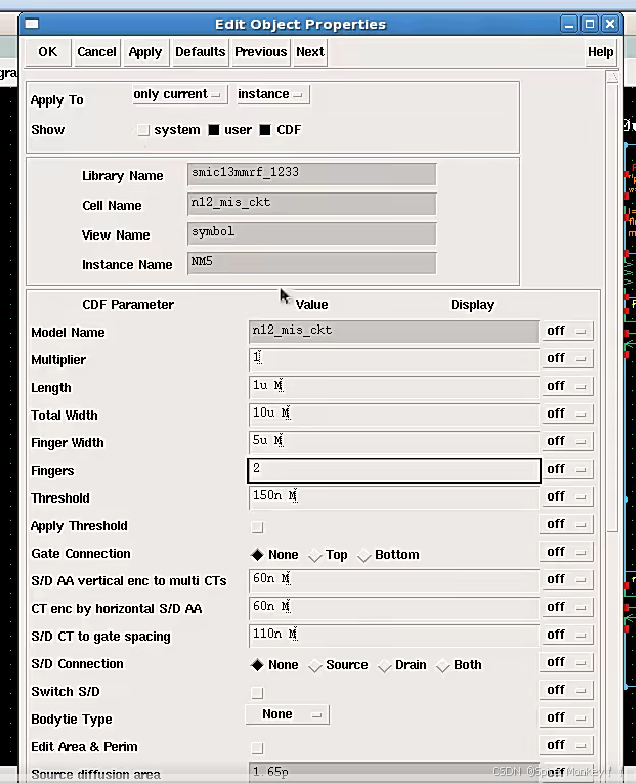

- PMOS下面的第一层的晶体管(NM6和NM9)为cascode级

- 除此之外,PMOS下面的第二层NMOS电流镜(NM5),其栅极通过一个受通过power down开关控制的MOS晶体管(NM4)拉到GND上。这样就当power down导通工作的时候,就可以把输入进来的偏置电流完全断开了,然后输出的电流镜也不会有任何的电流的输出。

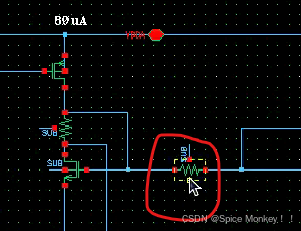

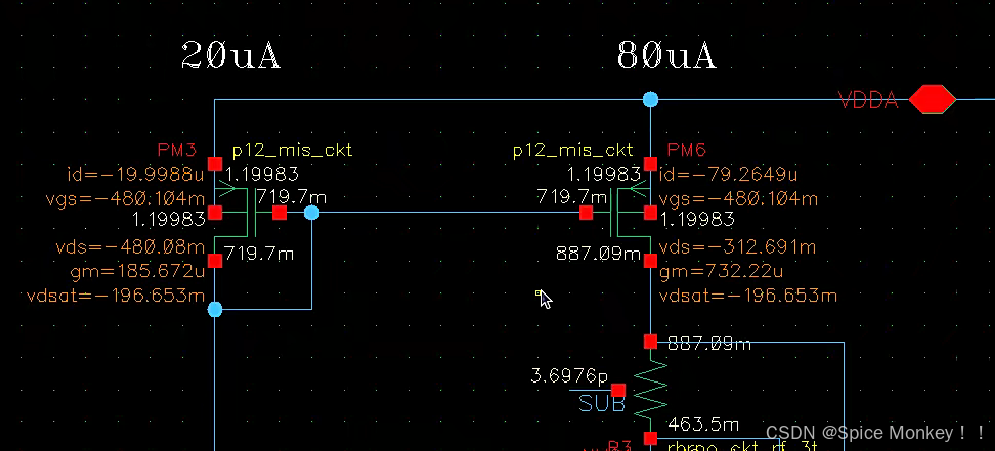

- 第二次的晶体管输入电流为20uA,又通过PMOS晶体管(PM3和PM6)进行镜像的操作,放大倍数是1:4的关系,输出80uA的电流。在这里没有采用cascode结构了。

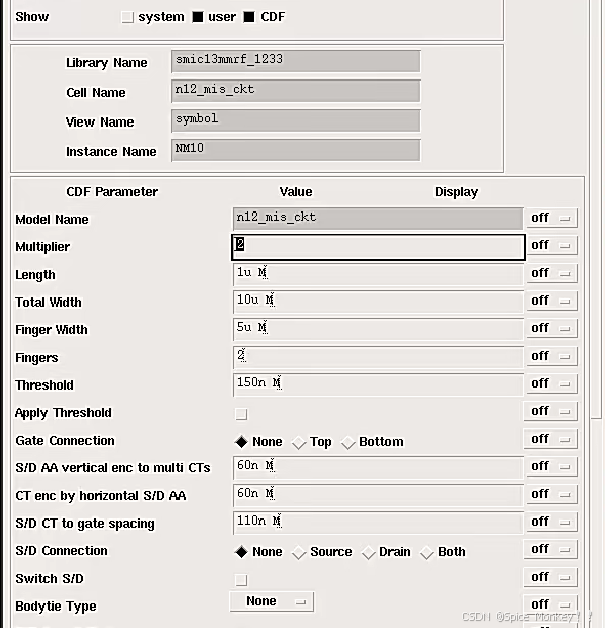

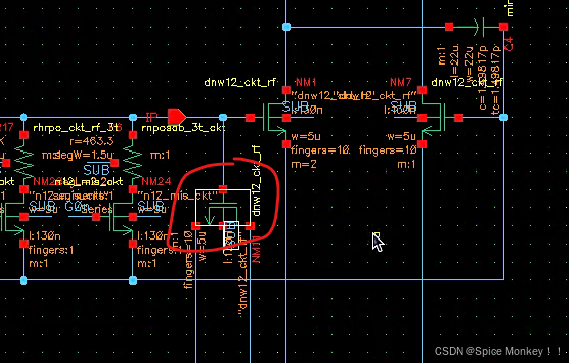

第一次电流镜

-

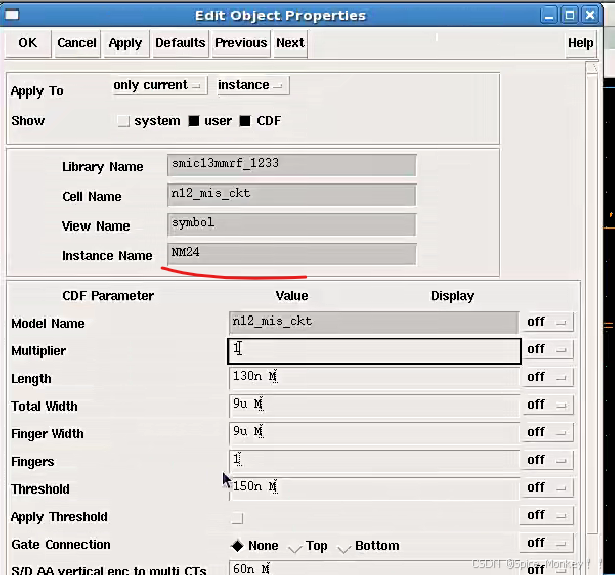

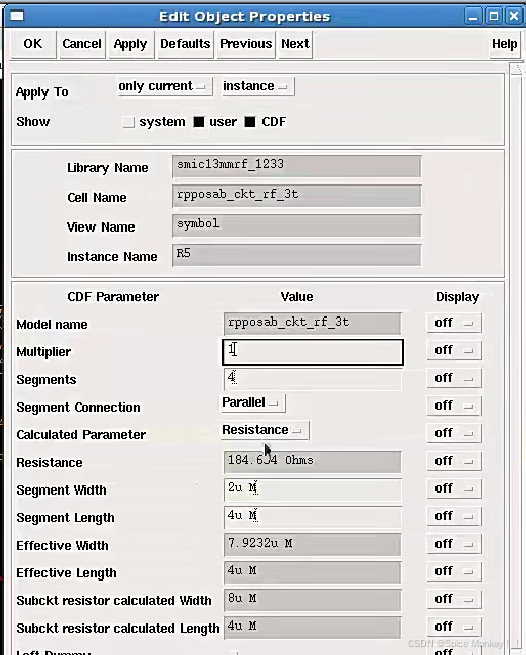

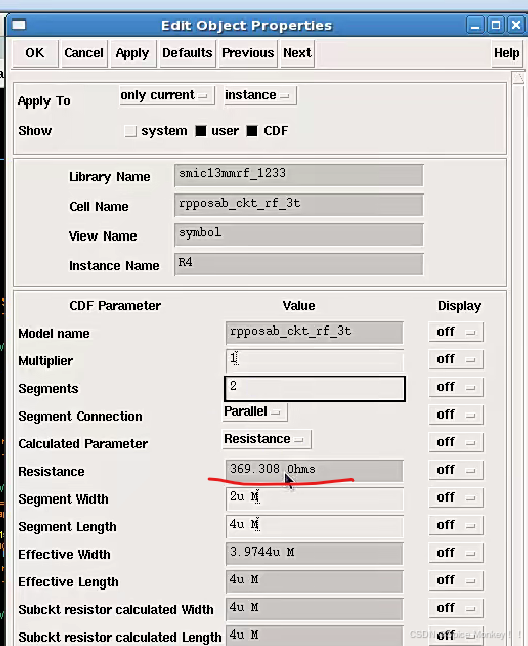

开关的PMOS晶体管(PM4)的尺寸这里设置的比较小,用的是最小沟道长度130nm,1finger 5um的宽度,来作为开关

-

第一次的电流镜的输入二极管连接型晶体管,其并联个数为1个

-

第一次电流镜镜像后的晶体管,其并联个数为2个。因此这个电流镜能实现二倍放大电流的关系

-

而电流镜上面的cascode级晶体管(NM9)采用跟下面一层晶体管相同的尺寸

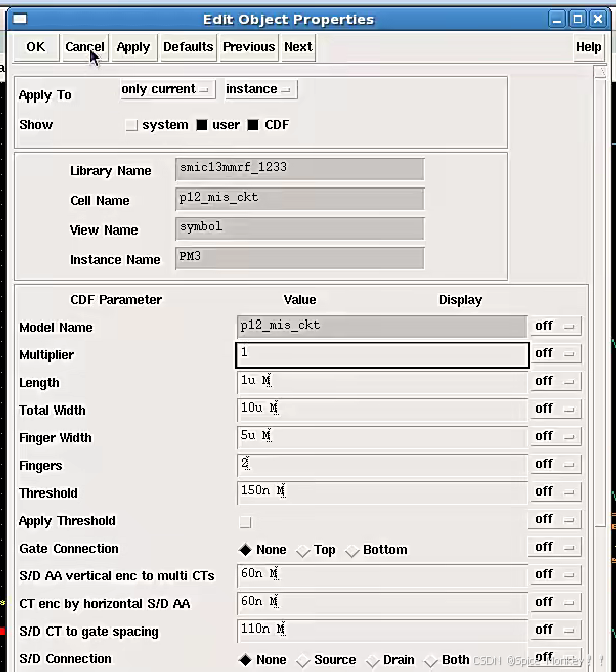

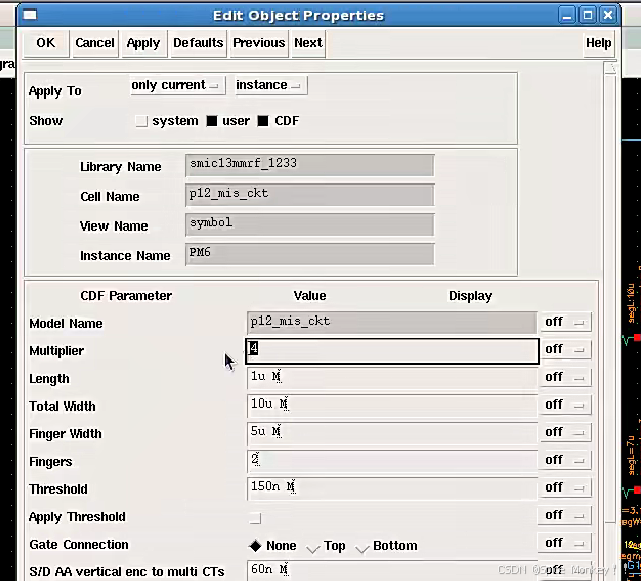

第二次电流镜

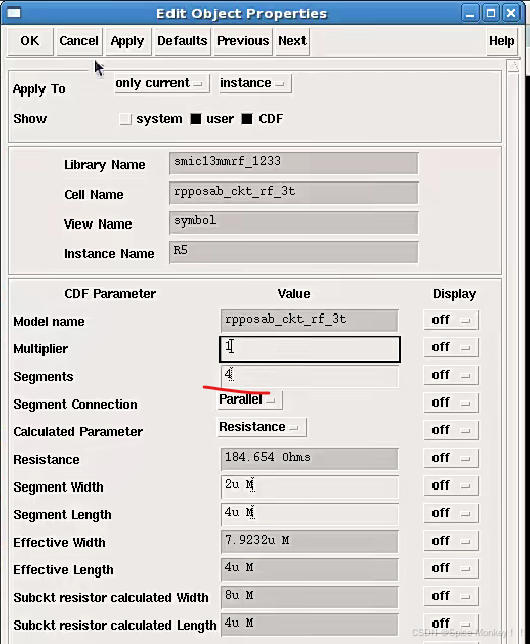

- 第二次电流镜的输入的二极管连接型晶体管

- 电流镜输出的晶体管并联个数为4个

(2)输入核心电路的电流镜

- 最终得到了80uA的电流,这些偏置电流最终使用来给核心电路共源极Cascode晶体管提供直流镜像偏置电流的。

- 但是在实际的电路设计上从80uA电流到核心电路的输入晶体管还是一个电流镜的关系,通过电流镜的方式来实现输入晶体管的栅极电压的偏置。这样即使随着工艺偏差或者温度的改变,输出的电流也能保持不变,主要是有电流镜的比例关系来决定的。

- 可以看到,80uA的电流其实产生了两个镜像电流的偏置电压。

- 第一路电流流到下面来以后,通过晶体管(NM15)进行电流镜的操作,有这个电流镜镜像到右边核心电路的输入晶体管的栅极。

创新:低漏电压方法

- 但是我们发现这个电流镜的输入晶体管并没有直接采用二极管型的连接方式,而是串联了一个电阻后,又叠加了一个cascode级的晶体管的偏置方式。可以产生低漏端电压的电流镜方式。

- 这种晶体管的连接方式主要是为了电流镜输入晶体管(NM15)的漏端电压。因为如果直接采用左边产生恒定电流部分的电路的二极管型接法的话,会在漏端产生相对较高的电压值,因为其至少会有一个电压阈值Vth,这是很大的电压消耗。这样给核心电路提供的偏置电压会非常的高(Vdsat>Vgs-Vth),会带来线性度方面的影响。

- 电阻的大小取值。由于电阻两端的压降就等于下面电流镜输入晶体管的VDS(漏端和源端的电压差值),因此电阻值大小是根据下面电流镜输入晶体管的VDS电压值而调整的,以最小的电压范围实现正常的工作状态。

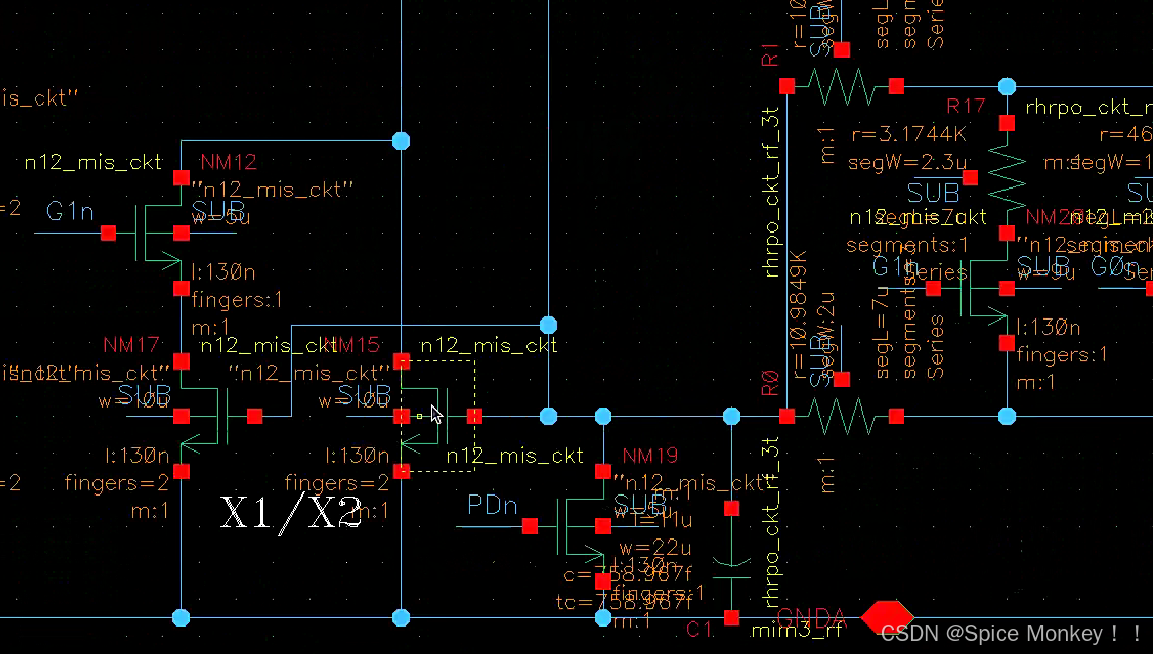

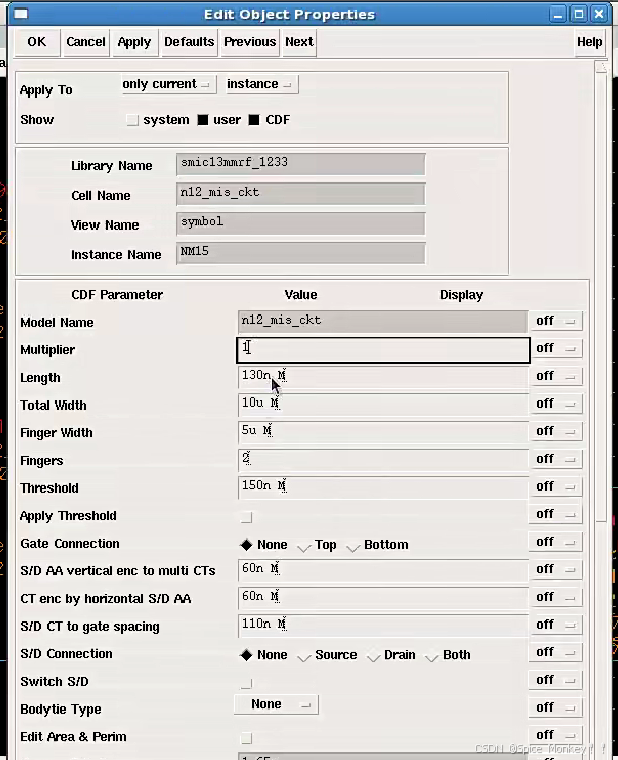

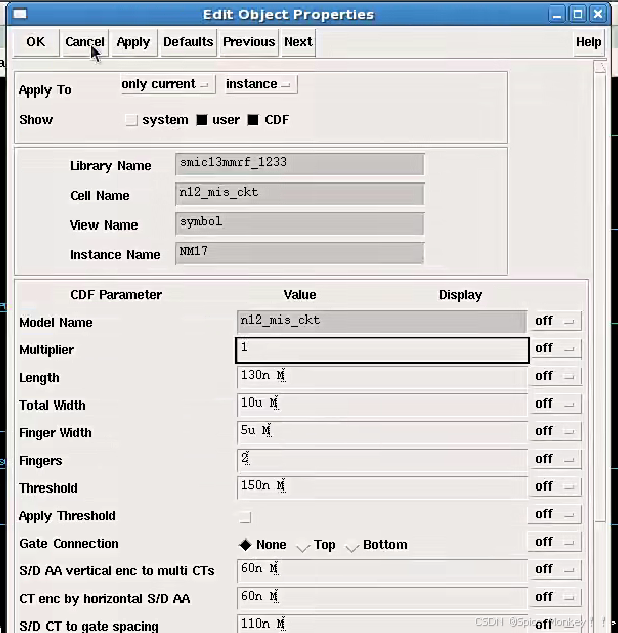

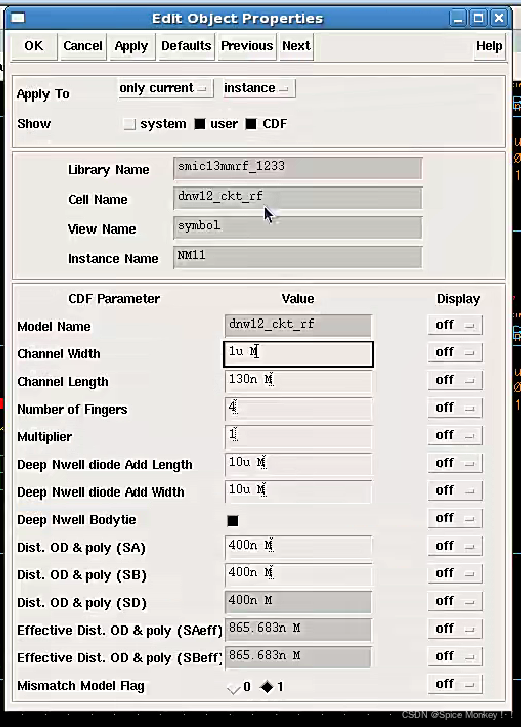

- 电流镜输入晶体管(NM15)参数设置如下

隔离电阻(输入核心电路的cascode级)

- 而给核心电路中的cascode级晶体管是由NMOS晶体管(NM21)的栅极来提供偏置电压,等于上面pmos电流镜输出的电压,使得对电源电压需求不太高,这种结构在低压下会采用的较多一些,通过串联电阻产生低压的方式。

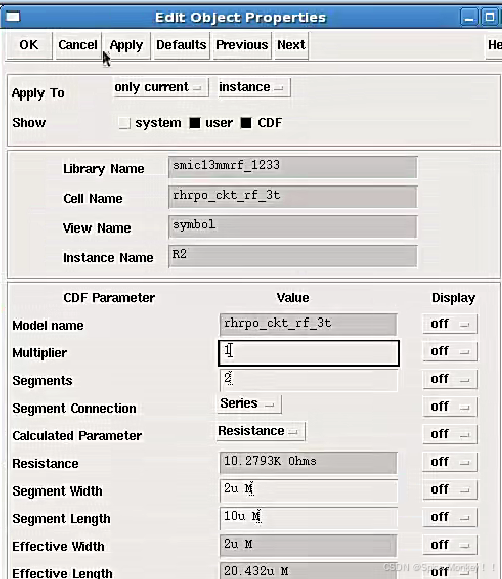

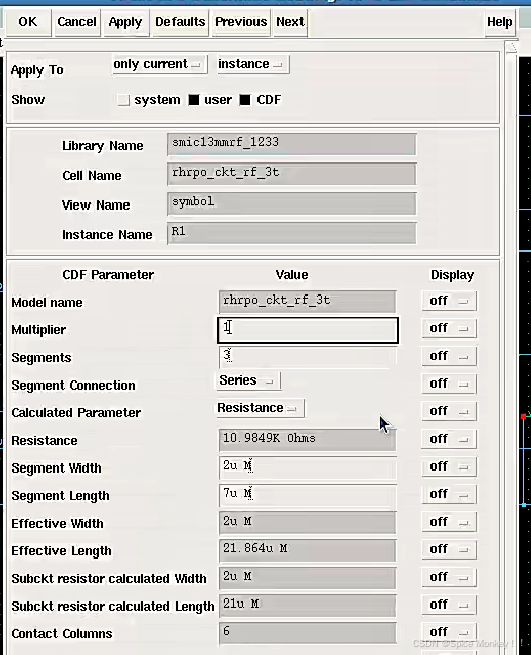

- 偏置的隔离电阻都选用10k欧的电阻阻值。

- 输入的隔离电阻采用高点电阻率的类型

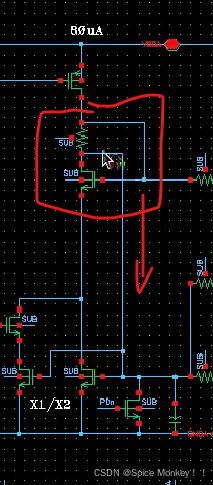

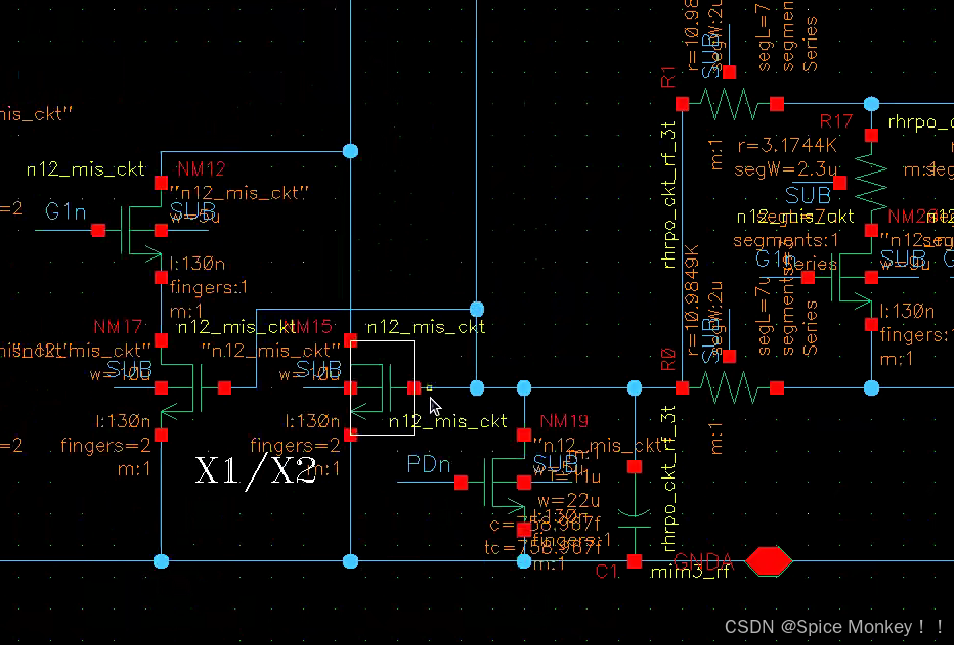

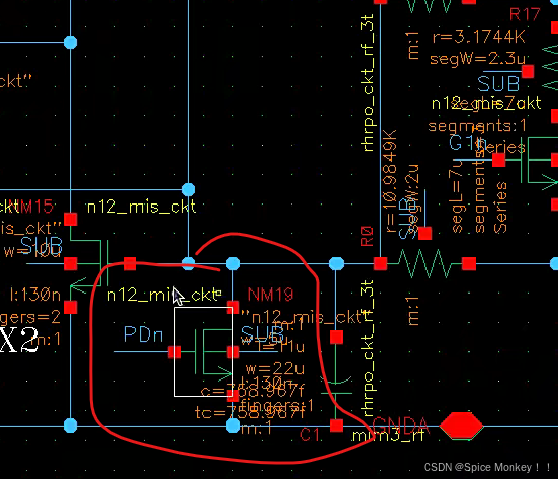

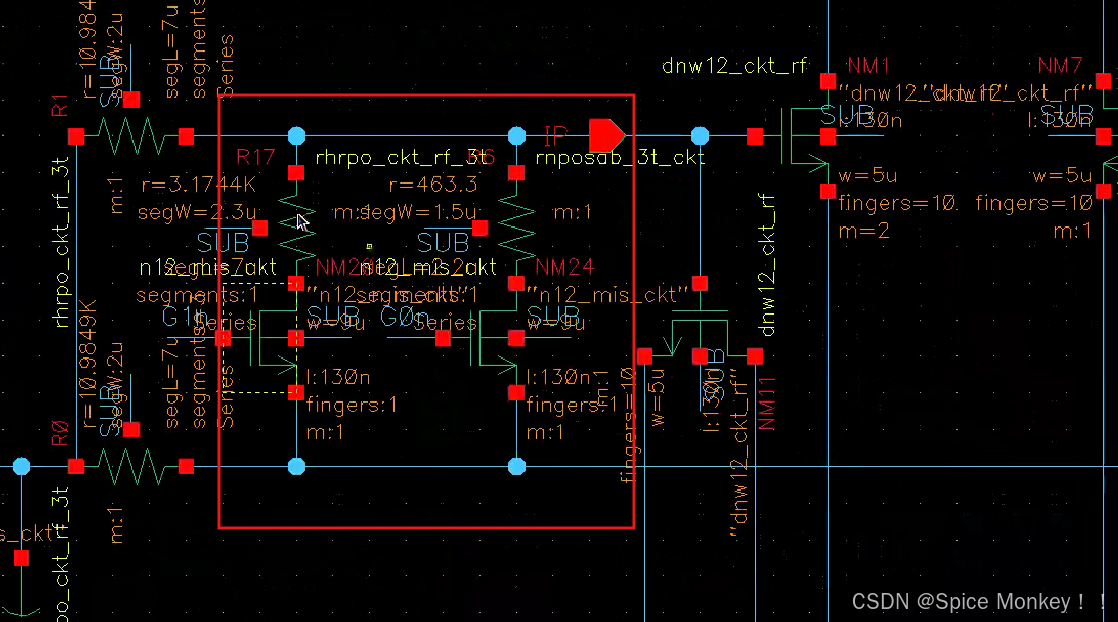

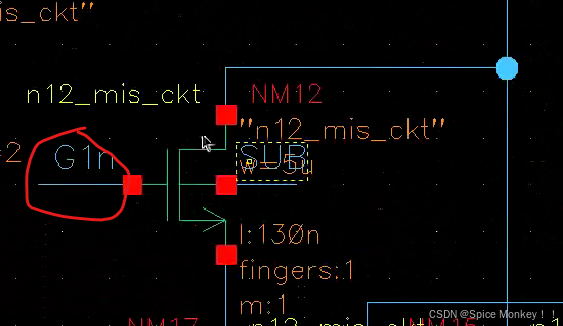

电流镜开关及改变尺寸电路

- 在偏置电路部分还做了特殊处理,增加了额外的开关电路(NM12和NM17)。通过增加这个开关电路可以去改变电流镜晶体管(NM15)的尺寸大小。

- 当开关晶体管(NM12)关断的时候,改变电流镜尺寸的晶体管(NM17)就不会流过电流而工作,使输入到右边核心电路的电流增大两倍。

- 当开关晶体管(NM12)导通的时候,(NM17)和(NM15)同时工作,使输入到右边核心电路的电流减小一半。

- 对电流镜输入晶体管进行尺寸的变换,并联了另外的晶体管(NM17),其尺寸跟输入晶体管一样

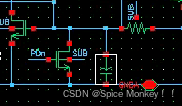

- 而在对核心电路输入晶体管的电流镜,也有Power down控制开关(NM19),通过PDn控制信号,当导通的时候就会把偏置电压源的电流流向地,这样核心电路的所有的晶体管都会全部关闭,不会有漏电流的产生

- 在这个输入的控制开关上,还在内部做了反相器的驱动,产生反向的控制信号来控制整个电路的开启和关闭。

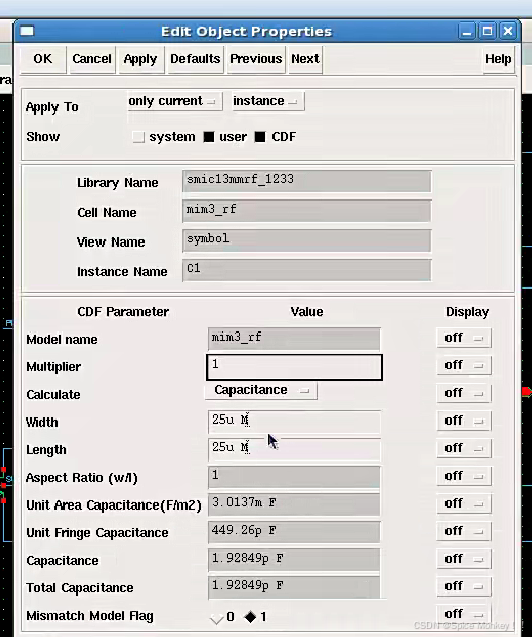

滤波电容

-

此外还在偏置电路里部分增加了滤波电容

-

其容值在700fF左右,选这么小的容值主要是为了版图布局上的考虑。在版图面积允许的情况下,还是希望滤波的电容容值尽量大一些,使各类干扰信号能够滤除掉,让核心电路的工作状态能够更加稳定,杂散的泄露耦合能够更小。

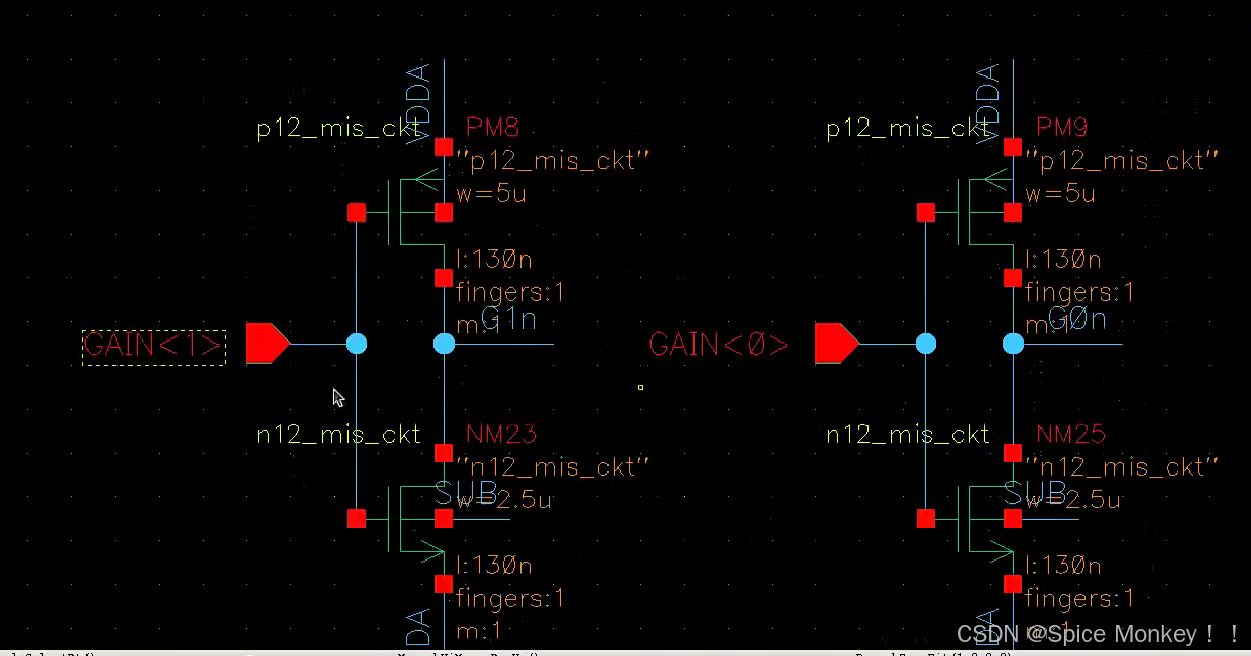

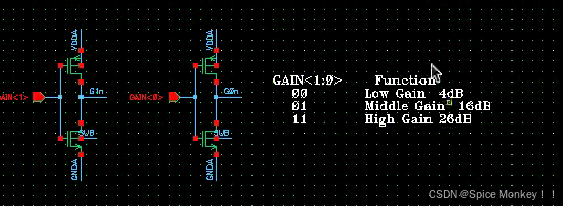

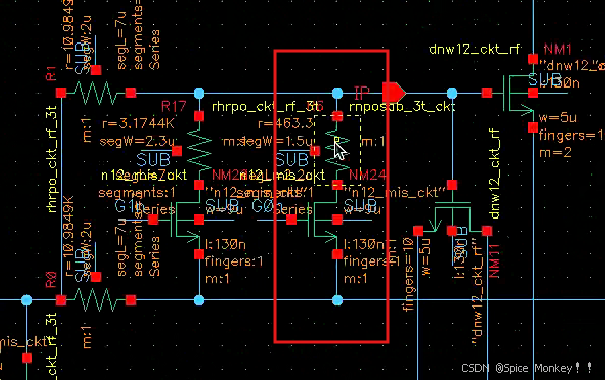

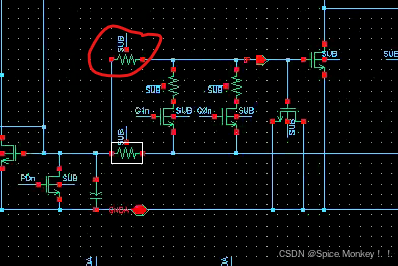

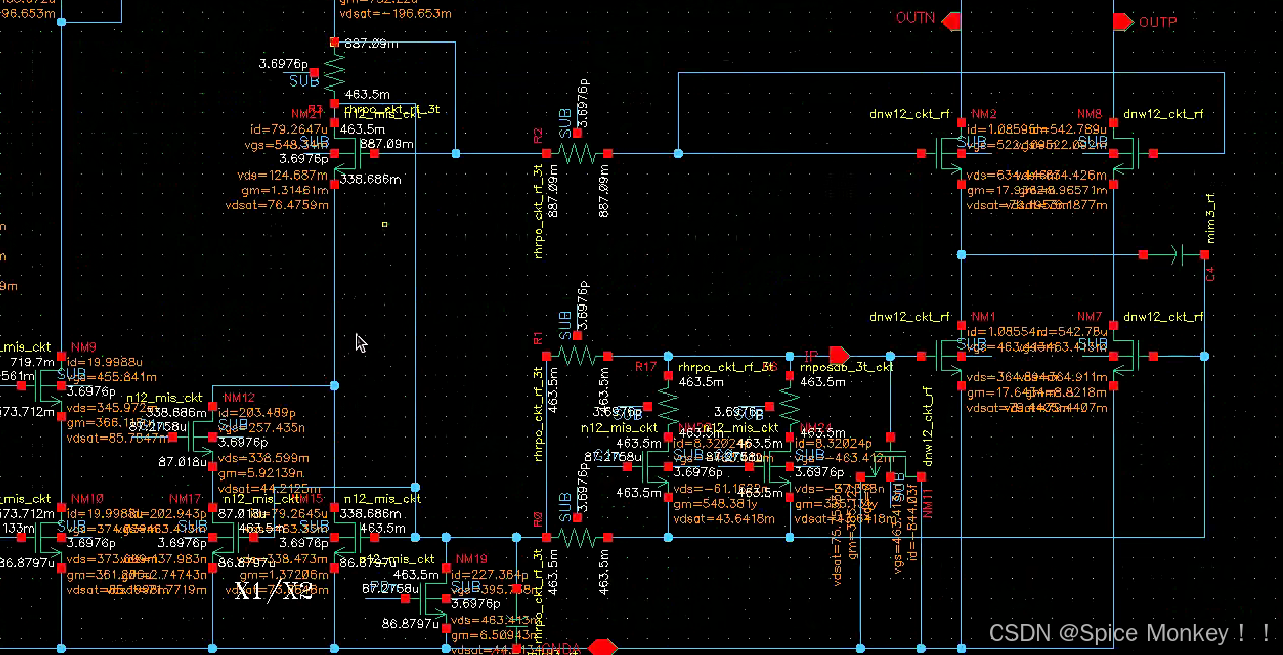

3. 增益控制电路(负反馈电阻+控制电流)

- 增益控制是通过GAIN1和GAIN0两个总线的信号,通过反相器去产生反向的控制电压。

第一档增益控制GAIN1

- 这两个控制信号分别是用来控制输入的反馈电阻,也就是前面在讲核心电路增益控制模式采用的负反馈的方式,通过减小反馈电阻来增加反馈强度,降低最终电路等效的增益。

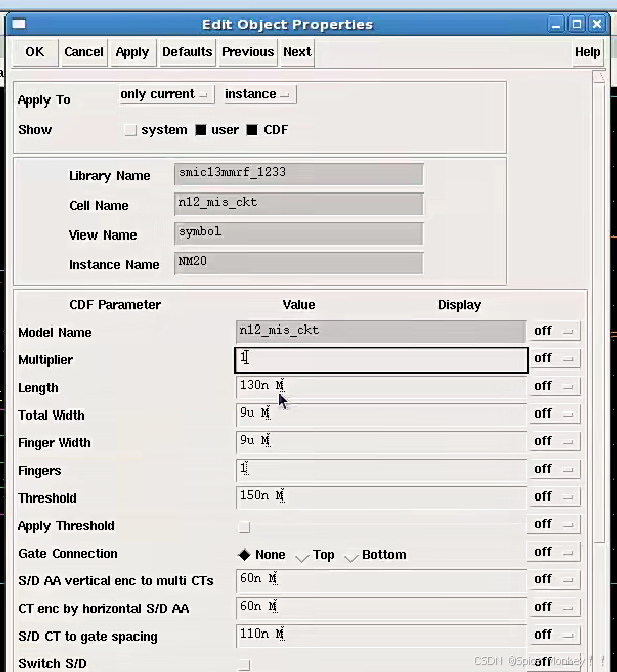

- 由NMOS晶体管(NM20)来控制反馈电阻R17的开关与闭合

- G1n控制信号会同时控制反馈电阻,并控制电流镜的开关晶体管(NM12),让NM17处于导通的状态,使最终直流工作电流减小一半。

- 当GAIN1输入信号为0时,最终输出的增益就会减小10dB

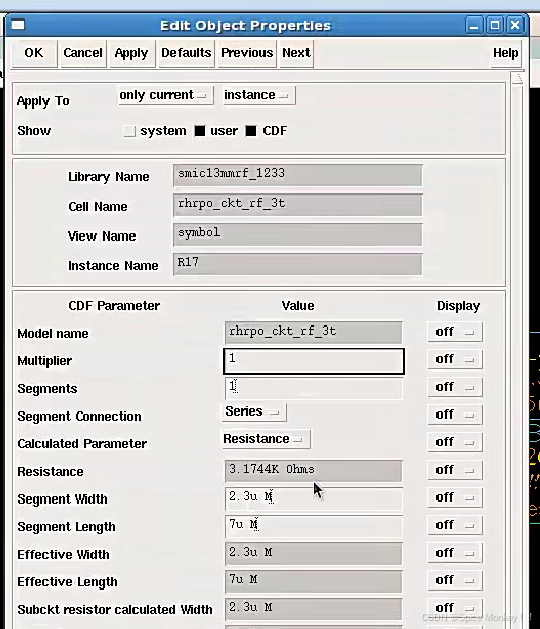

- 并联的负反馈电阻参数如下,相当于是并联了3.17k欧的电阻,再加上控制晶体管导通后的电阻,形成负反馈的控制。

- 控制开关的晶体管尺寸,选择这个尺寸是根据仿真查看导通电阻的阻值,与这个电阻串联后总的反馈阻抗。在根据所需要的增益值来确定最终电阻值的大小和开关晶体管的尺寸。

第二档增益控制GAIN0

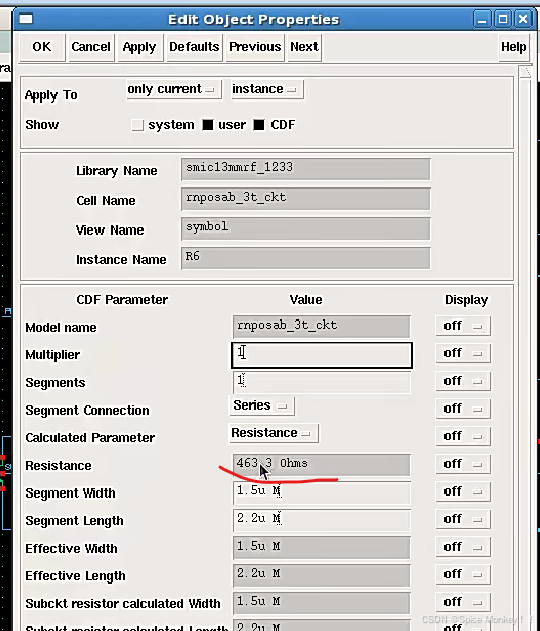

- 第二档GAIN0是额外再并联了一个晶体管和电阻

- 第二档增益控制的反馈电阻是463欧,因此又会降低10dB

- 控制的晶体管参数如下

隔离电阻

- 核心电路的输入级晶体管还串联了两个隔离电阻(R0和R1)接入到其栅极。

- 所以核心电路晶体管的工作电流就跟输入的晶体管的尺寸和电流镜晶体管的尺寸比例有关系。

- 输入的偏置电阻选用11k欧

晶体管电容(减小输入匹配电感)

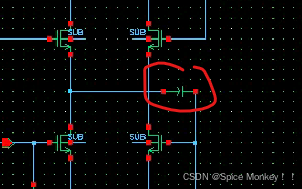

- 在输入的栅极上还并联了一个输入晶体管电容,主要是用于提供输入匹配的。

- 这里我们采用的是MOS晶体管电容。栅极接在输入端,漏极和源极接在GND上面。来实现所要求的比较小的电容。等效增大了输入晶体管Cgs的等效电容

- 增加这个电容主要是因为在核心电路testbench仿真的时候,输入的串联电感会非常大,到25nH左右。这样的电感相对在2.4GHz频率下面,在PCB板上面的分立器件上,20nH的电感性能就不是太好了。较小的输入匹配电感其射频特性才能更好,自谐频率更高,Q值更高。

- 减小输入匹配电感的两种方法

- 增大核心电路输入晶体管的尺寸。输入级晶体管尺寸越大,其寄生电容越大,外部所需要的匹配电感就会越小。这是因为输入总电感值要和输入晶体管的寄生电容Cgs在工作频率下产生串联谐振,阻抗的虚部要完全抵消掉。产生的串联谐振频率是固定的。

- 但有个问题是晶体管的尺寸并不能无限制的增大,因为其会使工作电流增大,使功耗增加,噪声特性各方面的情况都会变得很差。

- 另一种方式是在LNA的外面再并联一个小电容,那么其串联谐振增加额外的电容值,减小串联匹配的电感值。

- 电容如果放在芯片外部,就会增加一个元器件。因为这是一个非常小的电容容值,不允许太大,因为工作频率较高。如果用外部PCB板的分离元器件的电容,用射频电路来做的话,这个电容可能就是一两百fF,这种电容非常小,精度也会要求较高。因此希望能够在芯片内部实现这样的电容。

- 芯片内部做这样的电容有很多种方式,可以是MOS电容,或者mom电容/min电容。

- 芯片内部做这样的电容有很多种方式,可以是MOS电容,或者mom电容/min电容。

- 电容如果放在芯片外部,就会增加一个元器件。因为这是一个非常小的电容容值,不允许太大,因为工作频率较高。如果用外部PCB板的分离元器件的电容,用射频电路来做的话,这个电容可能就是一两百fF,这种电容非常小,精度也会要求较高。因此希望能够在芯片内部实现这样的电容。

- 增大核心电路输入晶体管的尺寸。输入级晶体管尺寸越大,其寄生电容越大,外部所需要的匹配电感就会越小。这是因为输入总电感值要和输入晶体管的寄生电容Cgs在工作频率下产生串联谐振,阻抗的虚部要完全抵消掉。产生的串联谐振频率是固定的。

- MOS的电容容值要根据仿真结果来确定所需电容值有多大。看S参数仿真输入阻抗匹配的情况,来优化并联电容值的大小。

4. LNA核心电路

- 在核心电路部分选用的电阻是180欧姆,是根据完整电路增益仿真以后确定下来的。

耦合电容

- 耦合电容采用1.5pF,对整体性能参数是没什么影响的,也是从版图的面积上考虑的。

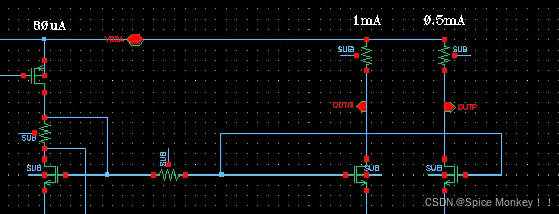

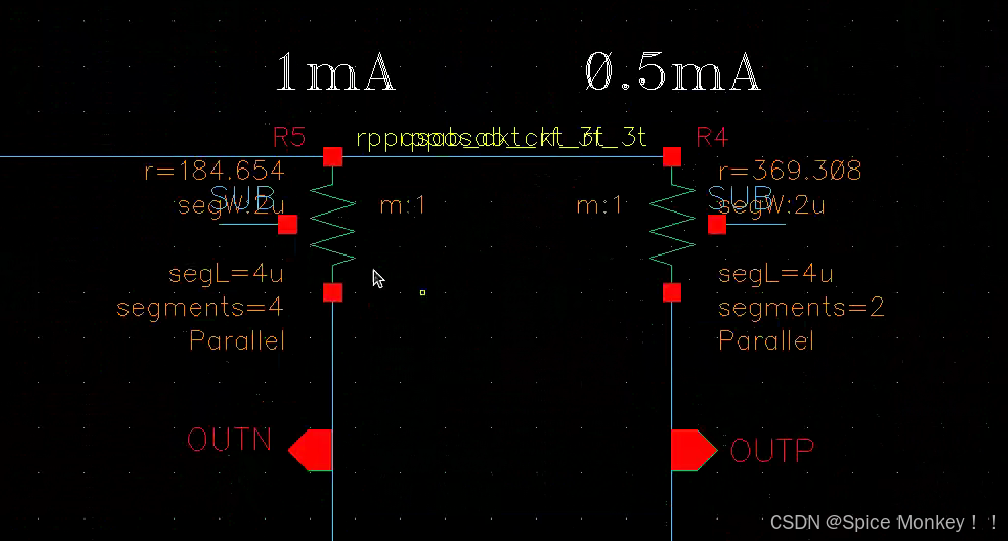

创新:不对称差分电路设计(减小功耗)

- 这里为了使功耗进一步降低,还做了其他优化和改变

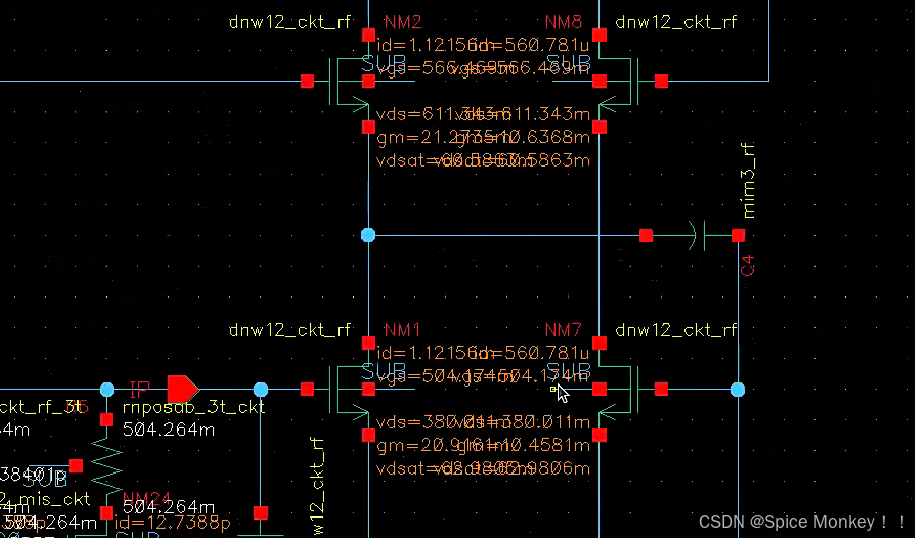

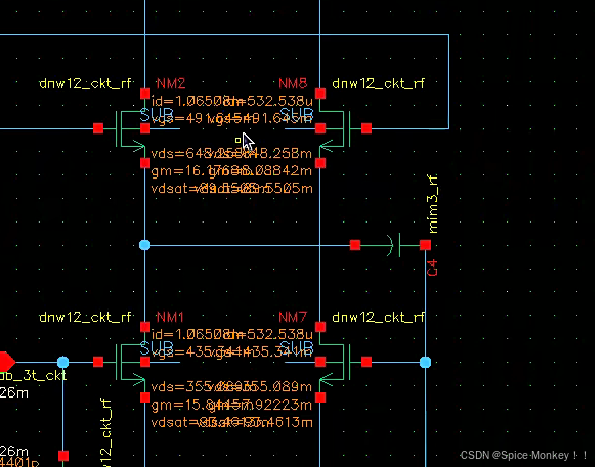

- 可以看到核心电路的右边电路的电流是非常小的,只有0.5mA

- 这是因为把右边的输入和cascode晶体管的尺寸(并联个数)全部都减小了一半。

- 由于右边电路的输入和cascode晶体管的尺寸(并联个数)全部都减小了一半,因此其GM值也会减小一半,所以要把负载电阻增大一倍,这样能确保输出的正端和负端增益是一样的。也就是输出信号的信号幅度。

- 其电阻的类型采用低电阻率的类型,主要根据电阻值大小和温度特性去选择合适的类型电阻

- 左边的负载阻抗并联了4个电阻

- 通过这种方式进一步减小了整个核心电路的工作电流,然后整体噪声系数和输入匹配状况并不是由右边单端转差分的电路决定,还是由左边这一路晶体管决定的。所以才把右半边电路的工作电流减小,确保小工作电流状态,减小整体电路的功耗。

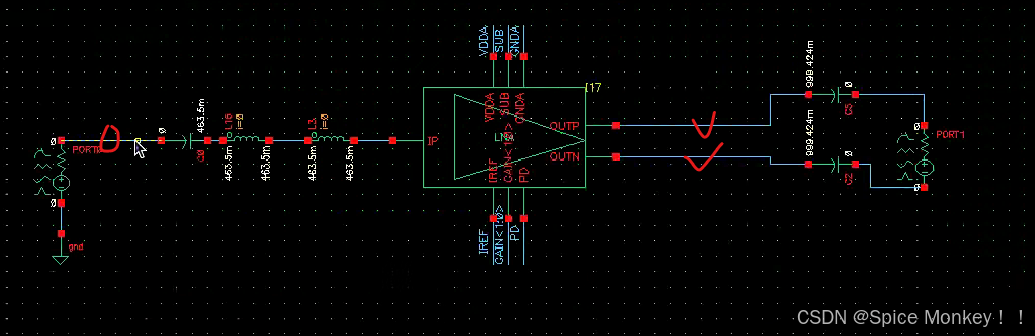

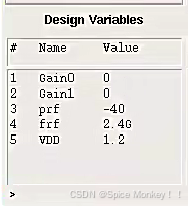

二、完整LNA仿真

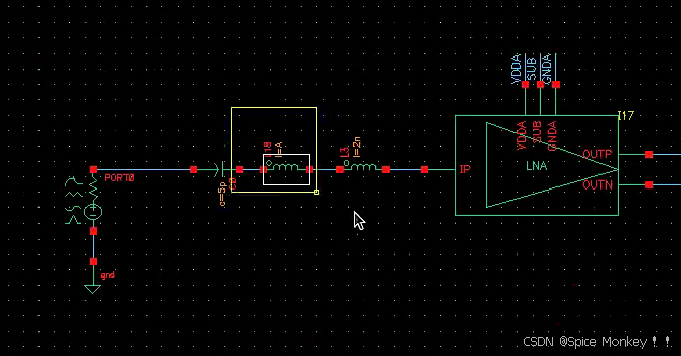

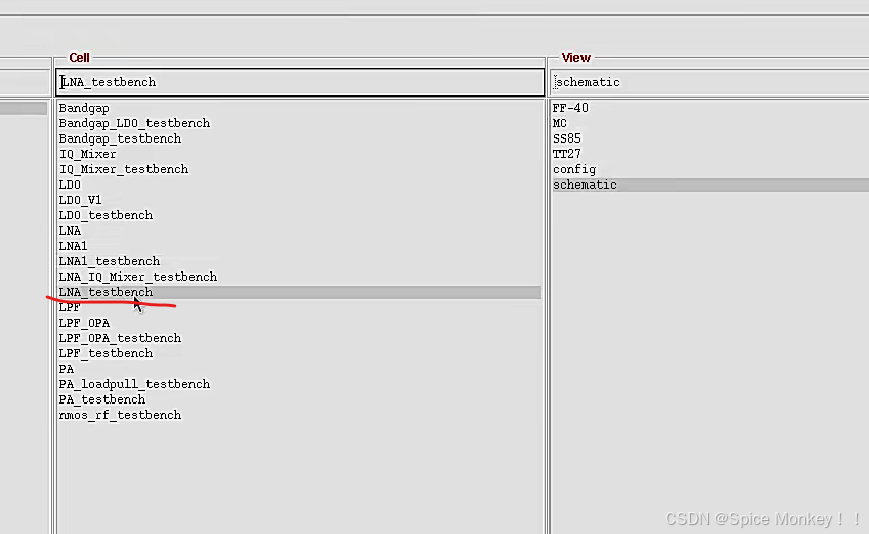

- 打开LNA完整电路testbench

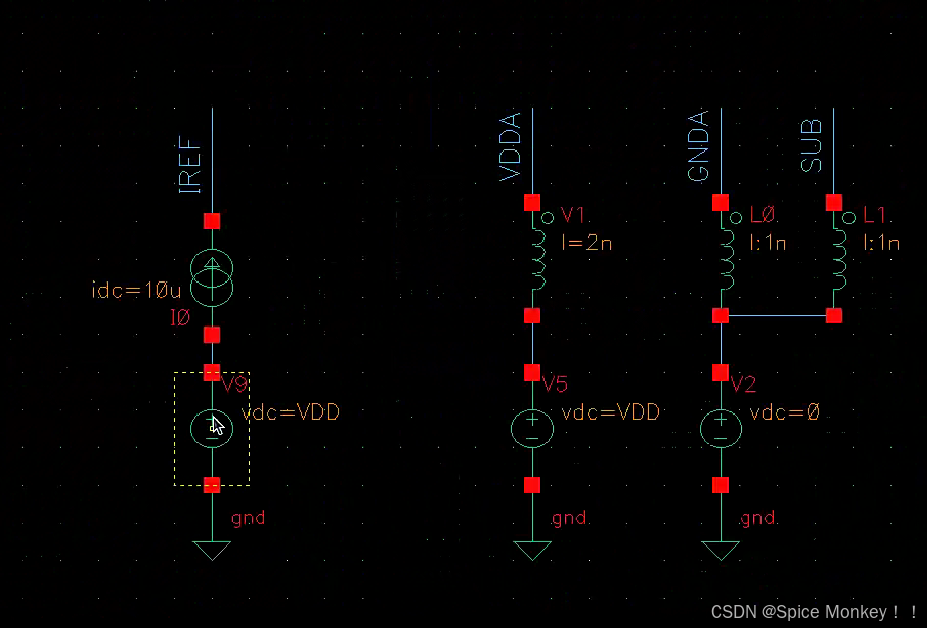

- 这个testbench和之前仿核心电路部分的testbench是一样的,只是电路增加了额外的输入偏置电流等控制信号

- 输入的偏置电流是理想的电流源10uA

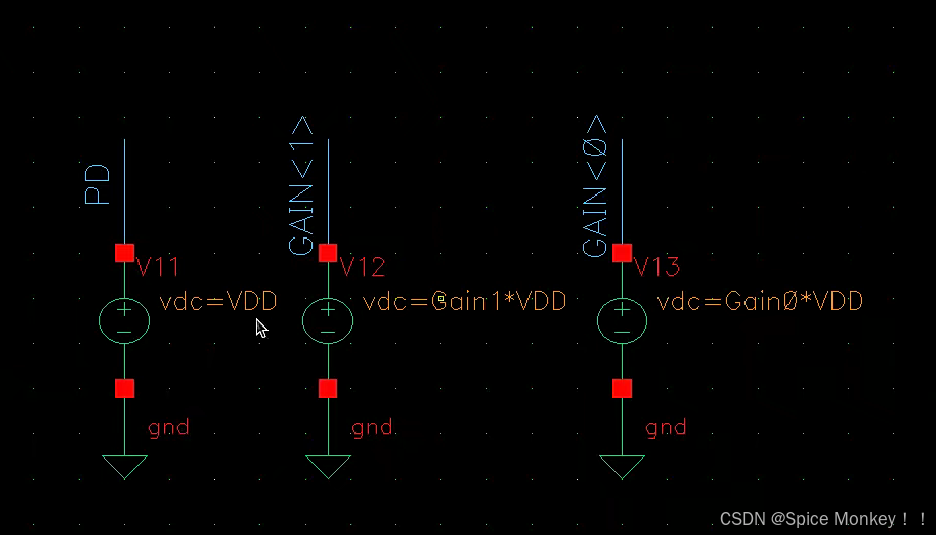

- 控制信号的配置

- PD信号接电源电压

- 增益控制信号设置了两个变量

- 其他参数跟之前仿真核心电路testbench

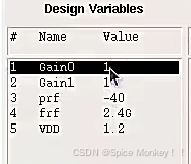

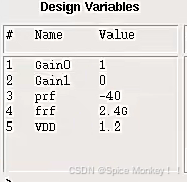

- 然后仿真,设计变量如下。

- 输入功率-40dBm,

- 增益控制信号都设置成1,表示该增益状态,因为其电压为Gain1*VDD,表示0V或者电源电压。

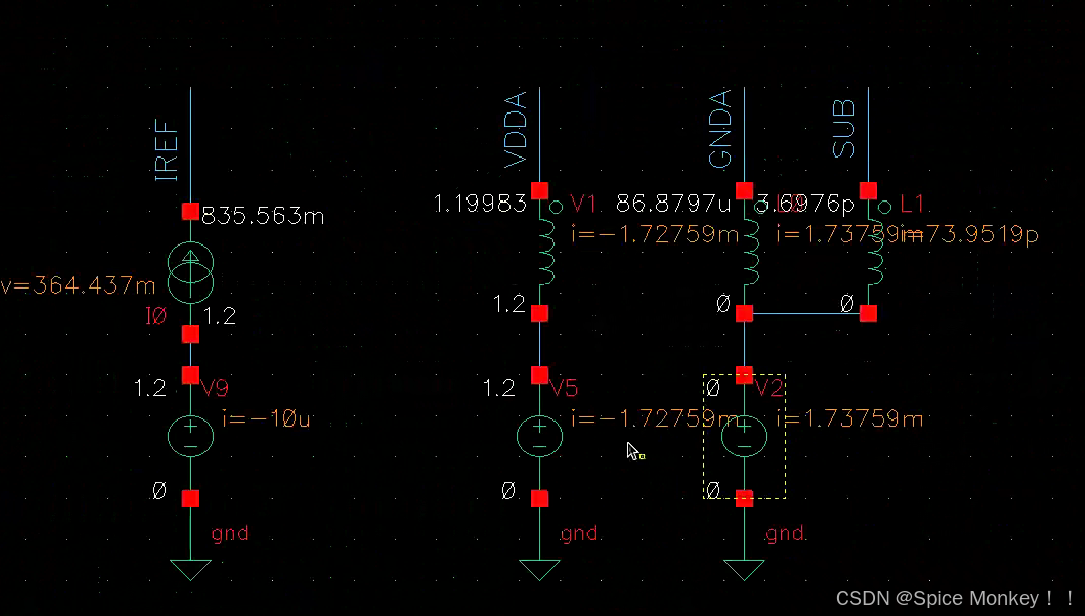

1. 直流工作状态

- 然后仿真,显示工作电流和工作电压

- 然后查看输入电流,电流镜的比例关系

温度特性

- 由于前面提到了,当采用固定栅极偏置电压的时候,直流工作电流的变化会非常大。

- 而现在采用恒定电流偏置方式。查看不同温度下工作电流的差异

- 先查看-40度下的直流仿真

- 能够看到在低温下,直流工作电流变化量较小,到1.12mA,维持在一个恒定的值。

- 然后查看高温情况下

- 高温情况下电流为1.06mA,工作电流变化较小。

- 因此采用恒电流的偏置电路是能够确保工作电流稳定的。确保性能参数不会在高低温下有太大的变化。

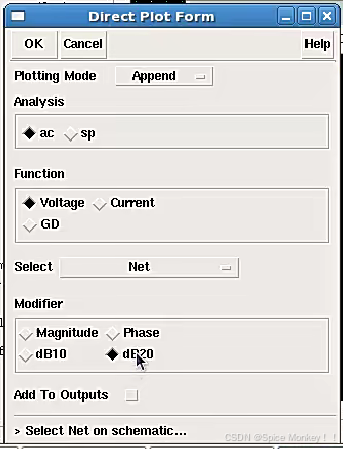

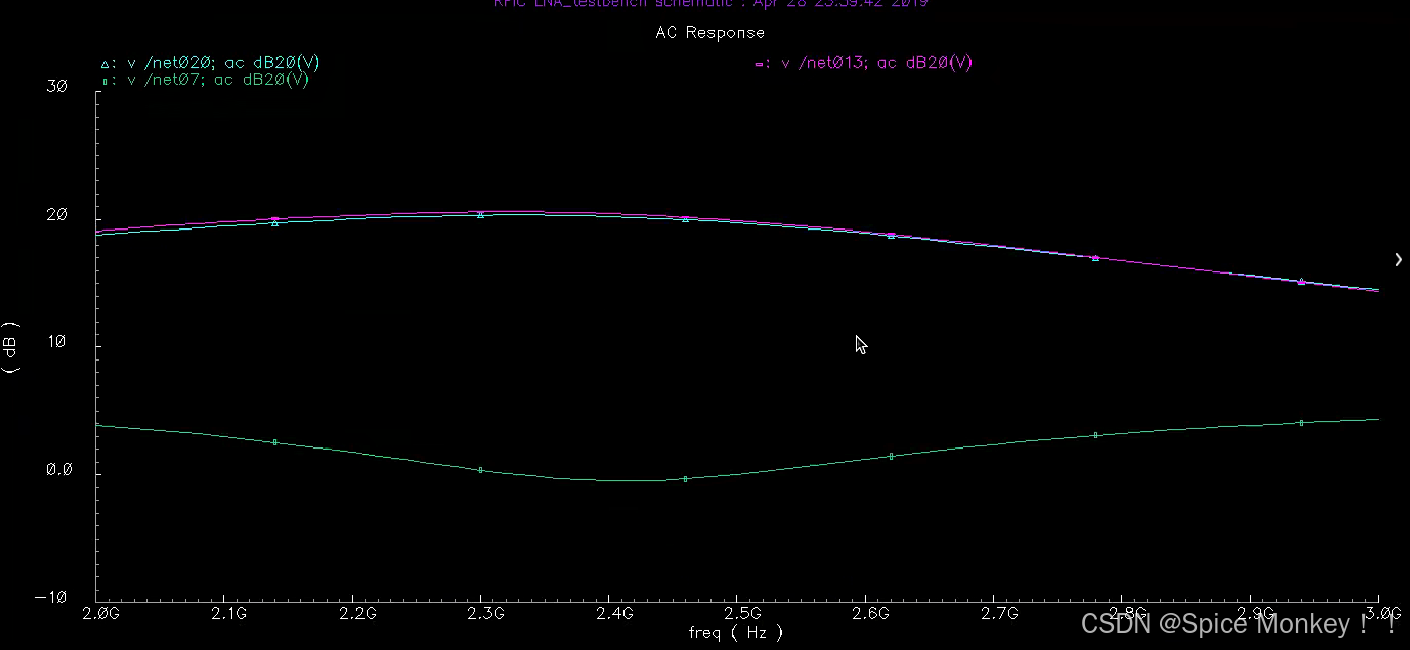

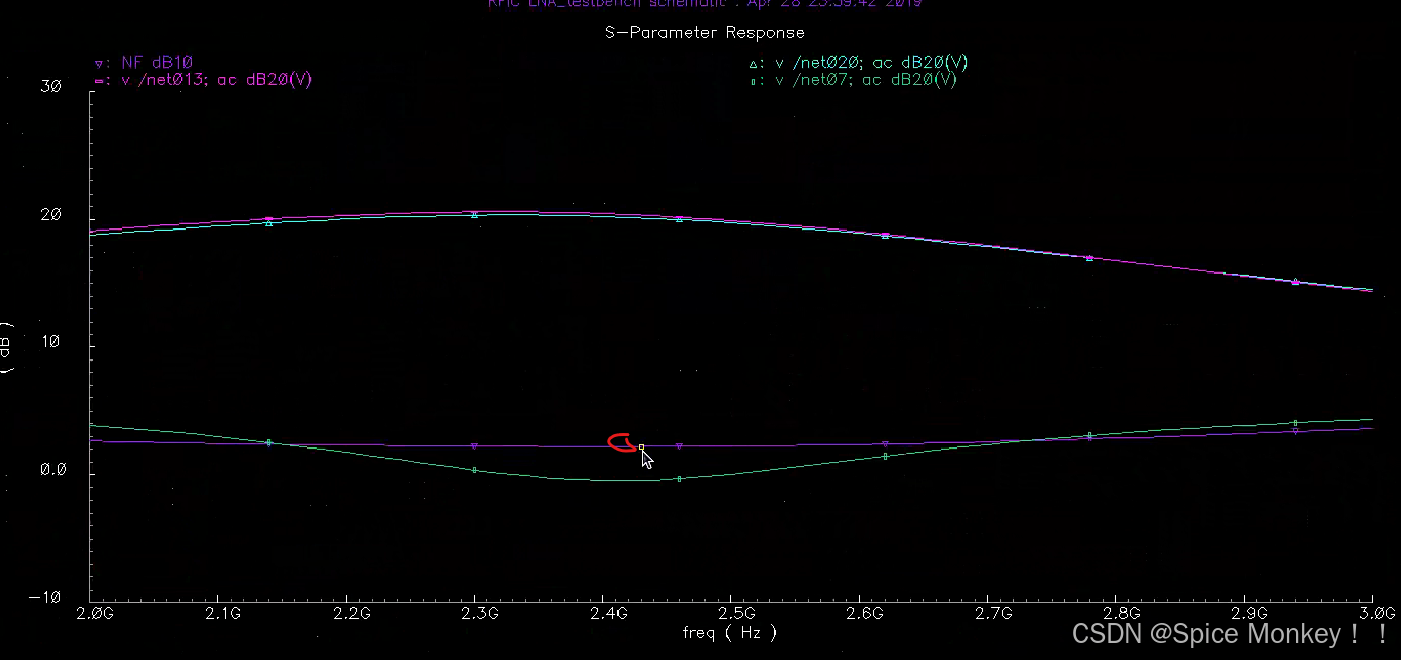

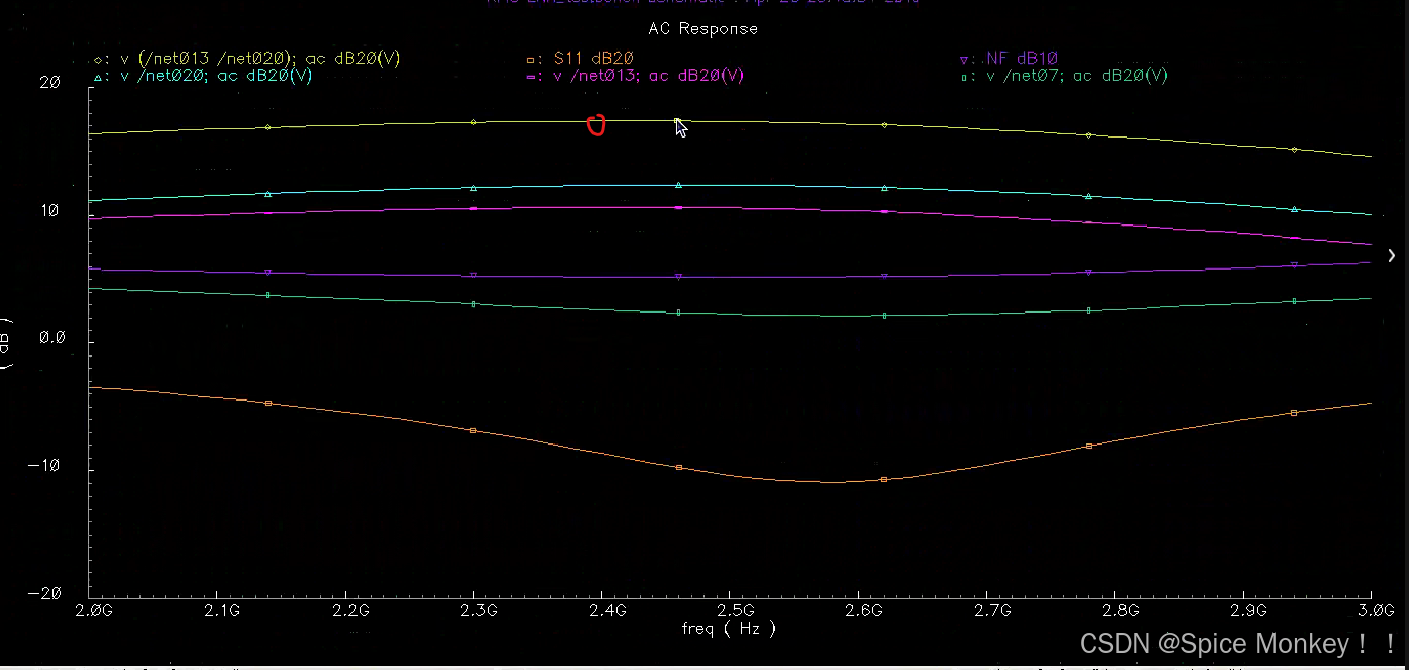

2.交流仿真

-

然后改回去查看常温下的性能参数,打开交流仿真,查看增益状况

-

增益要关系输入端,和输出的差分两个端口

-

输入端是-0.5dB左右

-

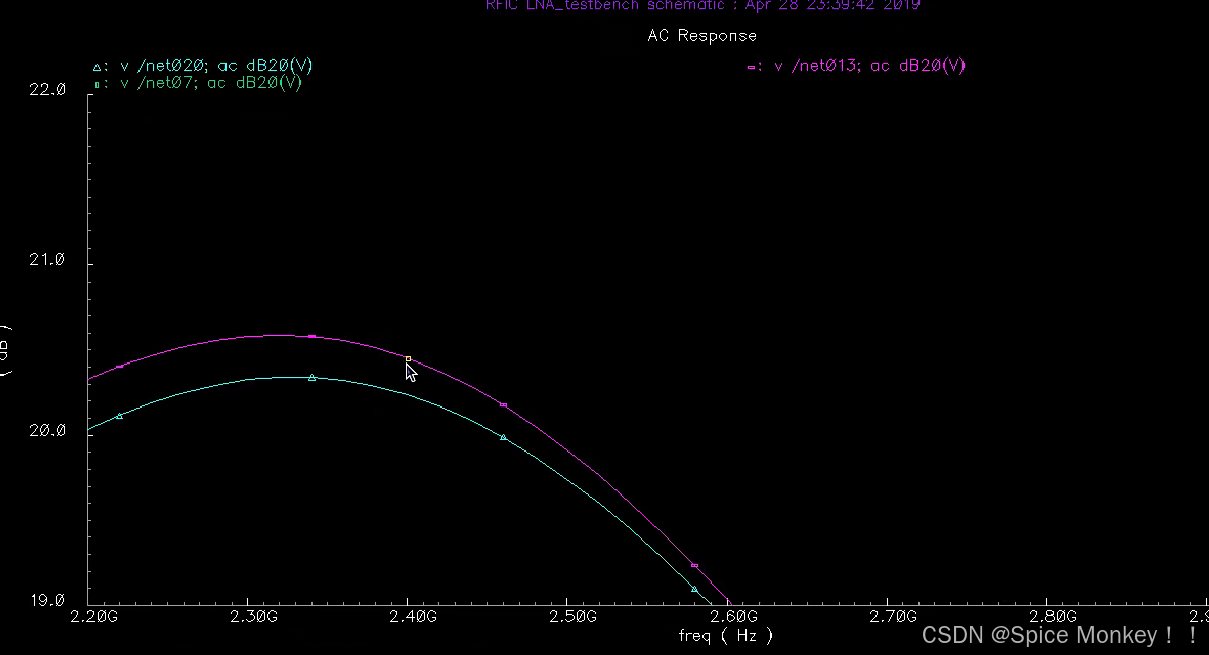

输出端要查看其平衡性,由于将核心电路设计为不对称的情况,因此需要查看他们的增益差值。

-

可以看到在2.4GHz下,只有0.2dB的差值。说明这个电路的平衡性要比之前电路的平衡性更好一些。因为将核心电路的右半部分电路晶体管尺寸减小,使其寄生电容减小增益得到了提高,使输出正负两端的平衡性有了进一步的改善。

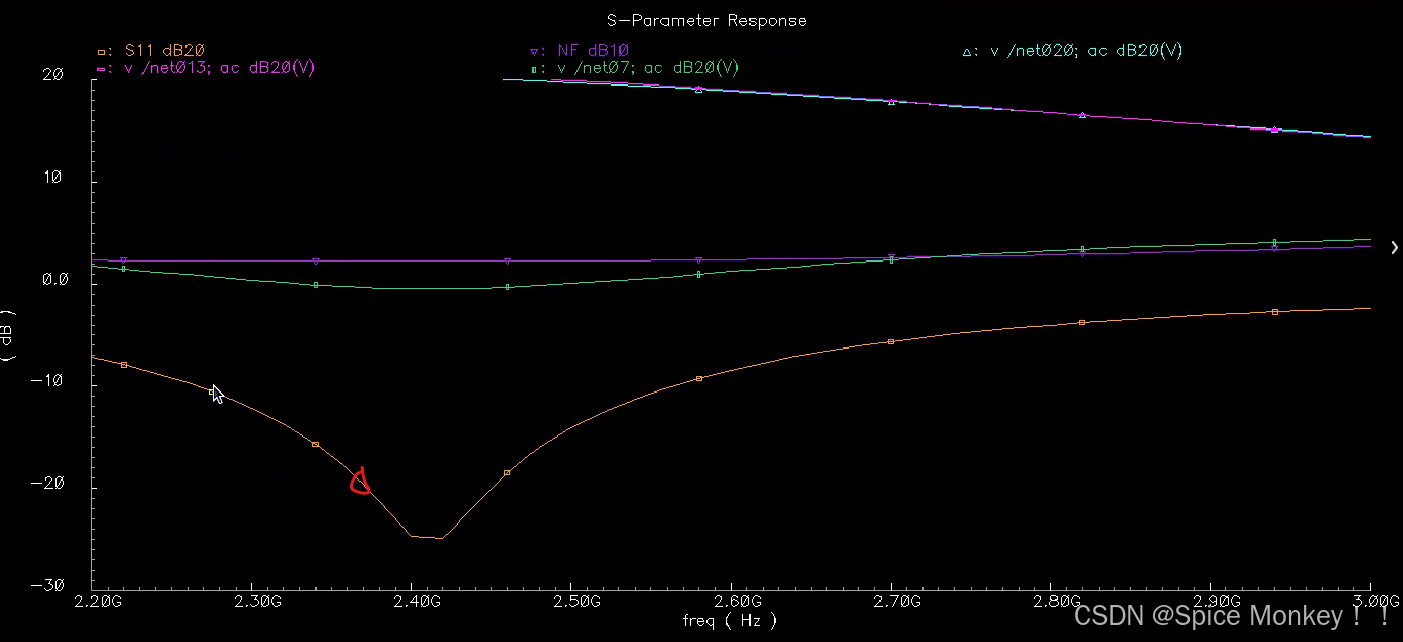

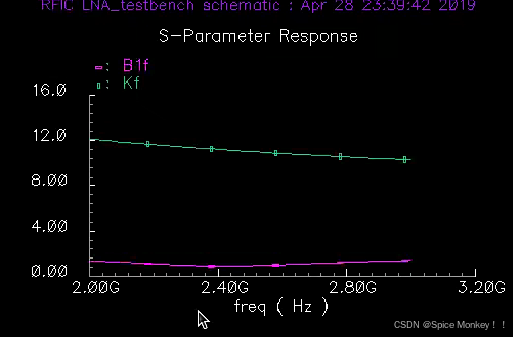

3. s参数

- 然后查看噪声系数NF,为2.23dB

- 然后查看输入匹配S11,输入匹配较好

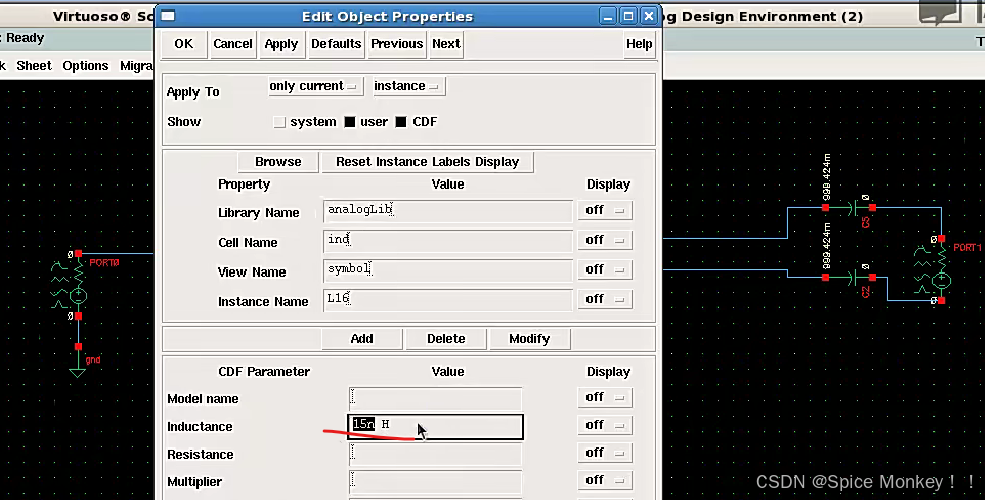

- 输入的电感也减小到了15nH的值。减小了10nH

- 输入电感的减小主要是因为其内部并联了匹配MOS电容,使得输入的串联电感会减小一些。

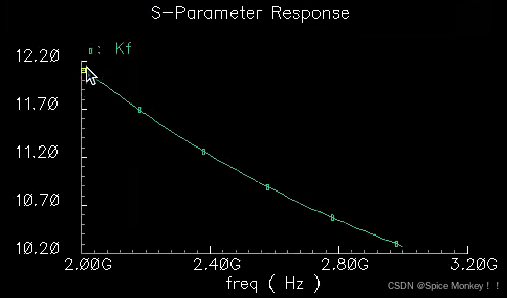

- kf值也是比1大的

- B1f也是小于1的

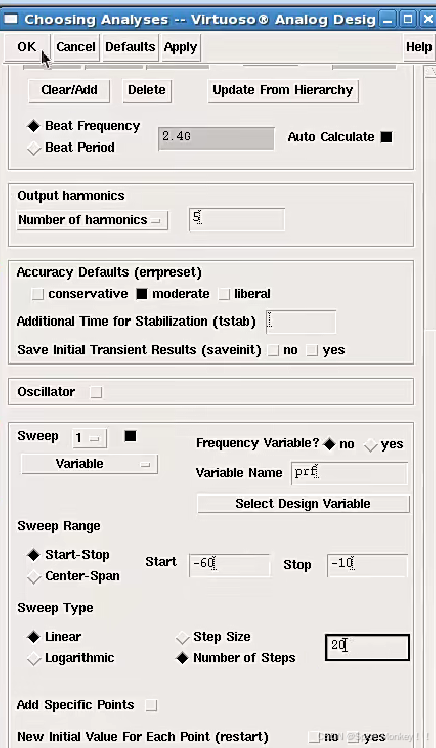

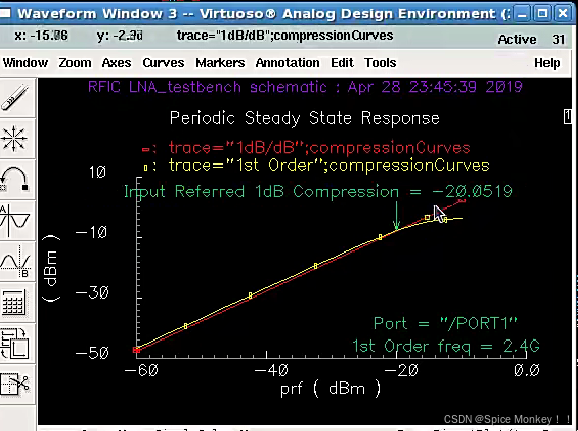

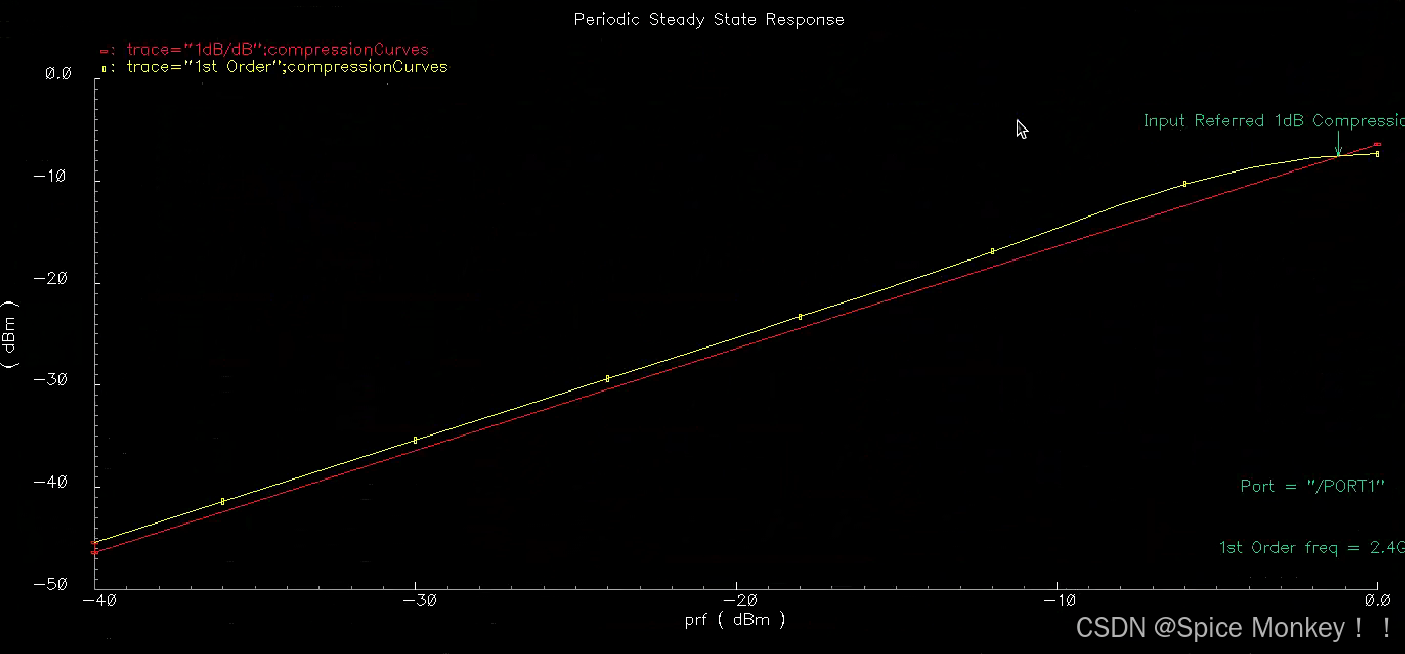

4.pss仿真

- 设置pss仿真

- 查看输入1dBm压缩点为-20dBm

- 那么输入三阶交调点为-10dBm左右,

5.高低温

6.工艺角

7.增益步进仿真

二挡增益

- 将Gain0信号改为0,使得整个增益降低10dB

- 仿真发现,输出的正端增益下降到12.4dB,负端下降到10.6dB,增益的差值变得更加大了

- 噪声系数恶化到5.2dB

- 输入匹配也有了一定程度的恶化,在-9到-10dB之间。

- 然后查看差分输出的增益,减到了17.4dB,

- 由于输入是2dB,所以总的电压增益是15dB

- 对于射频电路来说,精确度不会太高,基本差2dB左右不会有太大的影响。

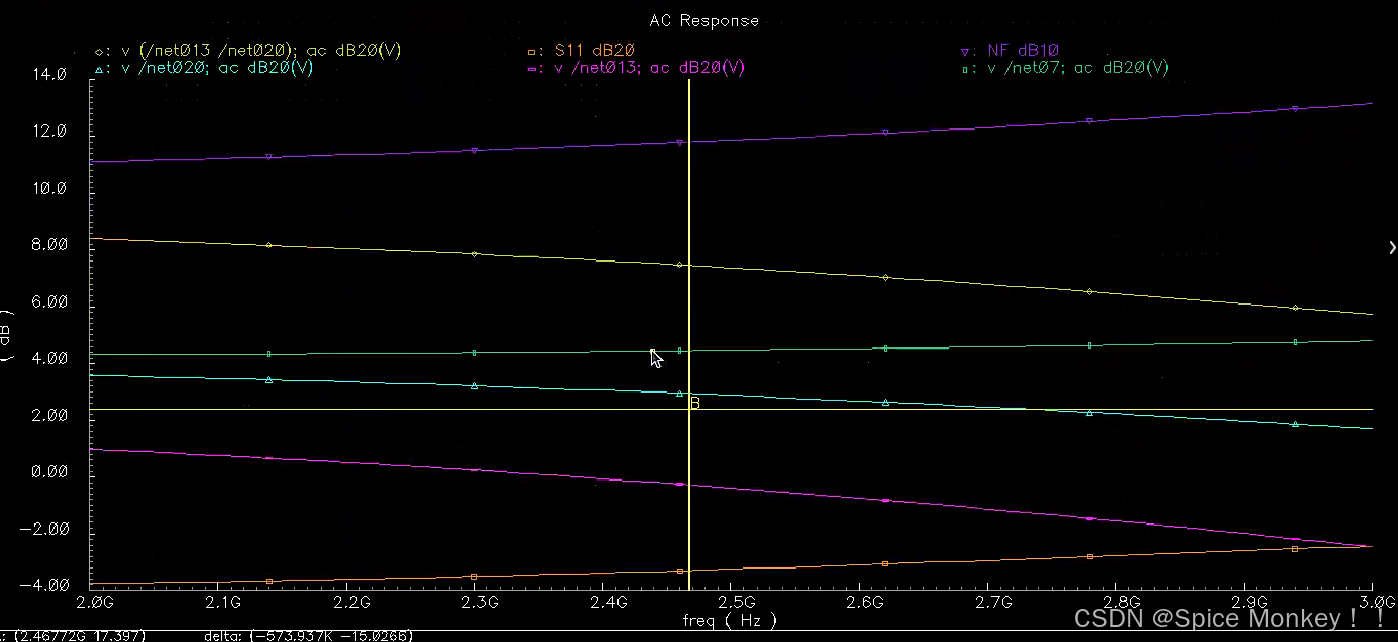

三挡增益

- 将两个增益控制信号都设置为0

- 增益基本只有3dB左右了

- 噪声系数恶化到11.8dB,在低增益的情况下,不太会去关注噪声系数的问题了。这种情况下一般认为输入信号功率是比较大的值,信噪比是非常高的。

- 输入匹配特性也变差了,主要是因为输入阻抗变得很高了,对50欧姆的匹配就会很差。因此当输入信号功率较强的时候,信号的反射会很大,这是在低增益下是可以允许它处在一个相对没有那么好的匹配状态的。

- 在最低增益下的线性度是在-1.2dBm,是远远大于-10dBm的要求的。

三、蒙特卡洛仿真

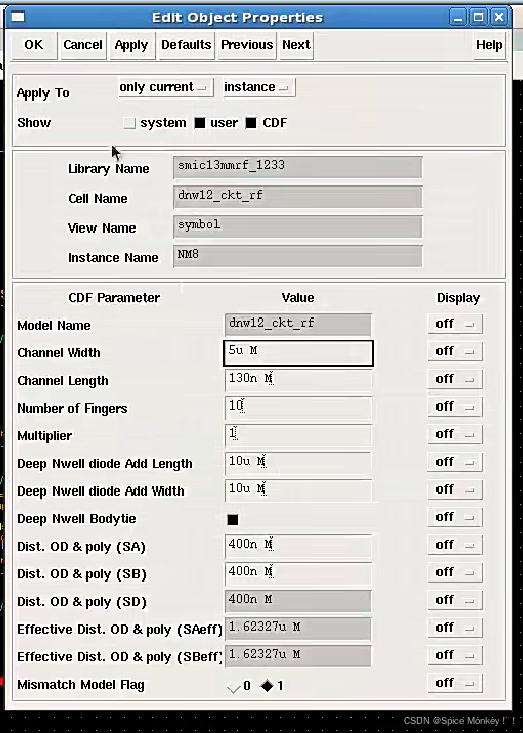

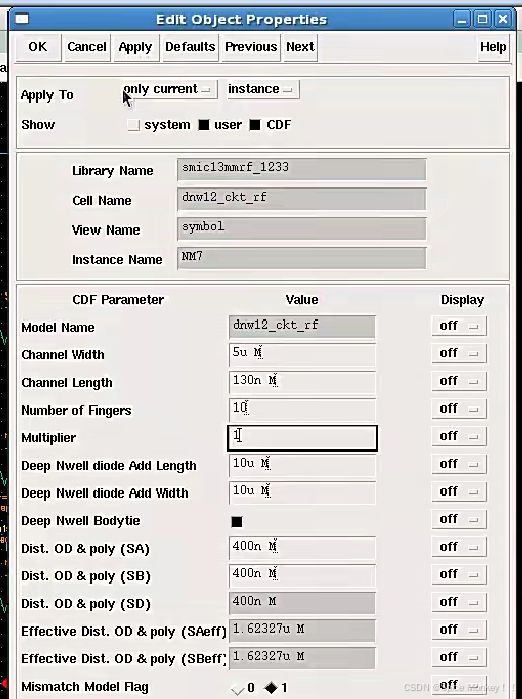

- 还有需要确定的是适配对电路的影响

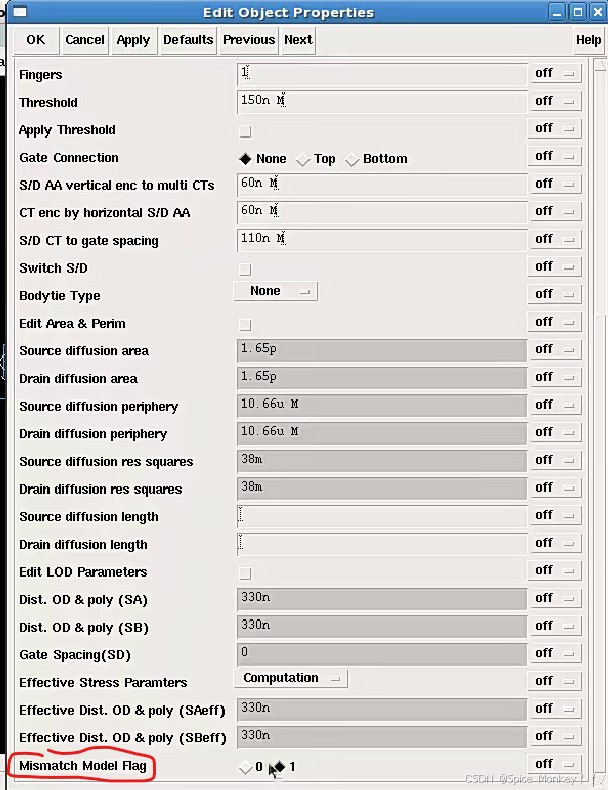

- 可以看到之前选用的晶体管类型都特意选择mismatch的晶体管

- 这种器件类型是可以选择mismatch的,默认都是1

- 那么我们需要去仿真mismatch和工艺偏差对整个电路性能参数的影响,就需要通过蒙特卡洛仿真。

- 首先要选用带有mismatch的器件类型(包括晶体管和电阻)

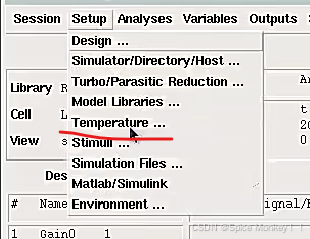

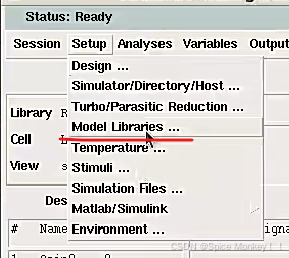

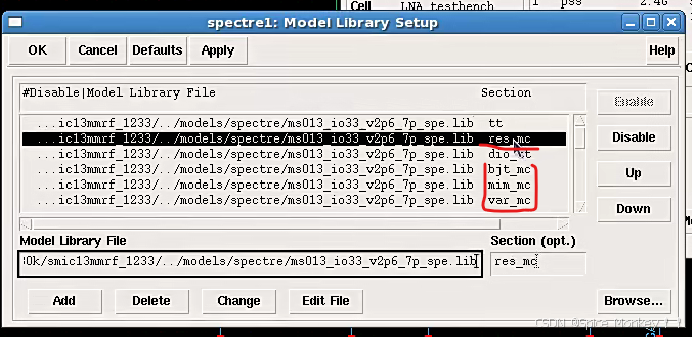

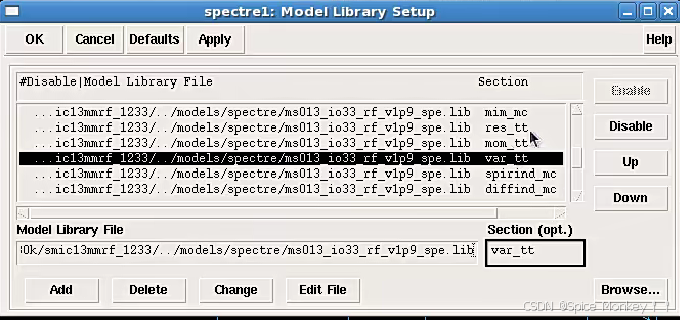

- 然后,要修改电路的模型

- 需要修改成MC模型,即蒙特卡洛模型

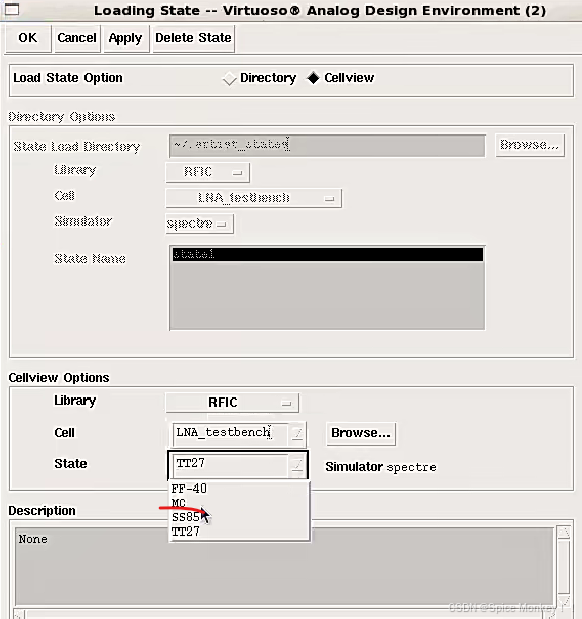

- 这里我们直接调用之前保存好的state,MC

- 可以看到所有器件参数都设置为了MC

- 如果没有设置成mc的话,仿真的时候会报错

- 这里要注意下面三个参数不能选择mc类型,因为在前面已经有相应的定义了

- 如果设置成mc类型,系统会报错

- 先仿真s参数

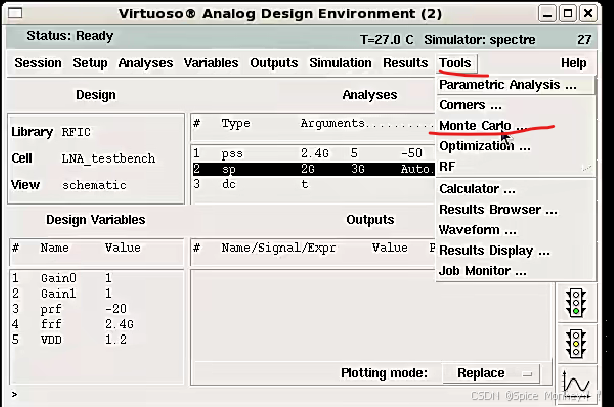

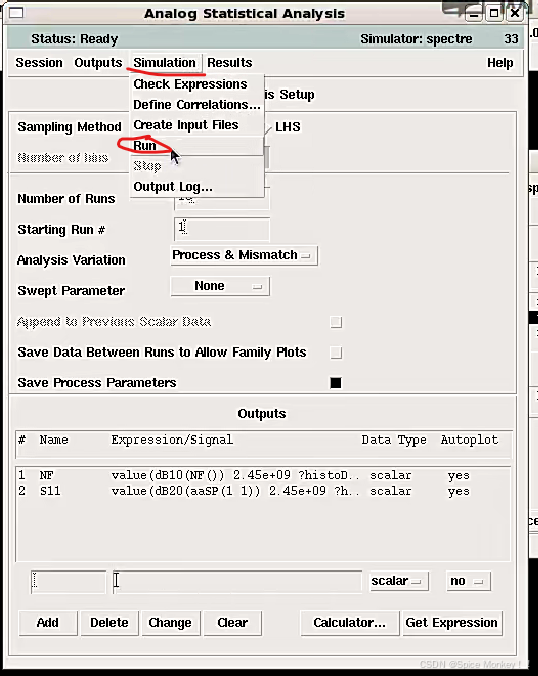

- 设置好后选择monte carto仿真

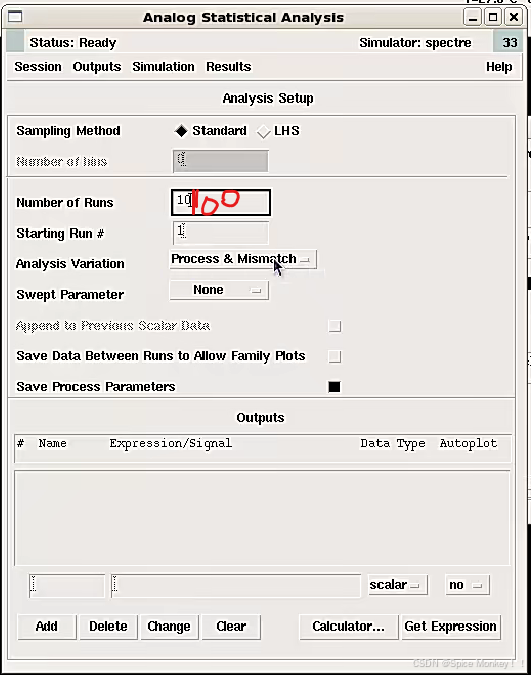

- 通常的sampling method要选择标准的standard

- 仿真次数通常设置为100次,然后取标准方差

- 仿真偏差analysis variation有三个选择,第一个是仿真工艺偏差process only,表示晶圆wafer的差异。还有一种是mismatch的偏差,也就是适配,即同一个晶圆上,不同的晶体管或不同电阻电容之间适配误差的影响,第三种是工艺偏差和mismatch同事仿真。

- 扫描变量暂时不进行扫描

- 蒙特卡洛仿真最终要的是确定仿真的目标,比如工艺偏差,输入匹配等

- 因此要进行公式的编辑,

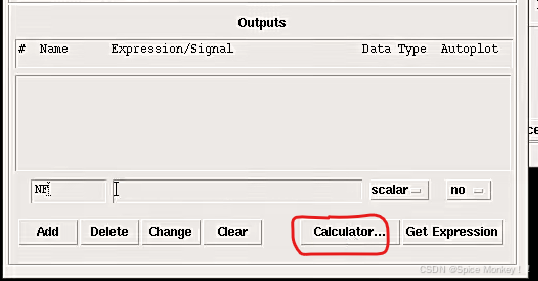

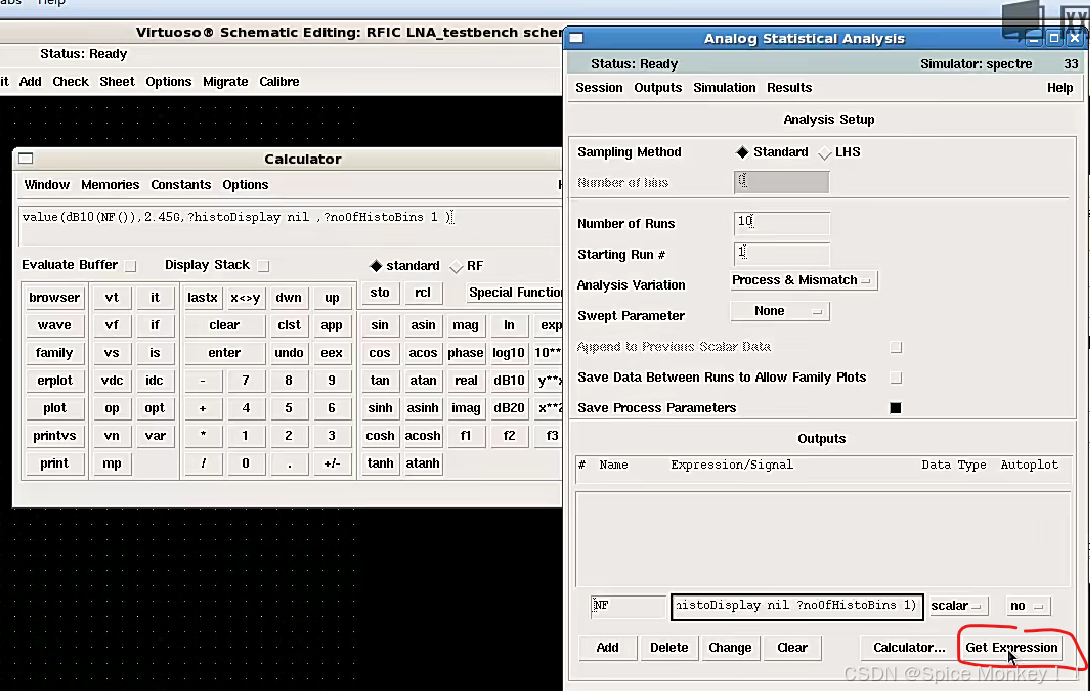

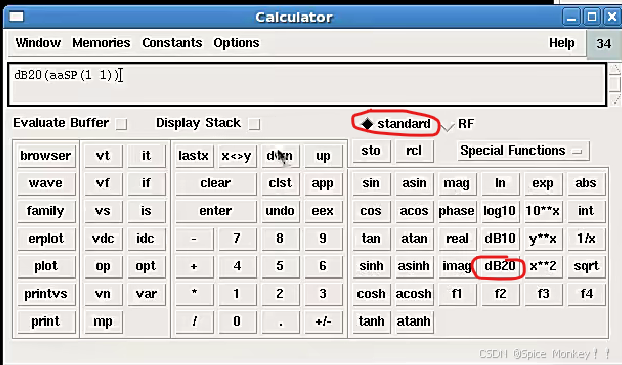

- 首先定义了一个噪声系数为NF,然后打开计算器,来获得NF的表达式

- 由于要查看真是的结果分布和标准方差的影响,通常表达式不会去选择波形wave的情况,而是选择scalar准确的参数数值的结果

- 这里我们需要选择特定频率点上的值

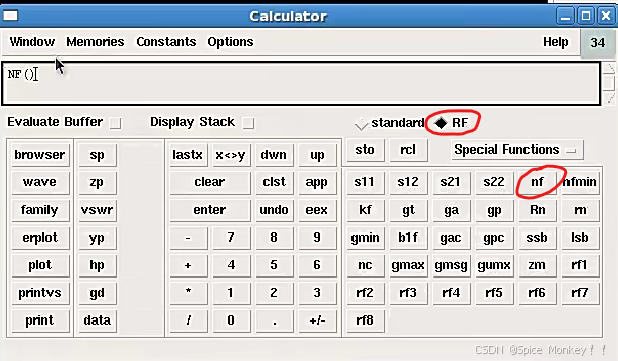

- 这里我们需要选择特定频率点上的值 - 先选中RF

- 然后点击NF

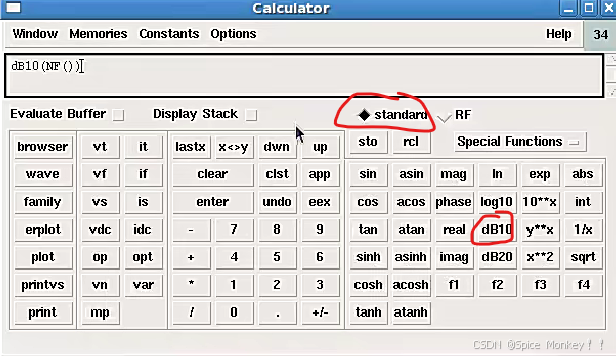

- 然后选择标准库standard,选择dB10,转化为dB数

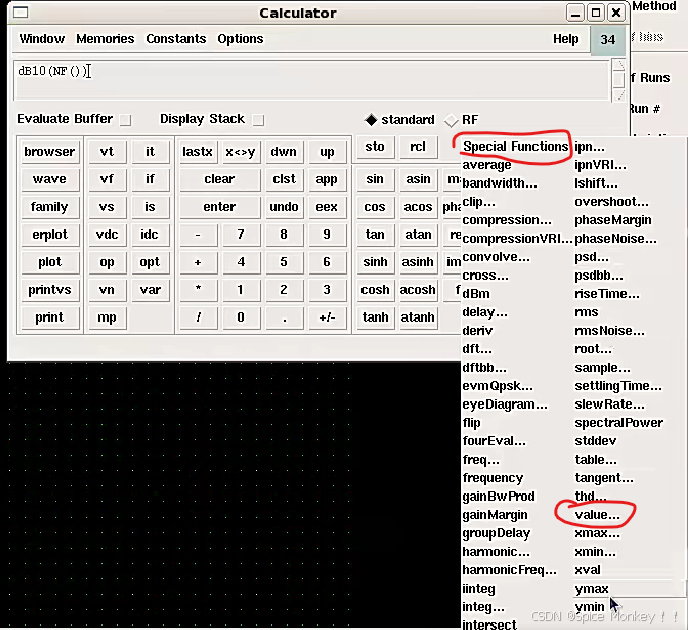

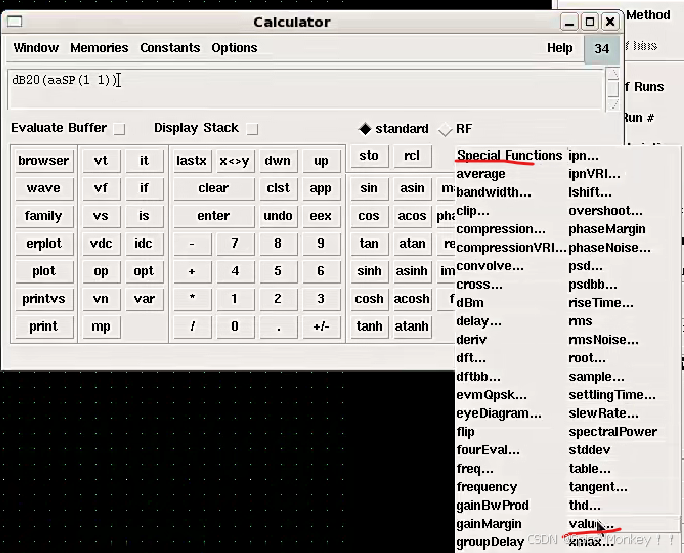

- 然后我们要截取某个频率点上的噪声系数进行分析。如果不选择某个频率点,那么在s参数仿真的时候,会从2GHz扫描到3GHz的频率范围,那么他输出的形式data type就是一条曲线,跟最终画出来的直方图结果不太一样。因此要取固定扫描变量的值

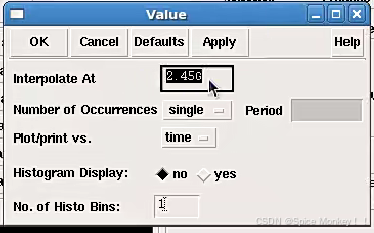

- 点击special function,选择value

- 然后会弹出的窗口来选择频率点,输入2.45GHz

- 然后将表达式get expression,把表达式拉进来

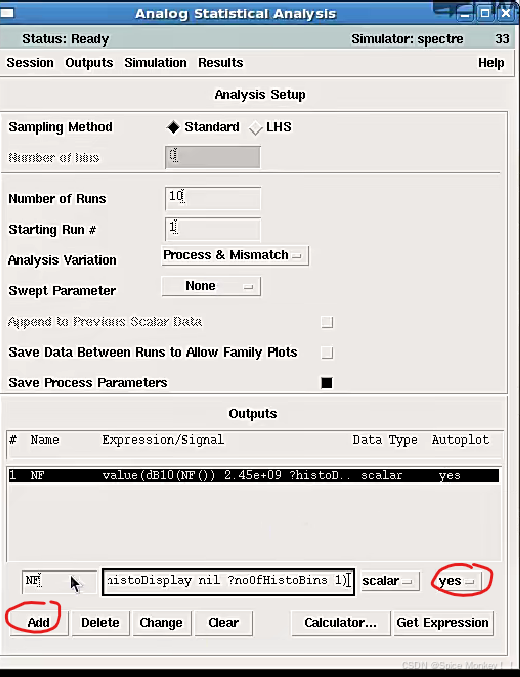

- 将autoplot选择yes,即自动画出结果

- 然后点击add

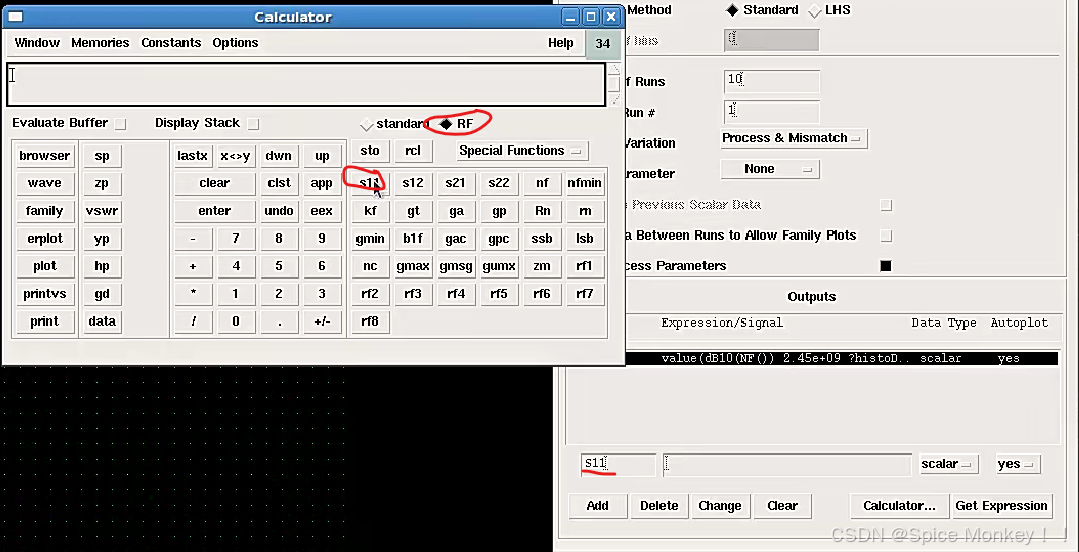

- 然后我们还需要去设置s参数

- 设置s11

- 然后选择standard标准库,选择dB20

- 然后同样选择频率点2.45GHz

- 这时候蒙特卡洛的设置就完成了

- 然后点击运行仿真

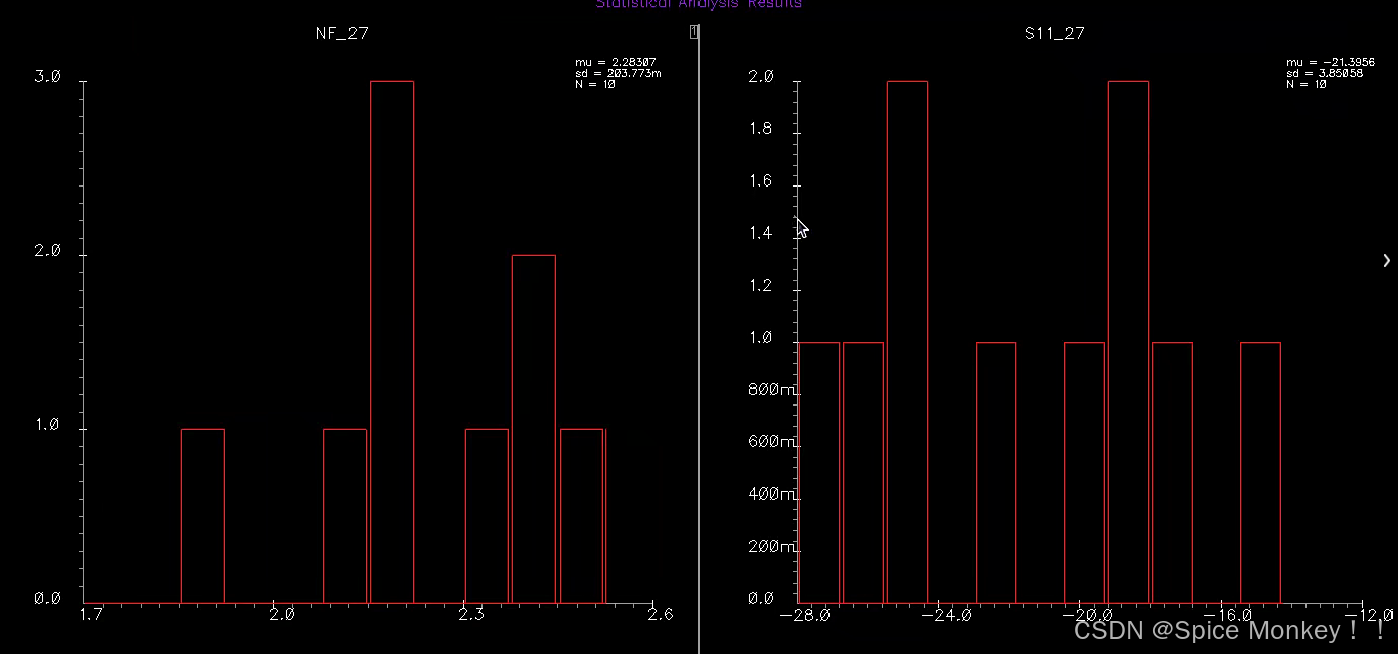

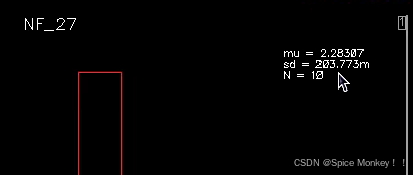

- 然后下面是跑了10次的NF和S11的结果

- 跑的次数越多,会越接近与真实的工艺偏差和mismatch偏差的结果

- 横坐标是NF的分布情况,纵坐标是表示次数。比如左图,在NF为2.15dB-2.25dB的时候,处于这个范围的总共有3次(10)。

- 左上角的mu表示平均值为2.28dB

- sd表示偏差为0.2dBm

- N表示总的仿真次数

984

984

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?