💥💥💞💞欢迎来到本博客❤️❤️💥💥

🏆博主优势:🌞🌞🌞博客内容尽量做到思维缜密,逻辑清晰,为了方便读者。

⛳️座右铭:行百里者,半于九十。

📋📋📋本文目录如下:🎁🎁🎁

目录

⛳️赠与读者

👨💻做科研,涉及到一个深在的思想系统,需要科研者逻辑缜密,踏实认真,但是不能只是努力,很多时候借力比努力更重要,然后还要有仰望星空的创新点和启发点。当哲学课上老师问你什么是科学,什么是电的时候,不要觉得这些问题搞笑。哲学是科学之母,哲学就是追究终极问题,寻找那些不言自明只有小孩子会问的但是你却回答不出来的问题。建议读者按目录次序逐一浏览,免得骤然跌入幽暗的迷宫找不到来时的路,它不足为你揭示全部问题的答案,但若能让人胸中升起一朵朵疑云,也未尝不会酿成晚霞斑斓的别一番景致,万一它居然给你带来了一场精神世界的苦雨,那就借机洗刷一下原来存放在那儿的“躺平”上的尘埃吧。

或许,雨过云收,神驰的天地更清朗.......🔎🔎🔎

💥1 概述

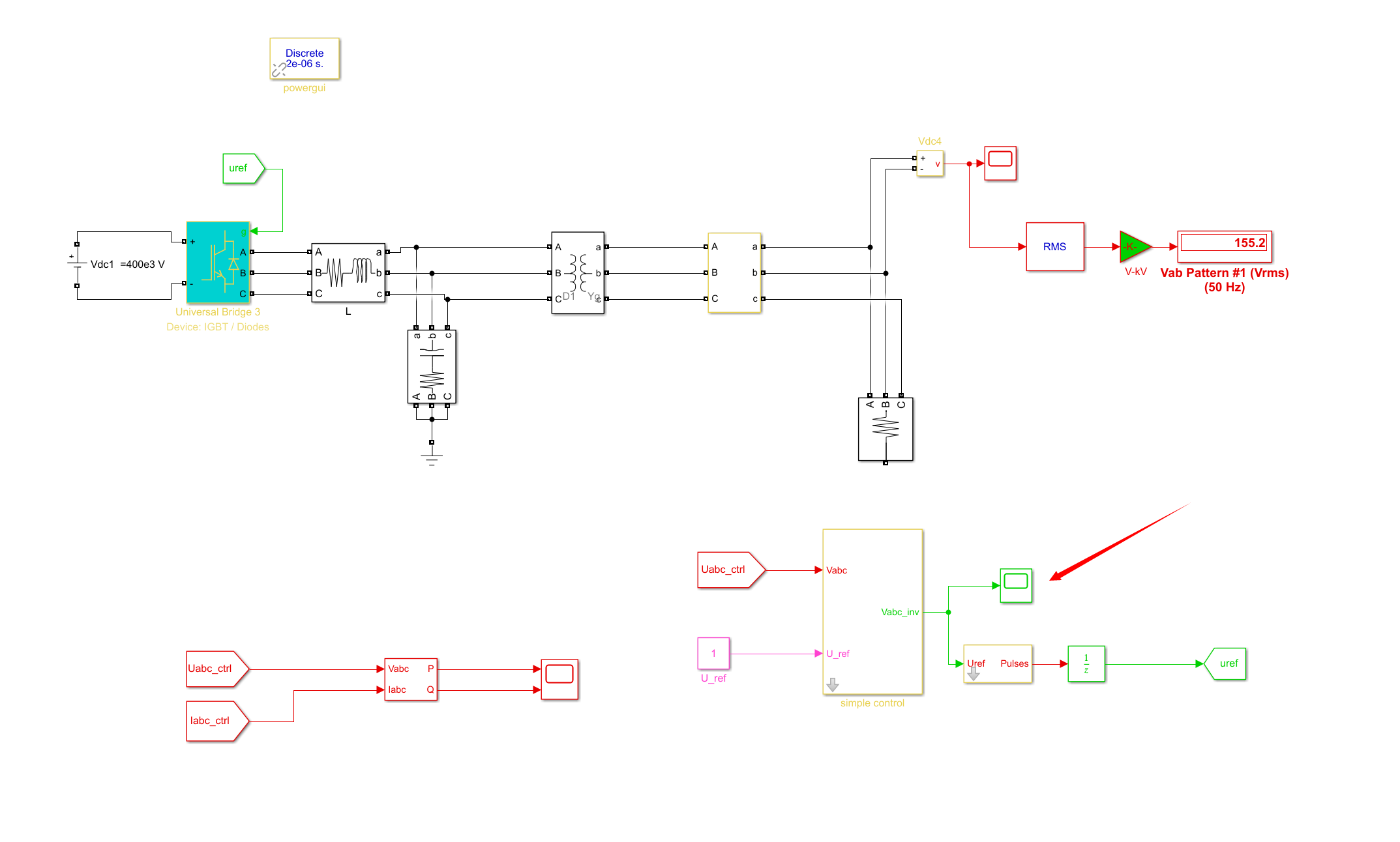

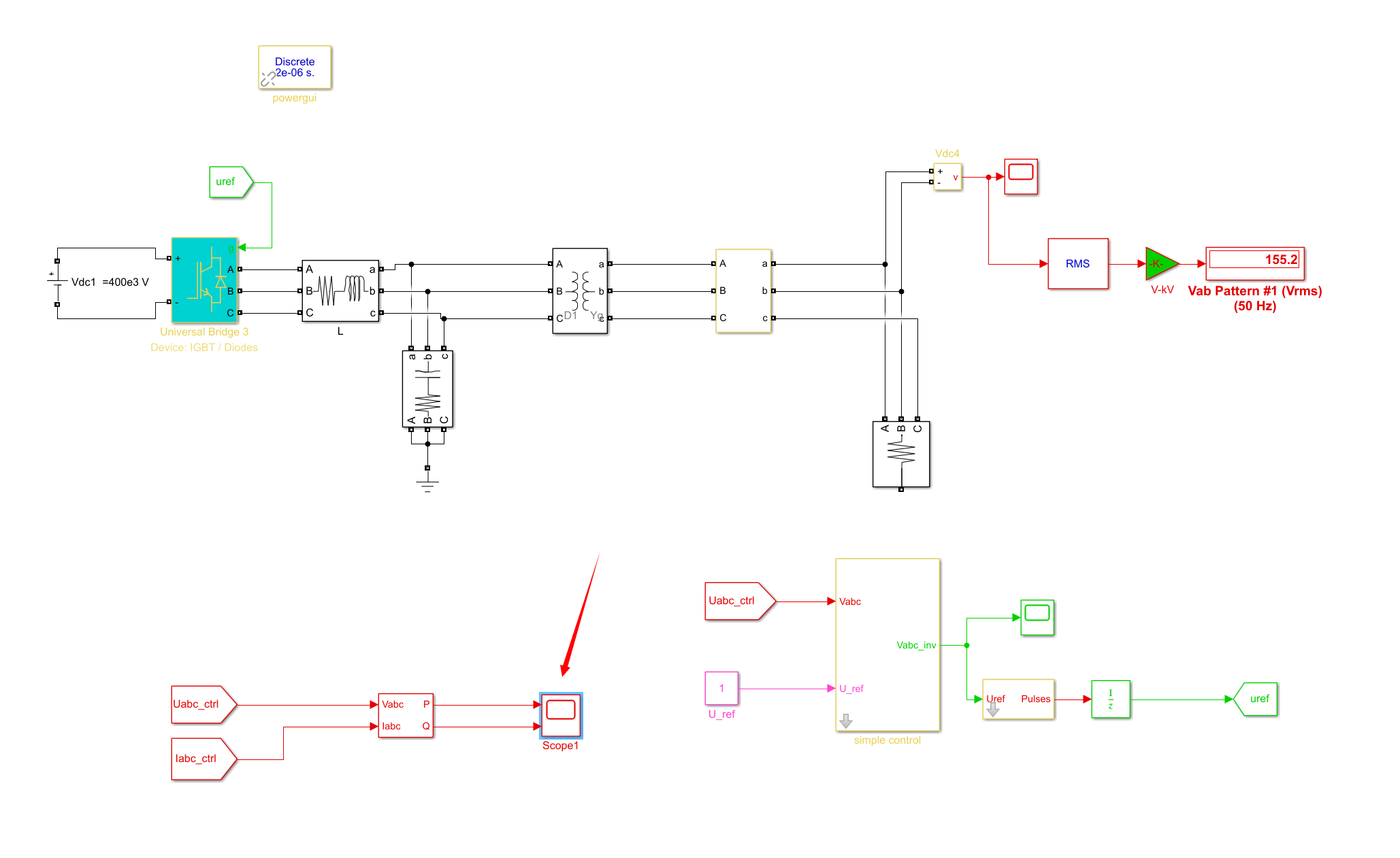

三相逆变器采用DPWM0调制(Dual PWM Modulation 0)是一种常见的控制策略,用于控制交流电源转换成交流电源的逆变器。DPWM0调制通常用于控制三相逆变器的输出电压和频率,以实现对电机或其他负载的精确控制。

DPWM0调制的基本原理是在每个PWM周期内,将一个PWM周期分成两个子周期,在每个子周期内通过对PWM信号的调节,实现对逆变器输出电压的控制。通过合理设计DPWM0调制的控制策略,可以实现逆变器输出电压的调节,从而控制输出功率。

在DPWM0调制中,需要考虑调制波形的形状、频率和相位等参数,以实现所需的输出电压波形。同时,还需要考虑逆变器的开关器件的功率损耗、电磁干扰等问题,以确保系统稳定运行。

DPWM0调制是一种有效的控制策略,被广泛应用于工业控制和电力电子领域,能够满足不同应用场景的要求,并提供良好的动态响应和稳定性。

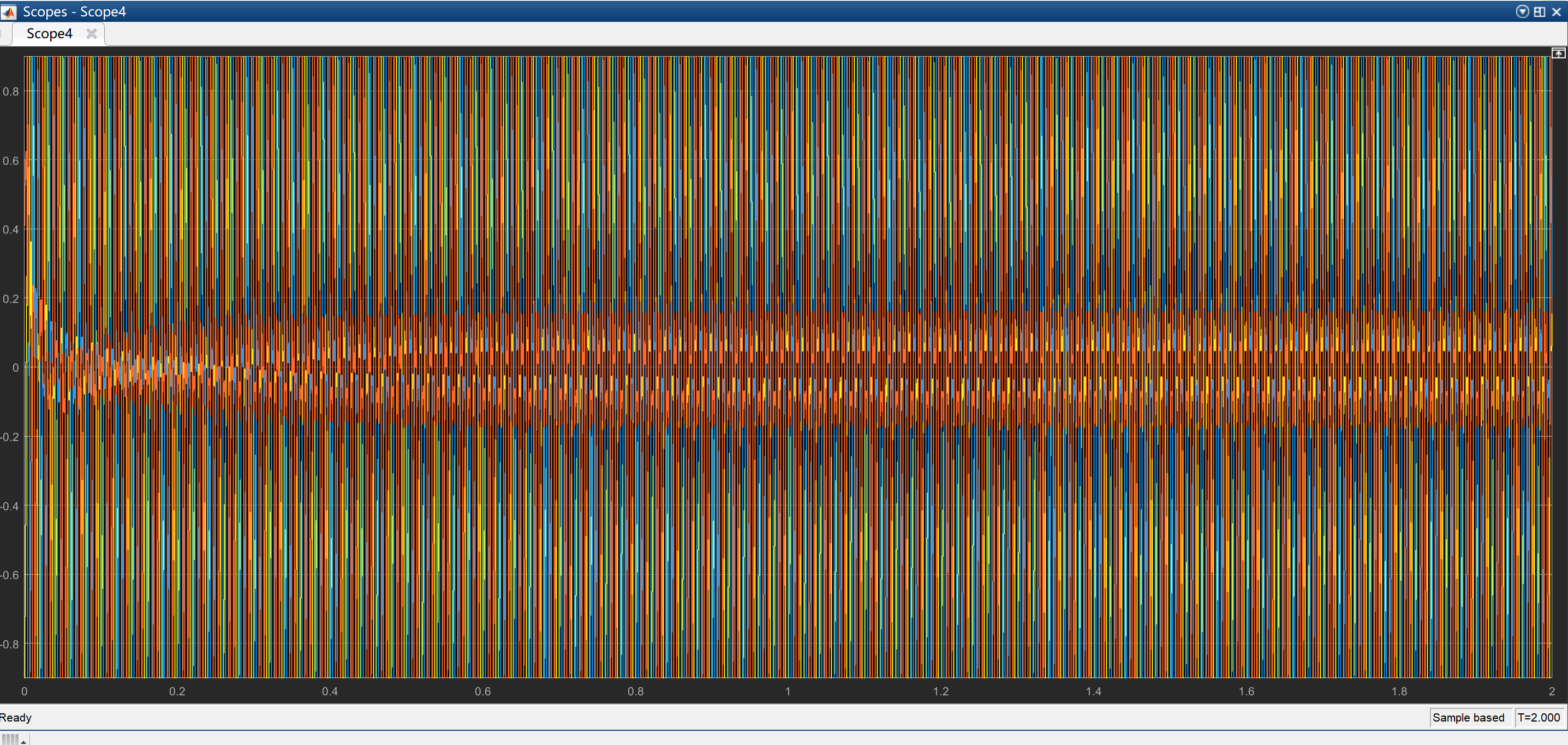

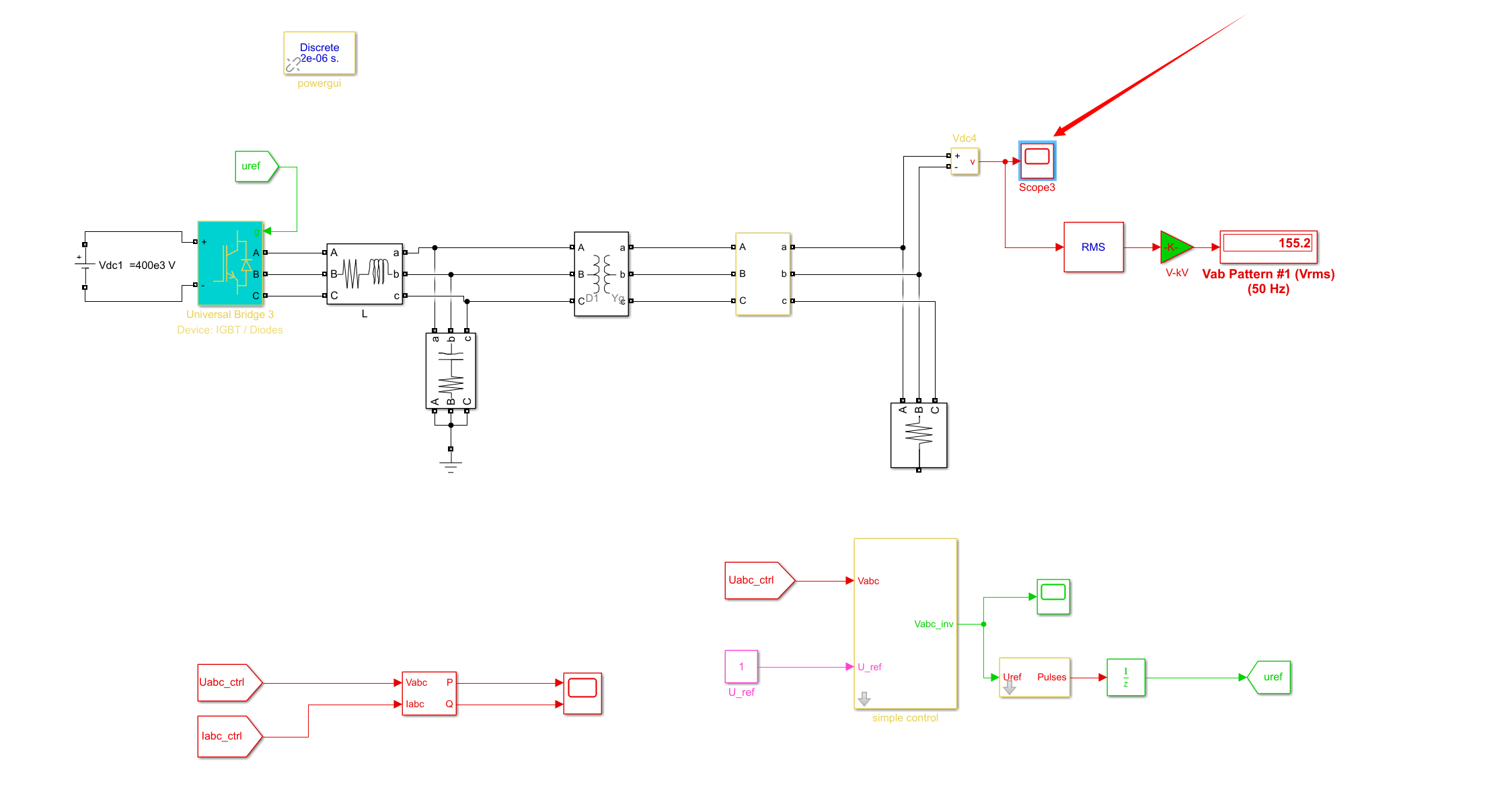

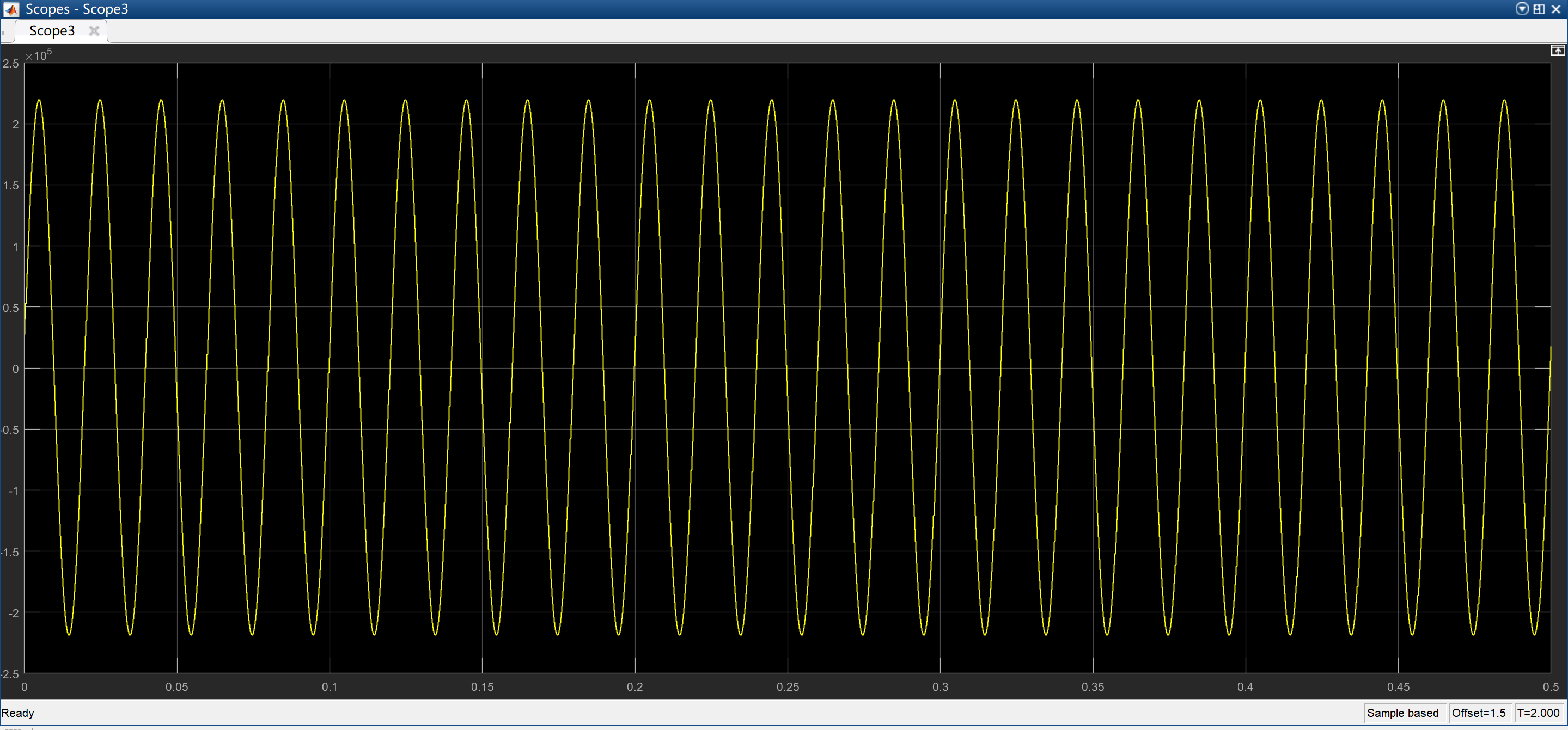

这个逆变器模型使用DPWM0调制技术。DPWM0是一种用于减少逆变器开关损耗的SVPWM技术的变体。模型中使用了基于PI的简单电压控制器。逆变器LC滤波器参数的调整不是最佳的,但整体模型性能良好。

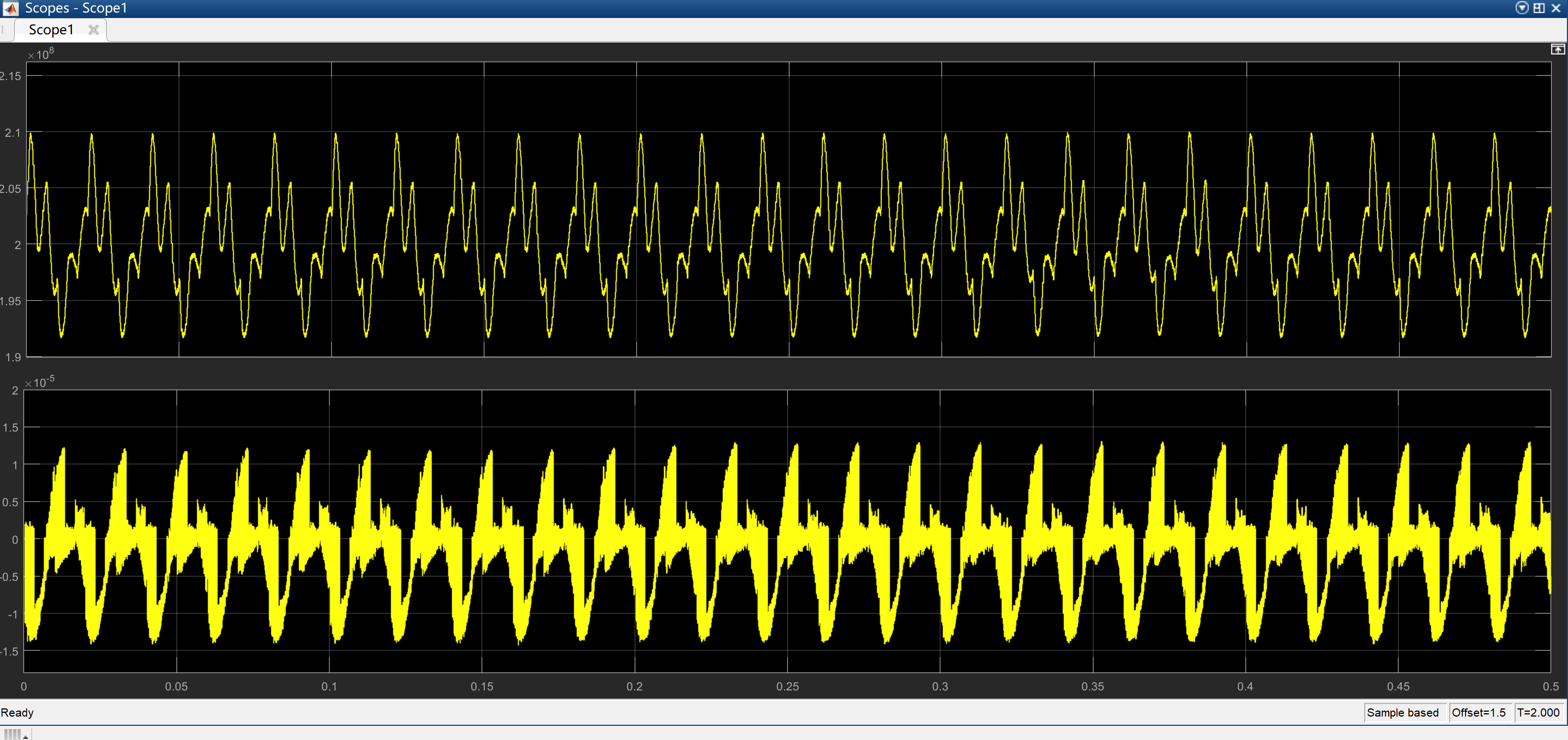

📚2 运行结果

🎉3 参考文献

文章中一些内容引自网络,会注明出处或引用为参考文献,难免有未尽之处,如有不妥,请随时联系删除。

[1]栗伟周,朱政通,梁满营,等.基于三相桥式逆变器的DPWM调制算法测试研究[J].机电信息, 2018(24):3.DOI:10.19514/j.cnki.cn32-1628/tm.2018.24.010.

[2]史威.三相逆变器SVPWM调制研究[D].华中科技大学,2011.DOI:10.7666/d.d187555.

[3]安昱明,李廷枫,李强,et al.正弦波脉宽调制技术在三相逆变器中的研究[J].电子技术(上海), 2017, 46(5):4.DOI:10.3969/j.issn.1000-0755.2017.05.001.

3370

3370

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?