运放

1、 分类:运算放大器、运算跨导放大器OTA----------运放通常用于ADC/DAC、DC/DC电源以及滤波电路中

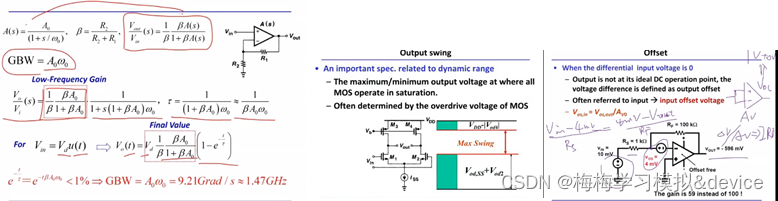

2、 运放的指标:增益、信噪比、速度(带宽)、输入输出摆幅、off-set失调、电源抑制比;小信号带宽就决定了阶跃响应的速度,运放处理信号的带宽;

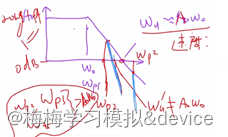

3、 运放的速度由GBW决定;GBW=A0*W;最常见的反馈系统,求出闭

环增益的频响表达式,带入到闭环增益里面,可以看到前面的低频增益

相当于直流增益,后面的表示以什么样的速度趋近于直流增益;

弧度/6.28=Hz;但要注意终值也是有误差的

明确:加入VVF之后,带宽也是1+环路增益倍

4、 输出摆幅;

4、 输出摆幅;

5、 Off-set失调:由于两个输入存在offset,会使得增益降低;所以要降低mismatch

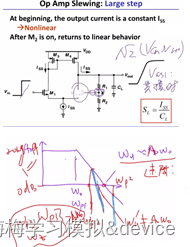

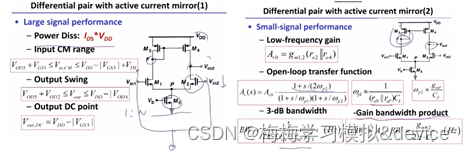

6、 线性:对于一个信号,一般是指数接近终值,但是非理想状态下先线性再指数;这是因为slew rate原因,全差动的slew rate是尾电流一半除以CL;单端是是尾电流除以CL ;先线性给CL充电,X的电压高到一定值,即根号2*(VGS-VTH),vgs是共模时的;使M2导通,那么继续指数趋近;差动对的输入差模范围;差动信号对差动电流有效分配,最大值不能超过根号2*(VGS-VTH)

7、 大信号:

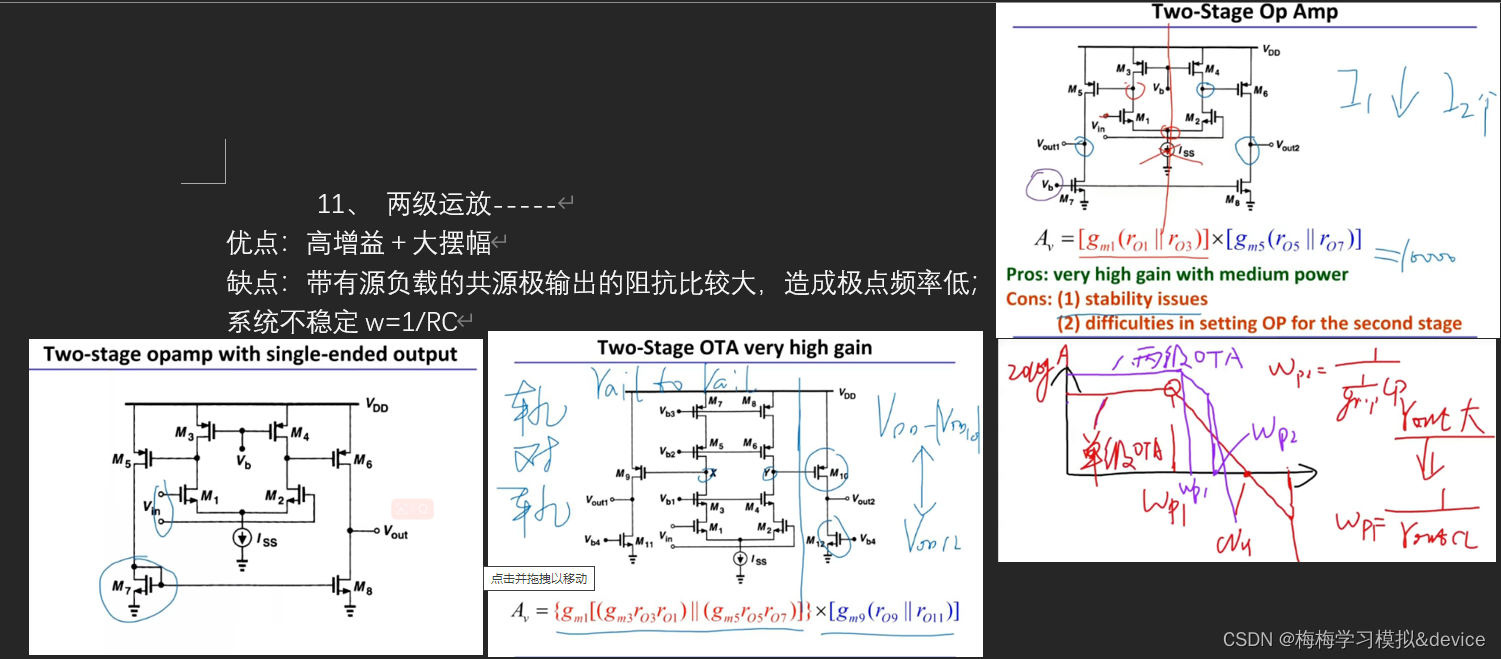

8、 小信号:这里要求wp2>wu(单位增益对应的频率);注意这里的GBW

通过gm/id方法设计电路首先要通过这个公式确定跨导

单极点系统有速度快、稳定;两级点系统,WP2>>WP1,多极点系统的单位增益带宽对于速度的控制打折扣,但是若WP2在Wu的右边,则还是可以决定速度;所以对于多级点系统,尽量使极点频率大于wu且wu尽可能大,GBW大,速度快

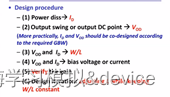

9、 设计一个运放的流程

需求:设计5ns±1%的运放,负载电容CL,增益,输出摆幅

流程:a)先根据GBW=gm/2*pi*CL-------得到gm

b) 根据输出摆幅确定VOD,如果不要求摆幅,VOD根据经验设计;

c)根据gm和VOD,gm=2ID/VOD,求出输入管的ID

d)根据ID确定W/L的值

e)根据所需的增益,AV=gm*r0,r0=1/λ*ID,保持gm不变,同比例增

大W和L,达到增益要求

例题:根据功耗确定电流,通过上面电流镜和下面尾电流共同确定两个支路

电流;Mb2:M7:M8=1:10:10;

设计时VOD9要比较大,因为电流大,不然尺寸就特别大,同时尾电流为了提高电阻,一般需要的L比较大,那么W一般也比较大,所以面积大,寄生电容大,所以VOD9要大;

为什么PMOS的VOD大?为了使12345678的尺寸不至于太离谱;

先设定L最小值减小size,减小寄生电容,小信号带宽更宽,极点频率越高;

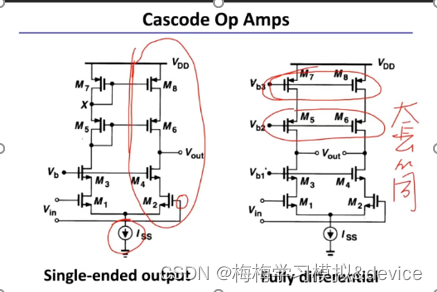

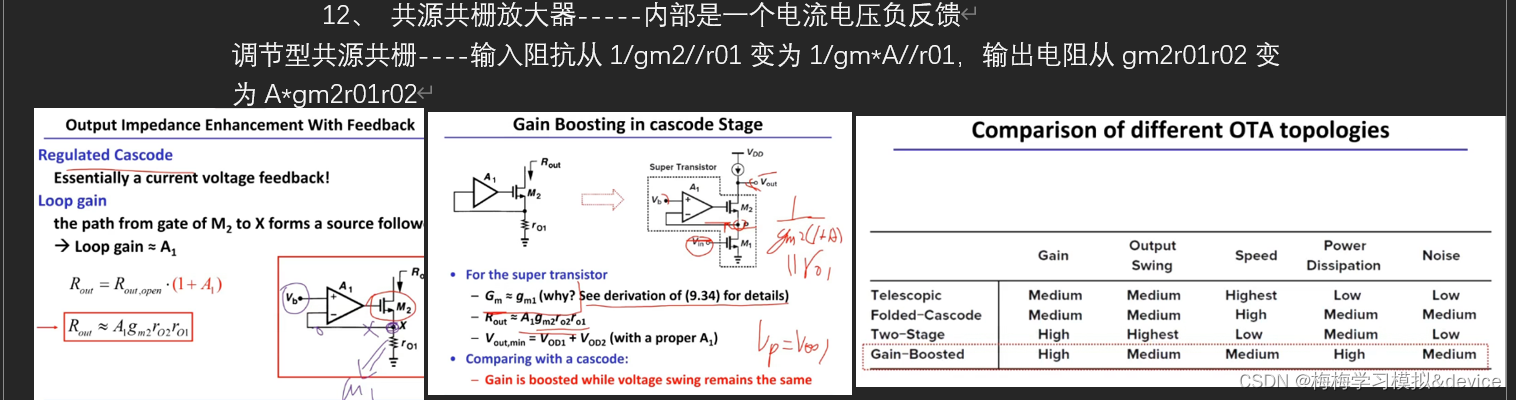

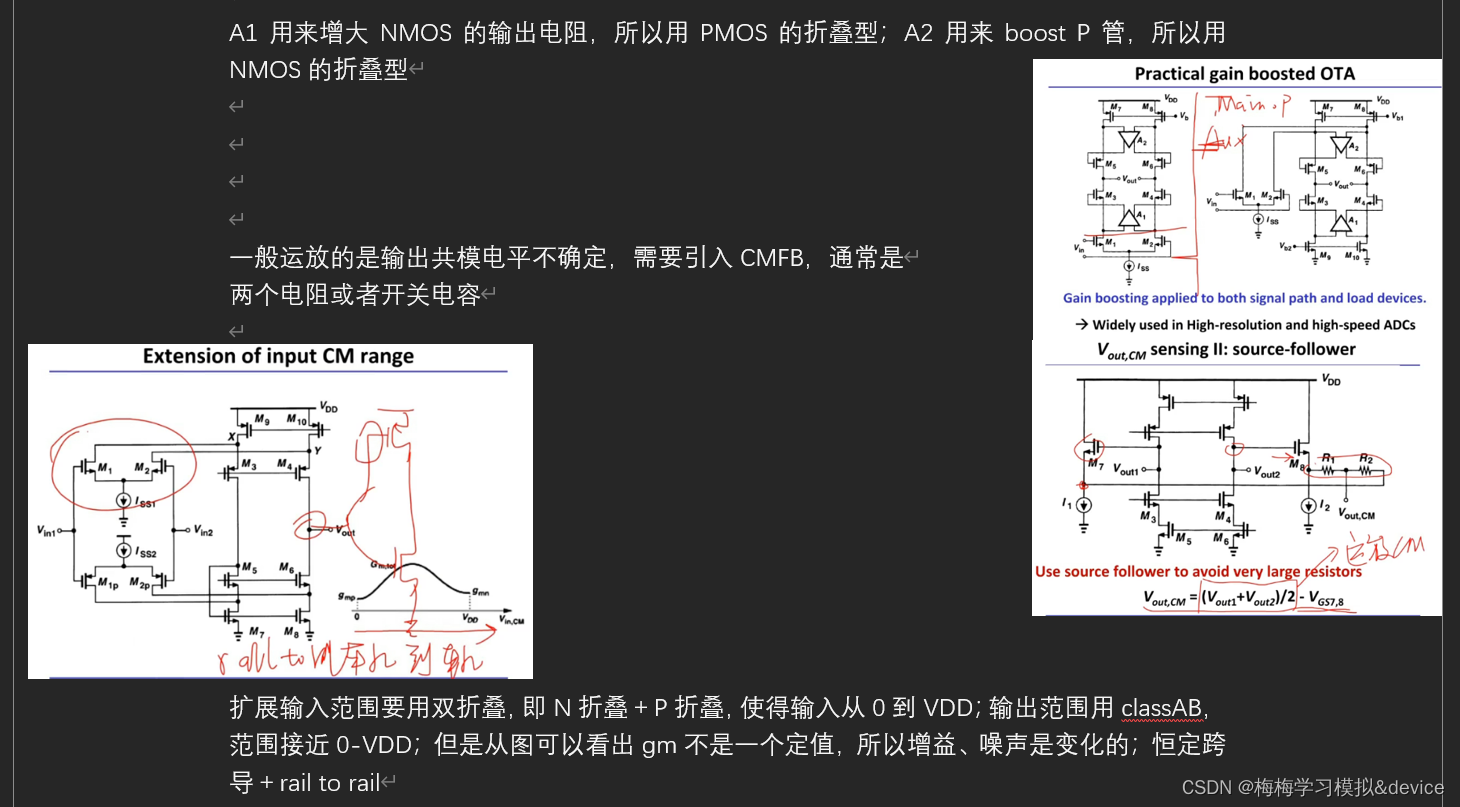

10、 套筒式共源共栅和折叠式共源共栅区别

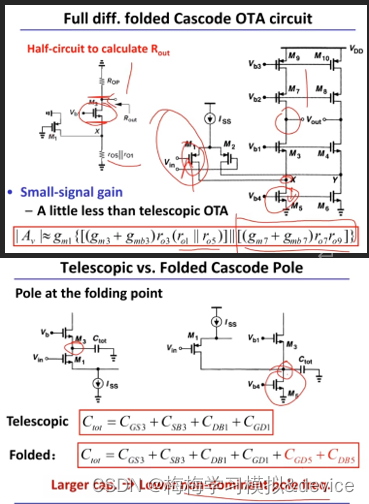

套筒式优点:增益大;AV=gm1(gmn*ron^2//gmp*rop^2);且

套筒越多,增益越大,但是受到电源电压的限制

缺点:将输入输出短接构成单位缓冲器后输出摆幅很小

Vod,ss+vod1+vod3<Vout<vdd-vgs7-vgs5+vth,即

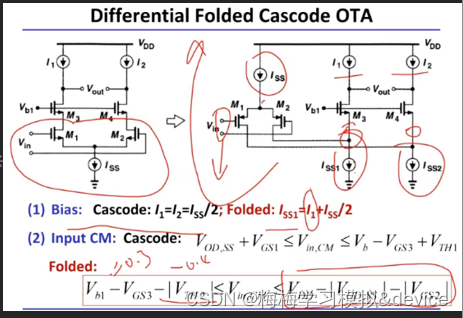

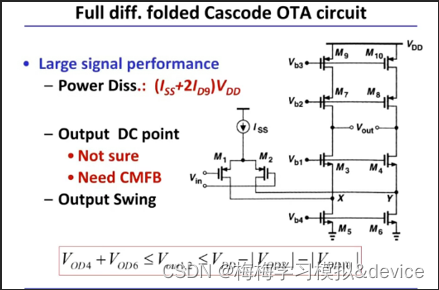

折叠式:

折叠性最大的特点就是将输入与输出隔离开,不会使得

输出受输入影响;原先NMOS漏极电压朝低,NMOS M1进入

线性区;但换成PMOS,漏极电压降低,M1更饱和;换成折叠型一般把输入换个管子

优点:输出摆幅大;

输入摆幅:

输出摆幅:

缺点:折叠式的电容大,第二级点频率小,不稳定;功耗大;

增益有所缩小

文章详细介绍了运算放大器的关键参数,如增益、带宽、失调和输出摆幅,强调了GBW在决定运放速度中的作用。还探讨了运放的设计流程,包括如何根据GBW、输出摆幅和增益需求来确定电路参数。此外,对比了套筒式和折叠式共源共栅结构的优缺点,涉及输出摆幅、稳定性和增益等因素。

文章详细介绍了运算放大器的关键参数,如增益、带宽、失调和输出摆幅,强调了GBW在决定运放速度中的作用。还探讨了运放的设计流程,包括如何根据GBW、输出摆幅和增益需求来确定电路参数。此外,对比了套筒式和折叠式共源共栅结构的优缺点,涉及输出摆幅、稳定性和增益等因素。

4890

4890

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?