结论:

总线周期:存储器和I/O端口是挂接在总线上的,CPU对存储器和I/O接口的访问通过总线实现。把CPU通过总线对微处理器外部(存储器或I/O接口)进行一次访问所需时间称为一个总线周期。也就是完成一次数据传输的时间。

总线周期一般包含4个总线时钟周期:

(1)T1状态 ——输出存储器地址或I/O地址。

(2)T2状态 ——输出控制信号。

(3)T3和Tw状态 ——总线操作持续,并检测READY以决定是否 延长时序。

(4)T4状态 ——完成数据传送。存取周期(存储周期):存取周期包含存取时间和恢复时间。指两次独立访问存储器操作之间的最小间隔。

存取时间指从启动一次存储器操作到完成该操作所经历的时间。

恢复时间指读写操作之后,用来恢复内部状态的时间。

总线周期与存取周期:

底位交叉编址采用轮流启动方式时,这里的一个T就是一个存取周期。到了后期,每隔1/4T的时间,CPU与主存之间就完成一次数据传输。这时,一个总线周期等价于1/4个存取周期(存储周期)。

底位交叉编址采用同时启动方式时:

会同时启动4个模块进行并行的读/写,也就是需要一个存取周期,才能完成一次数据传输,这时,存取周期等于总线周期。

所以一般没有特别说明,总线周期=存取周期

除了存取周期外,机器周期,指令周期与总线周期没有联系:

指令周期:取出并完成一条指令所需要的时间。

机器周期(CPU周期):一条指令的执行过程划分为若干个阶段(如取指、译码、执行等),每一阶段完成一个基本操作。完成一个基本操作所需要的时间称为机器周期。一般情况下,一个机器周期由若干个时钟周期组成 。

讲完这个概念,看王道书上给的7.3.4的第5题与第26题,答案是有点矛盾的。

第5题:

CPU会在每个存储周期(总线周期)结束后检査是否有 DMA 请求。

第26题:

每个机器周期结束后,CPU 就可以响应 DMA 请求。注意区别:DMA 在与主存交互数据时

通过周期窃取方式,窃取的是存取周期。其实还有第27题:

DMA 请求的是总线的使用权,因此 CPU 对 DMA 请求的响应时机是一个总线周期结束时。在流水线 CPU 中,流水段的长度以最复杂的操作所花的时间为准,总线周期(访存时间)通常是耗时最长的,因此通常可认为总线周期、存取周期、机器周期和流水段长度是等价的。

在网上看到的解答:

1.理解两个周期

机器周期:完成一个基本操作的周期,比如说取址,间址

总线周期:使用总线的周期,有的机器周期包含总线周期,比如说"取址周期",要利用总线来传送地址,但是有的机器周期与总线周期无关,比如加法指令的执行周期,只要在运算器中运算,不占用总线,此时这个机器周期执行的时候,总线是空闲的,DMA当然可以使用总线。

2.理解"总线周期后响应"

从传送方式的角度来理解,DMA的传送方式是“周期窃取”,书中有提到,采用周期窃取方式,CPU不使用总线的时候,DMA控制器可以直接使用,并不需要等到CPU机器周期结束。所以说周期窃取,窃取的是总线周期,也就是存取周期。

3.理解“机器周期后响应”:

从中断的角度来理解,在预处理时刻CPU响应DMA请求中断,这种中断的优先级比外中断高,要求CPU尽快响应,但是CPU总得把手里面最基本的事情做完才能响应这个很着急的特殊中断,也就是机器周期后响应DMA

4.总结:

考研范围内:

周期窃取:存取周期

DMA中断响应时刻:机器周期结束时刻

外中断响应时刻:一条指令执行结束时刻

DMA中断优先级>外中断优先级

没有机器周期就选总线周期。

我的理解,结合:

链接:https://www.zhihu.com/question/624019708/answer/3483878438

首先分清DMA请求与中断请求:

DMA请求:

当I/O设备准备好一个字数据之后,I/O设备向DMA控制器发送DMA请求(就是向DMA请求触发器发送高电平信号,使他变为“1”。当控制逻辑检测到一个字的传输已经完成后,会向CPU申请总线控制权),再由DMA控制器向CPU发送总线请求,这两个过程统称为DMA请求。

补充:DMA接口与主存之间传送单元是字,而DMA与设备之间的传送单位可能是字节或位。

DMA中断请求:

传输完多个字后,传送长度计数器会发生溢出,溢出信号会发送给中断机构,中断机构检测到溢出后,向CPU发出中断请求,接着CPU会进行后处理。

发生DMA请求,表示要与主存传送一个字的数据,发生DMA中断请求,表示一整块的数据传输完成。

回到问题:

DMA请求响应:

从CPU角度分析:设备向数据缓冲寄存器传送完一个字的同时,会向DMA请求触发器发送高电平信号,使他变为“1”。当控制逻辑检测到一个字的传输已经完成后,会向CPU申请总线控制权。

CPU收到来自DMA发出的总线控制请求,并将总线控制权移交给DMA控制器,DMA请求属于外部中断,以五段流水线技术为例,外部中断的检测一般放在第一个流水段(IF),故不需要指令冲刷,即不需要将流水段中的控制信号清零,故可以让已经在流水段中的指令继续执行完。不过下一个时钟周期的IF流水段取的指令就是有关DMA请求的指令了。从上面可以看出,CPU响应DMA请求总是在接收到DMA请求的机器周期的下一个机器周期开始执行DMA请求的相关指令(因为在下一个机器周期才把DMA请求的指令取进来,这里一个流水段周期就是一个机器周期),综上,CPU响应DMA请求总是在当前机器周期的下一个机器周期开始。

从I/O系统的角度分析,DMA控制器向CPU申请总线的控制权,CPU对DMA控制器的响应肯定是在完成当前这个总线事务之后,也就是本次总线周期结束。

DMA中断请求响应:此时一整块的数据传输已经完成了。DMA控制器传输完数据后,释放总线控制权并向CPU发出中断请求,这个动作是DMA控制器发出的,发生在DMA完成最后一个字的传输这一总线事务之后。所以DMA中断请求的响应,肯定是在完成总线事务,即一个总线周期之后。

按这样的理解:从CPU的角度看,那么应该是机器周期执行完响应DMA请求。

对于2013年的这道真题:

B项是正确的,从I/O角度看,DMA 响应发生在一个总线事务完成后。况且A正确,那么B顺着A理解也是正确的。

总结:

对于DMA的响应优先选择总线周期(因为申请总线控制权,肯定要在当前总线周期结束才能申请),没有总线周期就选存取周期,因为不特别说明,总线周期等价于存取周期。没有以上两个就选机器周期。

对于周期挪用,即周期窃取,针对的就是存取周期,周期挪用就是CPU与DMA控制器同时竞争主存,当CPU正在使用主存时,只有到当前存取周期后,CPU再将总线占有权让出,针对的就是存取周期。

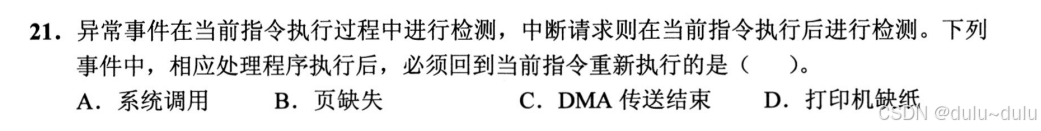

21年这道题有涉及DMA中断请求:

A,B都属于内中断(异常),异常发生在指令执行过程中。A.系统调用是通过"陷入"完成的,系统调用执行完后,执行下一条指令,如果是转移指令就跳到转移目标指令执行。B.页缺失属于异常,执行完后返回当前指令重新执行。

D.属于外部中断,一条指令执行完毕后,才检测是否有外部中断。

C.DMA 请求只请求总线的使用权,不影响当前指令的执行,不会导致被中断指令的重新执行

既然讲到了DMA请求与DMA中断方式,那么还有一点:DMA方式的优先级大于程序中断方式

DMA请求优先级非常高,因为DMA一般连接高速设备,如果不及时响应这个请求,不及时把总线优先权交给DMA控制器,那么DMA控制器的数据还没有被传输到主存,可能就被覆盖了。

读一读:

DMA传送方式的优先级高于程序中断,两者的区别主要表现在对CPU的干扰程度不同。程序中断请求不但使CPU停下来,而且要CPU执行中断服务程序为中断请求服务,这个请求包括了对断点和现场的处理以及CPU与外设的传送,所以CPU付出了很多的代价;DMA请求仅仅使CPU暂停一下,不需要对断点和现场的处理,并且是由DMA控制外设与主存之间的数据传送,无需CPU的干预,DMA只是借用了一点CPU的时间而已。

所以DMA方式的优先级,甚至大于不可屏蔽中断。

所以:

DMA请求>不可屏蔽中断>内部异常>可屏蔽中断。

内部异常:

硬件故障(终止)>软件中断(故障,自陷)。

而对于DMA中断请求:

DMA 中断请求 > I/O 设备的中断请求

在 I/O 传送类中断请求中:

高速设备 > 低速设备

输入设备>输出设备

实时设备>普通设备

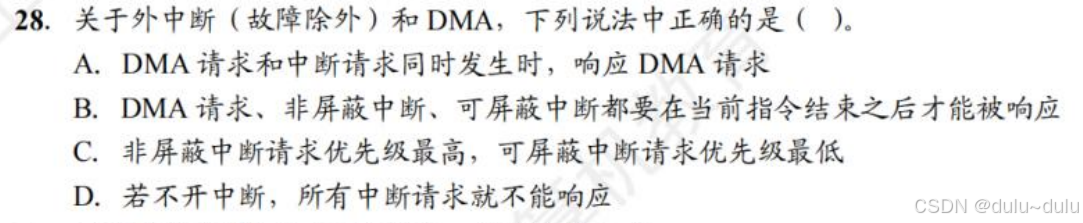

A:优先响应DMA请求 B:DMA请求与非屏蔽请求都是必须立即响应的,不能等到当前指令结束 C:DMA请求优先级最高 D:关中断时,异常和不可屏蔽中断是能响应的,关中断能挡住的是可屏蔽的 外部中断

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?