一、实验要求:

1、首先用 multisim (或logsim)采用门电路或者74LSxx系列设计基本RS、D触发器,进行仿真,写成真值表。

2、在控制台上,用硬件联线完成SR触发器、D触发器的实际电路,对真值表进行验证并记录。

二、实验设计

1.RS锁存器

(1)Logsim仿真

RS锁存器特征表

| R | S | Q |

|---|---|---|

| 0 | 0 | 1 |

| 1 | 0 | 0 |

| 0 | 0 | 保持上一个状态 |

| 1 | 1 | 禁止、不稳状态 |

RS锁存器是时序电路的基础。基本的RS锁存器可以用两个与非门或或非门实现,由于没有74LS02芯片,这里使用与非门实现RS锁存器。

其原理图如下所示。

输入端:

R:复位端(Reset)

S:置位端(Set)

输出端:

Q:状态输出端

Q’:反相状态输出端

在Logsim的仿真电路图如下:

仿真后的真值表为:

| R | S | Q | Q’ |

|---|---|---|---|

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 维持上一个状态 | 维持上一个状态 |

| 0 | 0 | 1 | 1 |

R-S触发器结论

1.R、S的有效电平是低电平。

2.不论现态如何,在R端输出低电平能将现态强制性地转换到“0”态;

在S端输出低电平能将现态强制性地转换到“1”态;

R和S不能同时事假低电平。

引入74LS00芯片后电路图如下:

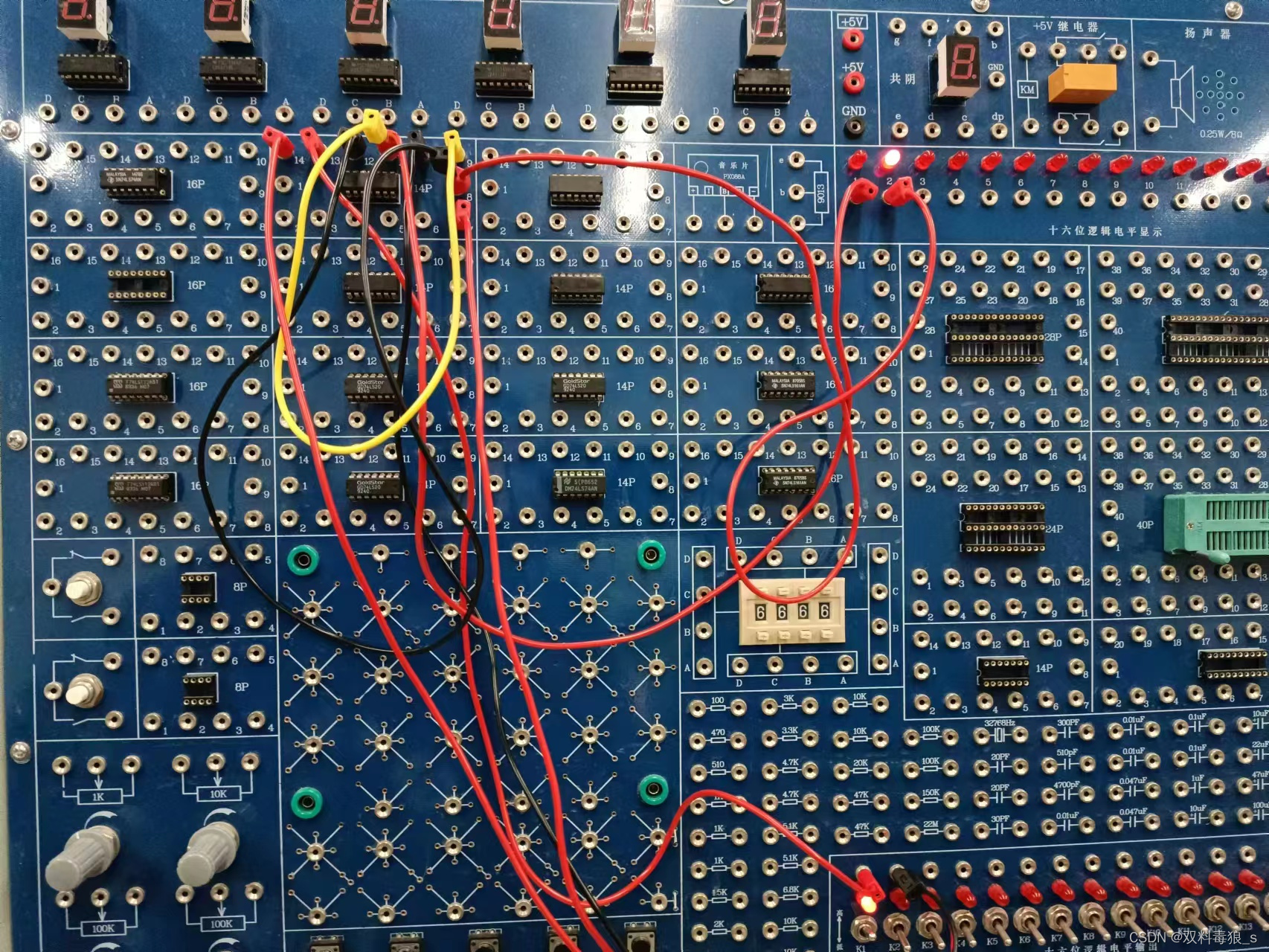

(2)控制台接线

接好后的逻辑真值表与仿真结果一致。

2.D触发器

RS触发器当输入端均为1是,输出为不确定的状态。为解决这一问题,引入D触发器。

(1)Logsim仿真

下图是D触发器的原理图,目的是解决输入的约束问题。

工作原理:

- CP=0 : 时钟封锁G3,G4;致使D的变化不能传入G1,G2。触发器保持现态。

- CP=1:时钟封锁解除,D的变化传入G1,G2。若D=0,Q=0;若D=1,则Q=1;

理论逻辑真值表如下:

| CP | D | Q |

|---|---|---|

| 0 | 0 | 保持不变 |

| 0 | 1 | 保持不变 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

logsim仿真电路图如下所示:

符合理论逻辑真值表。

引入74LS00后如下:

D触发器结论

1.当CP=0时,无论如何改变D,输出都不会被改变。

2.当CP=1时,输出随D的改变而改变,D是多少输出就是多少。

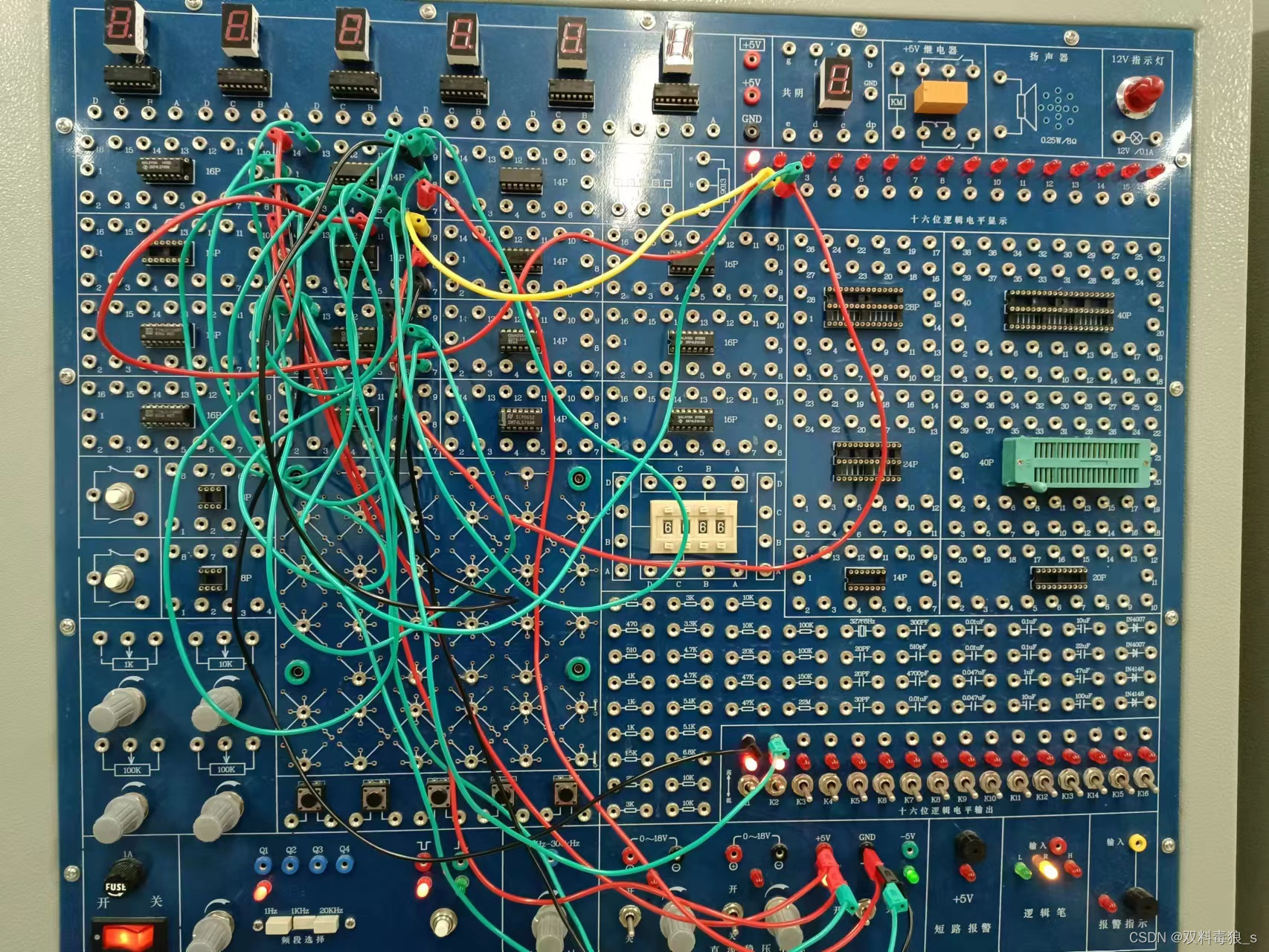

(2)控制台接线

三、拓展与延伸

为了解决D触发器“空翻”的问题,这里引入维持阻塞D触发器。

效果:

当且仅当CP的上升沿出现的一瞬间,D的数据才能置入触发器。

其原理图如下:

logsim仿真电路图如下:

四、实验小结

1.在根据各个输入的电平判断输出电平时,要注意是否有CP封锁。

2.在CP未封锁时,只要R为低电平就是“0”,S为高电平就转换“1”。

6568

6568

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?