提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

一、RS触发器

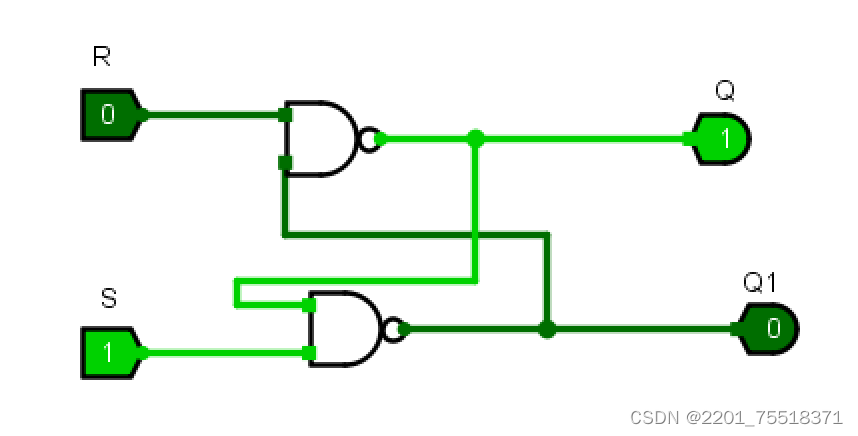

RS触发器是时序电路中的基础电路,可以存储一位数据。它可以由两个或非门或者两个与非门实现,考虑到实际操作时硬件的条件,这里就用与非门实现。

logsim中的仿真电路如下:

仿真后得出的真值表如下:

| R | S | Q | Q1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 9 | 0 | 1 |

| 1 | 1 | 状态不稳定,与上个状态保持一致 | |

仿真过后我们可以使用74LS00芯片进行实际电路的搭建,因为只有两个与非门,所以在74LS00芯片上任选两组即可。

实验得出的真值表与仿真电路一致。

结论:1、在S端输入低电平能将现态强制转换到“1”态

在R端输入低电平能将现态强制转换到“0”态

2、R和S端的有效电平是低电平

二、D触发器

1、原理

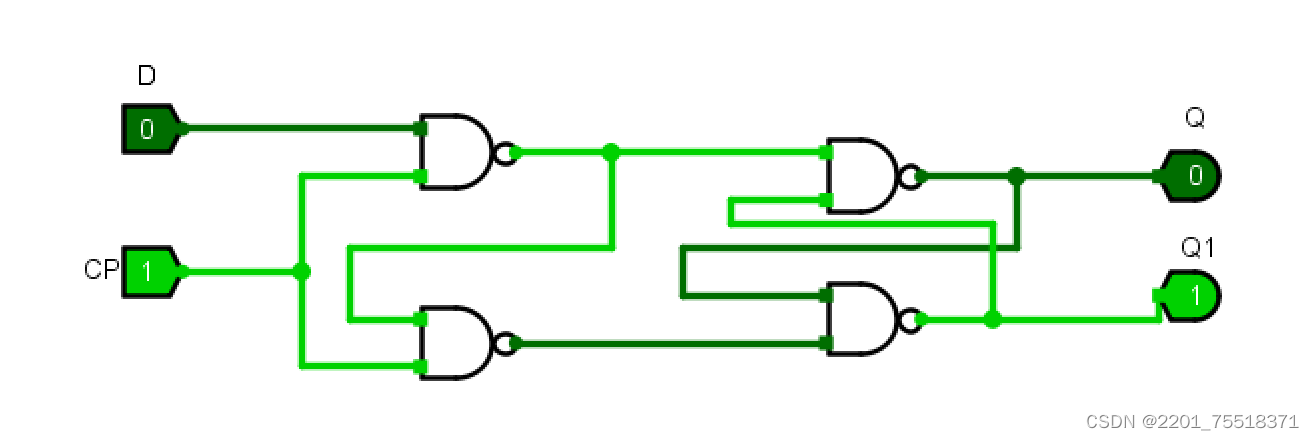

当输入S=1、R=1时,RS触发器的输出状态不稳定,因而又引入D触发器。D触发器中引入时钟,只有当CP端输入1时,D的输入才有效。其仿真电路如下:

根据仿真电路得出的真值表如下:

| D | CP | Q |

| 1 | 0 | 不定 |

| 0 | 0 | 不定 |

| 0 | 1 | 0 |

| 1 | 1 | 1 |

仅能当CP=1时,D端的输入才有效,并且Q的状态与D一致。在实际中可用74LS00芯片完成电路的搭建,其logsim的电路图如下:

根据此图在电路中将芯片的各个引脚连接好即可得到相应的结果。

2.空翻

空翻现象,又称为竞态现象,是数字电路中的一个术语,指在同一个时钟脉冲信号作用区间内,由于时钟脉冲的宽度过大,触发器出现在“0”“1”两逻辑信号中多次翻转的现象。

以时控D触发器为例,CP=0时,此时Q=0;当CP=1时,此时Q=1,此时Q因为D的值变化而从原来的0变成1,此时依然处于CP=1的时钟周期内,继续改变D的值,让D=0,这个时候Q还是w会因为D的值变化而继续变化,从刚才的1变成0。在cp=1的整个时钟周期内,Q从0变成1,再从1变成0;如果继续改变D的值,Q还会变化。空翻会让触发器结果产生错误。因此我们又引入了维持阻塞D触发器。

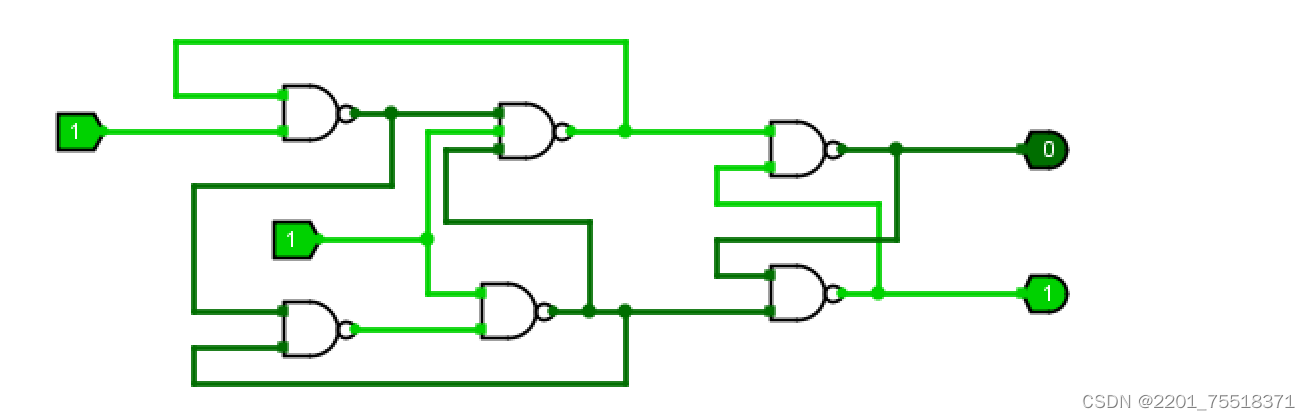

三、维持阻塞D触发器

维持D触发器就很好的解决空翻的问题,只有当CP上升的一瞬间,D端的数据才会被置入触发器。

其仿真图如下:

CP上升后D端再输入数据将不再起作用,因此也解决了空翻的问题。

总结

时序电路比逻辑电路更复杂,所以需要更加耐心的理解,基础的元器件需要理解透彻。

本文介绍了RS触发器的基本原理和功能,包括其在不同输入下的行为。随后详细讲解了D触发器,包括其工作原理、真值表以及空翻现象。最后,提到了维持阻塞D触发器如何防止空翻问题,强调了时序电路学习的重要性。

本文介绍了RS触发器的基本原理和功能,包括其在不同输入下的行为。随后详细讲解了D触发器,包括其工作原理、真值表以及空翻现象。最后,提到了维持阻塞D触发器如何防止空翻问题,强调了时序电路学习的重要性。

2141

2141

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?