目录

1、首先用logisim采用门电路设计RS和D触发器,进行仿真,写成真值表。

二.使用logisim采用门电路设计RS触发器,写成真值表并验证其逻辑关系

(3)设计一个CP上升沿触发的改进型的D触发器(维持阻塞D触发器)

2、在控制台上,用硬件联线完成RS触发器、D触发器的实际电路,对真值表进行验证并记录。

一.用硬件联线完成RS触发器的实际电路,对真值表进行验证并记录

二.用硬件联线完成D触发器的实际电路,对真值表进行验证并记录

1、首先用logisim采用门电路设计RS和D触发器,进行仿真,写成真值表。

一.RS触发器的基本原理

定义

RS锁存器,我们可以简单将它理解为一个存储单元,可以存储一位数据(0或者1)。 基本的RS锁存器可以用两个与非门或者或非门实现。

电路组成

将两个与非门的输入,输出端交叉相连,就组成一个基本RS触发器,如下图(a)所示。图(b)是基本RS触发器的逻辑符号。

逻辑功能

(1)/R=1, /S=1,触发器保持原来的状态不变

不管触发器原来是什么状态,基本RS触发器在/R=1,/S=1时,总保持原来的状态不变。这就是触发器的记忆功能。若输入端/R,/S 悬空,可认为加入高电平,即/R=1,/S=1。

(2)/R=0, /S=1,触发器为0态

此时,因 /R=0,G1的输出 /Q=1,而G2的两个输入端/S,/Q全为1,则输出Q=0。触发器为零态,并且与原来的状态无关。

(3)/R=1, /S=0,触发器为1态

由于/S=0,G2的输出Q=1。这时G1的两个输入端均为1,所以/Q=0。触发器为1态,同样与原来的状态无关。

(4)/R=0, /S=0,触发器的状态不定

这时,Q=1,/Q=1。破坏了前述有关Q与 /Q互补的约定,这是不允许的。而且,当 /R,/S的低电平触发信号消失后,Q与/Q的状态保持是不确定的。这种情况应该避免。

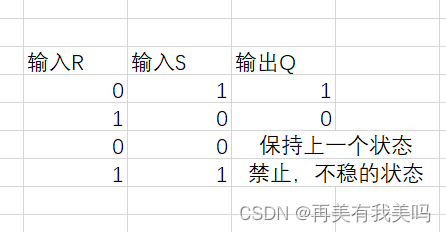

二.使用logisim采用门电路设计RS触发器,写成真值表并验证其逻辑关系

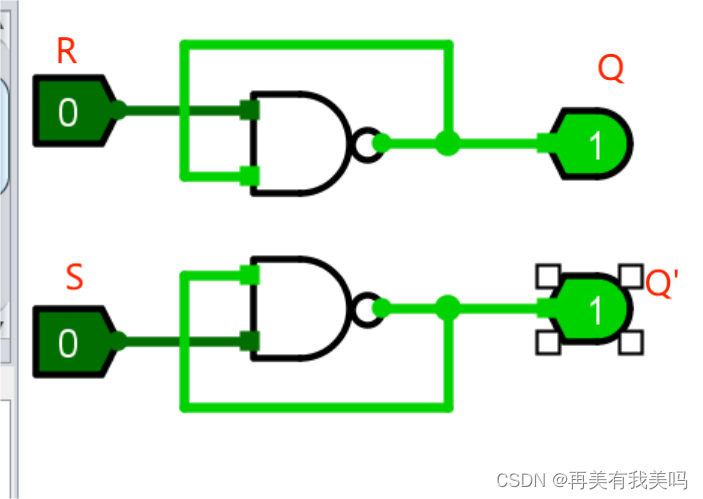

(1)采用门电路设计RS触发器

用与非门构成的基本R-S触发器

输出端:

Q:状态输出端

Q':反相状态输出端

输入端:

R:置位端(Set)

S:复位端(Reset)

没有时钟输入端

输入信号R,S的作用方式:低电平有效。

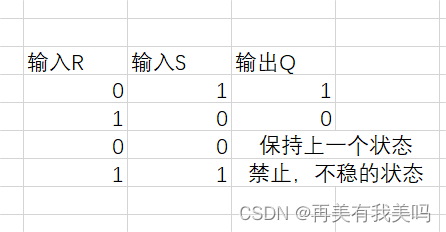

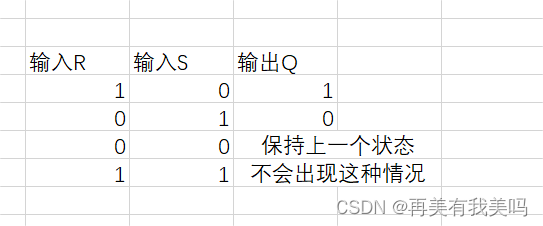

真值表

(2)验证Q的输出

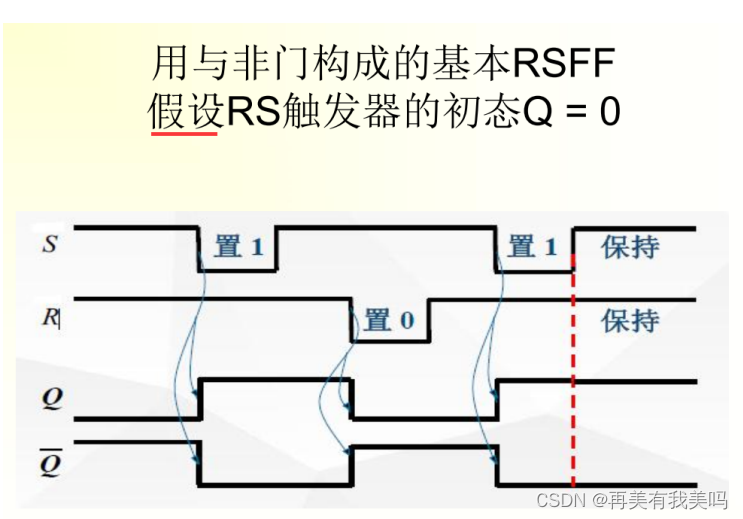

请使用一个基本的RS触发器,然后按照以下波形控制输入R、S信号的高低电平,验证Q的输出是否符合 上述逻辑关系。

上图中S为置位端,R为复位端。

通过使用logisim软件进行仿真实验可知,Q的输出符合上述逻辑关系。

四.D触发器的基本原理

D触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。

因此,D触发器在数字系统和计算机中有着广泛的应用。触发器具有两个稳定状态,即0和1,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。

D触发器有集成触发器和门电路组成的触发器。触发方式有电平触发和边沿触发两种,前者在CP(时钟脉冲)=1时即可触发,后者多在CP的前沿(正跳变0→1)触发。

D触发器的次态取决于触发前D端的状态,即次态=D。因此,它具有置0、置1两种功能。

对于边沿D触发器,由于在CP=1期间电路具有维持阻塞作用,所以在CP=1期间,D端的数据状态变化,不会影响触发器的输出状态。

D触发器应用很广,可用做数字信号的寄存,移位寄存,分频和波形发生器等等。

五.使用logisim采用门电路设计D触发器

前面RS触发器当输入R=1,S=1的情况时,输出是不确定的状态,这种情况比较棘手。因此为了解决这 个问题,又引入了D触发器。

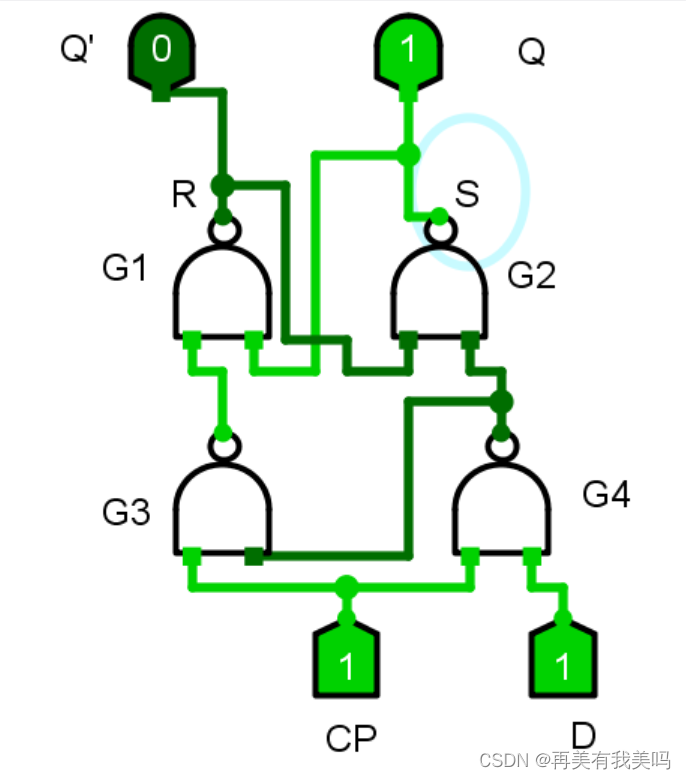

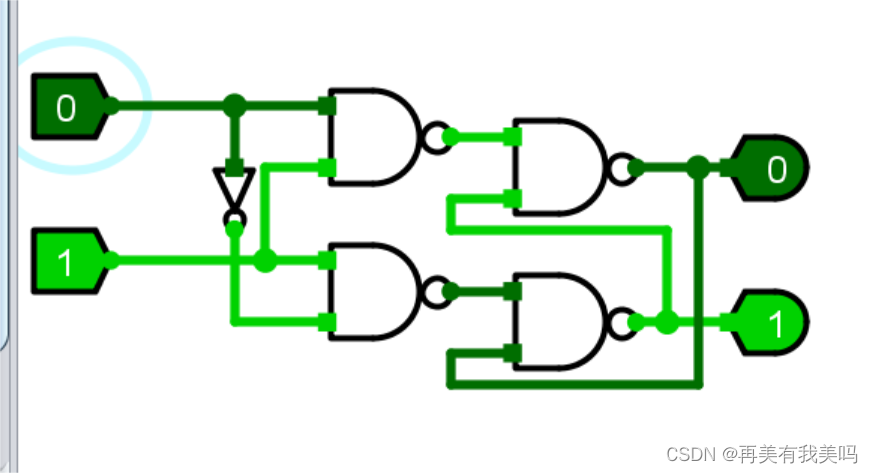

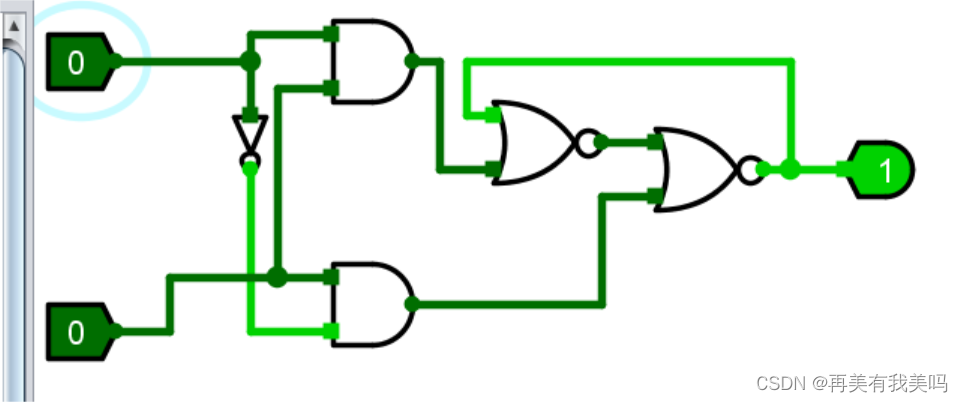

(1)用与非门设计实现一个D触发器。

(2)验证输入D、CP和输出Q的逻辑关系

输入D、CP和输出Q的逻辑关系:CP=0时,G3,G4被封锁,D的变化不能传到G1,G2,触发器保持现有状态。CP=1时,G3,G4门开放,D经G3,G4转换成一对互补信号送到G1,G2。

若D=0,则RS=01,Q=0;

若D=1,则RS=10,Q=1。

经验证,输入D、CP和输出Q的逻辑关系正确无误。

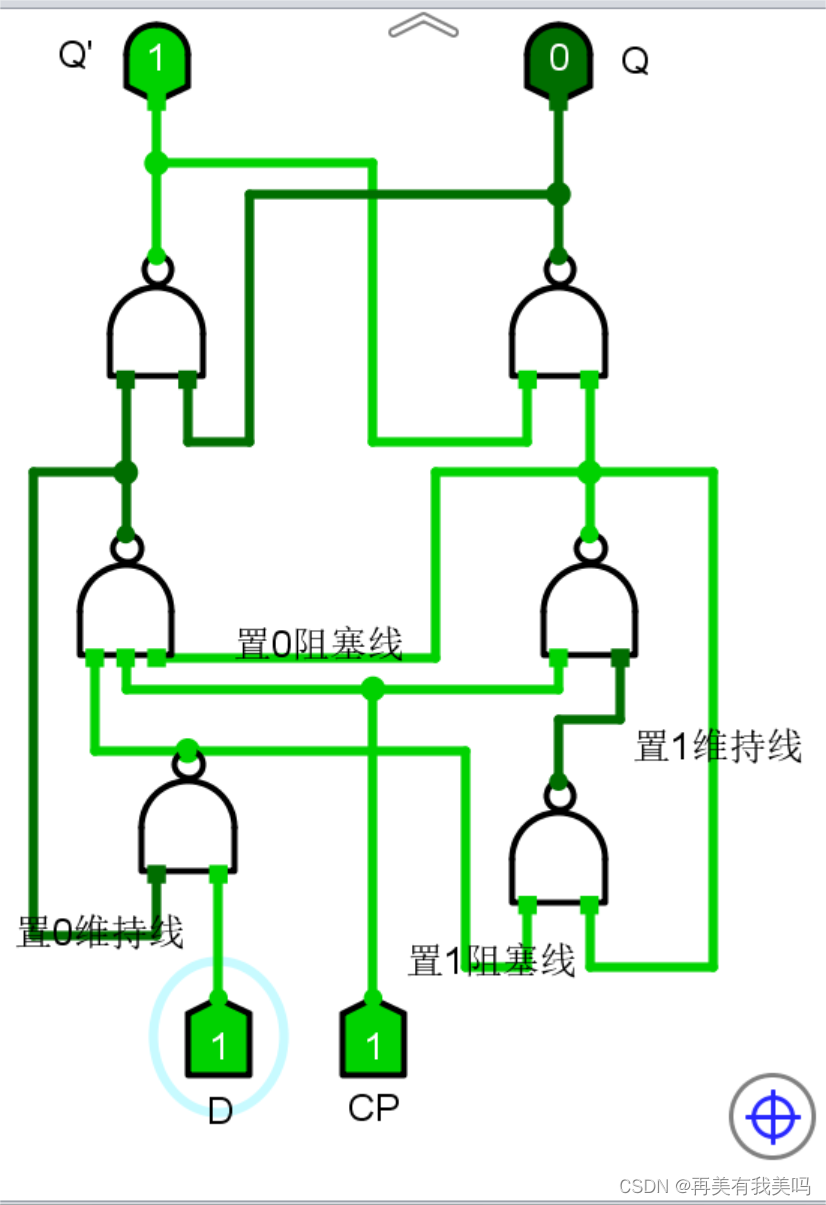

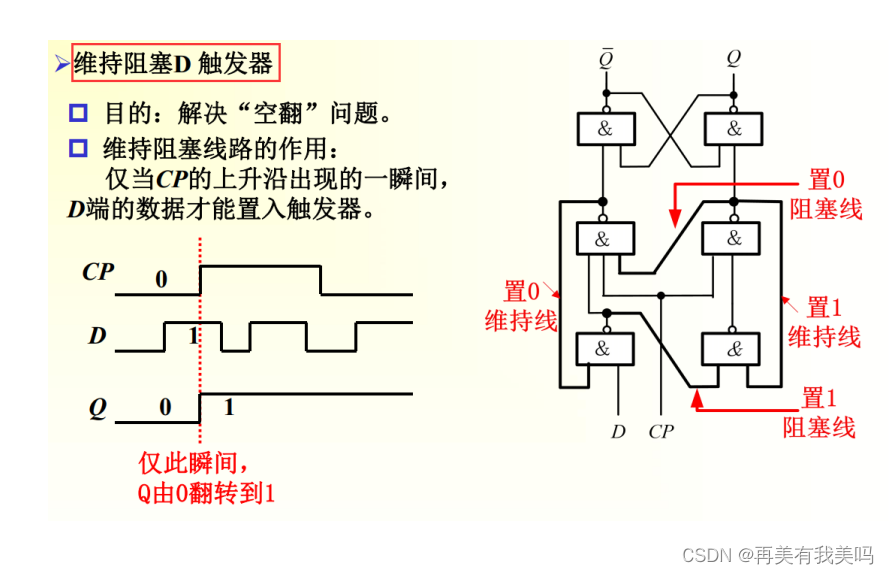

(3)设计一个CP上升沿触发的改进型的D触发器(维持阻塞D触发器)

具体如下图所示:

(4)验证维持阻塞D触发器的输入输出逻辑关系

维持阻塞D触发器的输入输出逻辑关系:

使用logisim仿真软件进行实验,经验证维持阻塞D触发器的输入输出逻辑关系正确。

(5)其他

使用或非门设计D触发器

使用与非门与非门设计D触发器

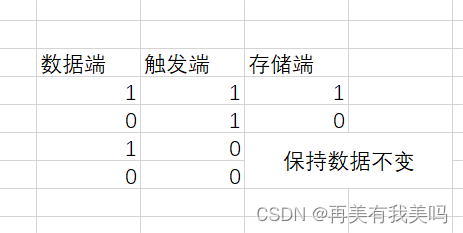

真值表

为了解决输入端不能同时为1的问题,我们将电路进行改善

真值表

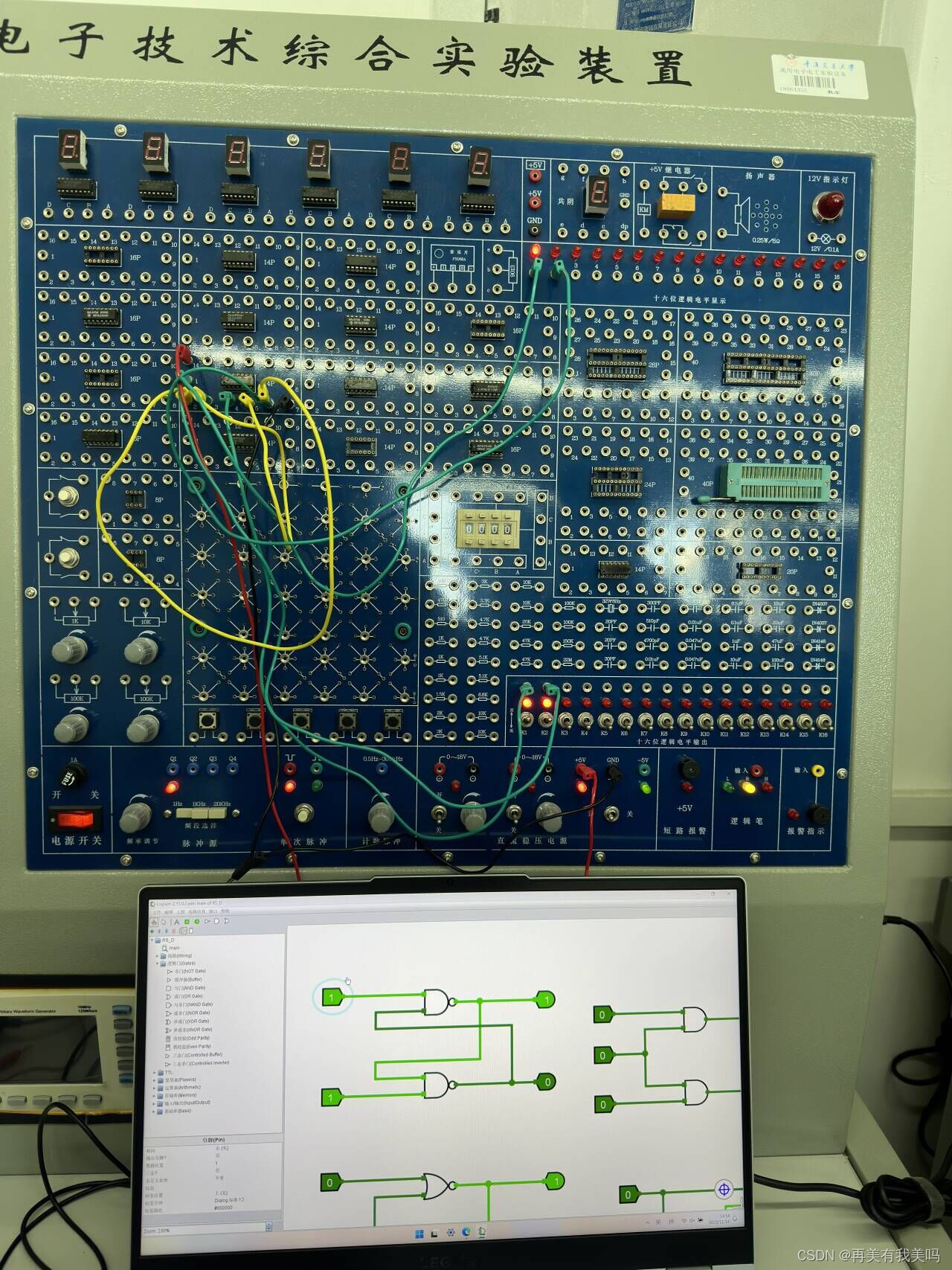

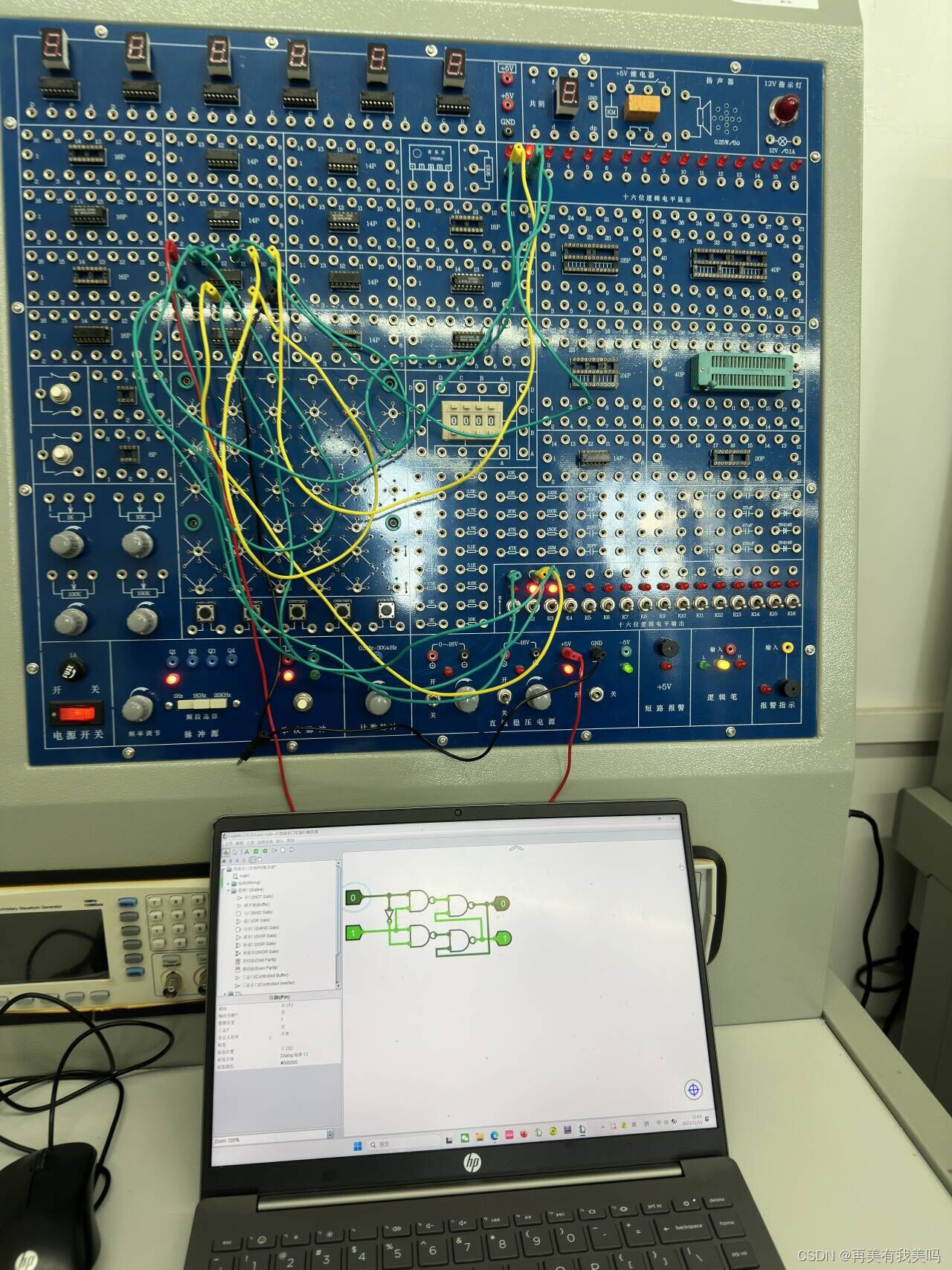

2、在控制台上,用硬件联线完成RS触发器、D触发器的实际电路,对真值表进行验证并记录。

一.用硬件联线完成RS触发器的实际电路,对真值表进行验证并记录

RS触发器的实际电路

经检验,实操后记录的真值表

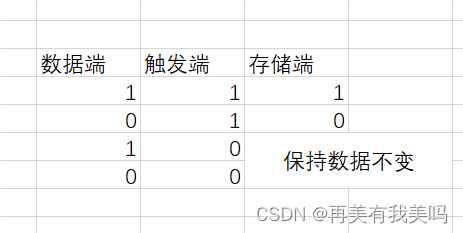

二.用硬件联线完成D触发器的实际电路,对真值表进行验证并记录

D触发器的实际电路

经检验,实操后记录的真值表

3、总结

1.R-S触发器中的R和S不能同时施加低电平。

2. R-S触发器两个输入端口S和R的输入信号必须是非重叠的。

3.实验时应当注意安全,避免触电,短路等危险情况。

4.实验时应注意触发器的类型,输入信号的类型和时序信号的变化,确保实验结果正确。

868

868

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?