DMA简介

- DMA(Direct Memory Access)直接存储器存取;

- DMA可以提供外设和存储器或者存储器和存储器之间的高速数据传输,无须CPU干预,节省了CPU的资源;

- 12个独立可配置的通道:DMA1(7个通道)、DMA2(5个通道)

- 每个通道都支持软件触发和特定的硬件触发;

- STM32F103C8T6 DMA资源:DMA1(7个通道)

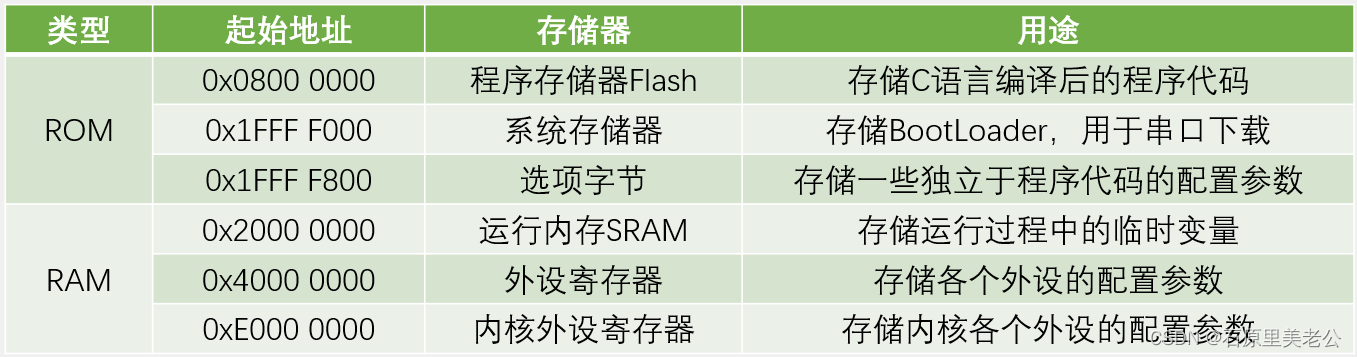

存储器映像

DMA数据转运本质上是从存储器到存储器的数据转运;

- ROM是只读存储器,是一种非易失性、掉电不丢失的存储器,RAM是一种随机存储器,是一种易失性、掉电丢失的存储器;

- 存储器起始位置是固定的,而终止位置取决与存储内存,内存多大则终止位置多大;

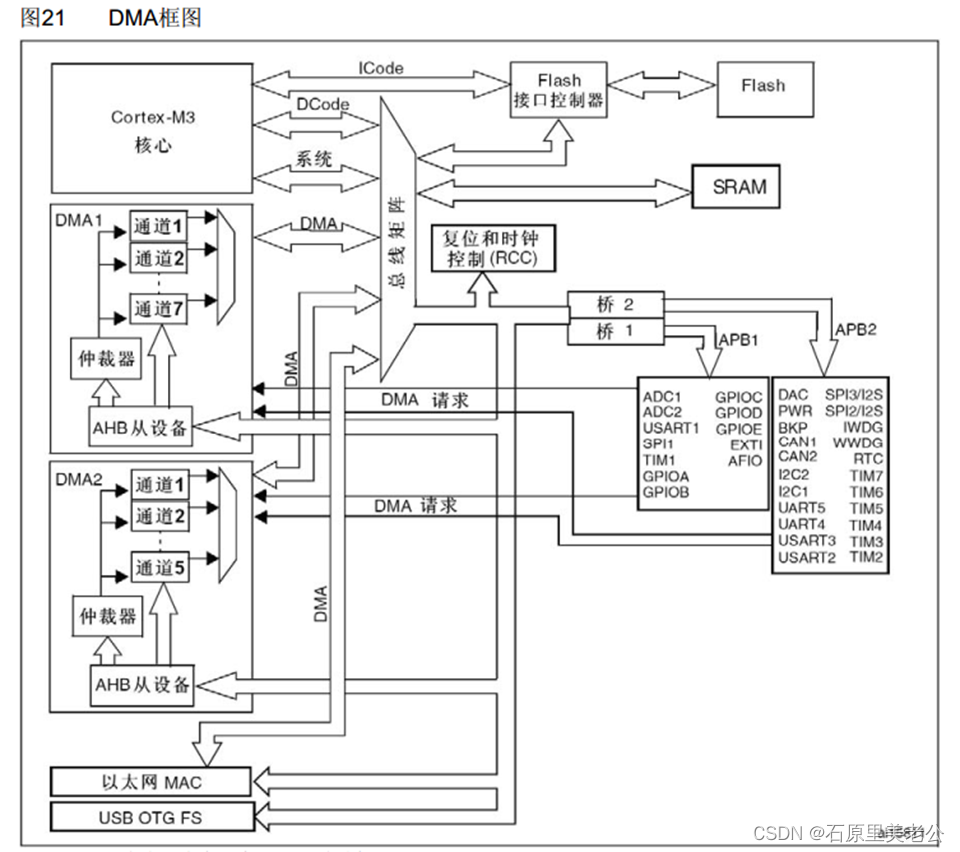

DMA框图

- 寄存器是一种特殊的存储器,一方面,CPU可以对寄存器进行读写,就像读写内存一样,另一方面,寄存器的每一位背后,都连接了一根导线,可以用于控制外设电路的状态,比如导通和断开开关、置引脚的高低电平等;所以寄存器是连接软件和硬件的桥梁。

- 总线矩阵的左端是主动单元,主动单元有内核CPU和DMA总线,拥有存储器的访问权,右端是被动单元,它们的存储器只能被左端的主动单元读写;

- DCode是专门访问Flash的,系统总线是访问其他东西的;

- DMA的各个通道可以分别设置他们转运数据的源地址和目的地址,仲裁器的作用是根据通道的优先级来决定哪个通道先转运;

- AHB从设备是DMA自身的寄存器,所以DMA既是总线矩阵上的主动单元,可以读写各种寄存器,也是AHB总线上的被动单元;

- DMA请求就是DMA触发源;

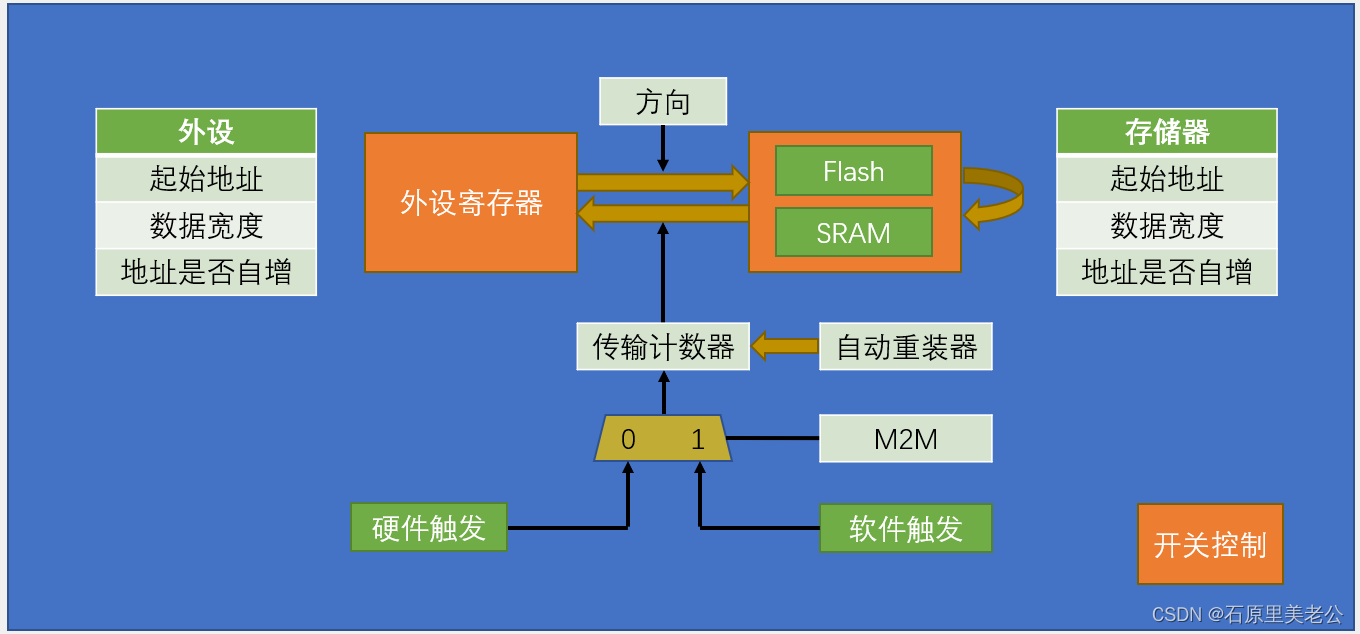

DMA基本结构

- 起始地址:有外设端的起始地址,和存储器端的起始地址,这两个参数决定数据从哪里来,到哪里去;

- 数据宽度:指定一次转运要按多大的数据宽度来进行,口语选择字节Byte(8位)、半字HalfWord(16位)、字Word(32位)

- 地址是否自增:指定一次转运完成后,下一次转运,是不是要把地址移动到下一个位置去,相当于指针p++;

- 传输计数器:用来指定总共需要转运几次;是一个自减计数器,每转运一次计数器的数减1,当计数器的值减到0后,之前自增的地址恢复到起始地址的位置,以方便DMA开启新一轮转换;

- 自动重装器:传输计数器减到0之后,是否要自动恢复到最初的值;不重装就是简单的单次模式,重装就是循环模式,相对于ADC的连续模式;

- 触发控制就是决定DMA在什么时机开始转运,有硬件触发和软件触发,由M2M决定;软件触发的执行逻辑是:以最快的速度,连续不断的触发DMA,争取早日把传输计数器清零,完成一轮传输,即连续触发,所以软件触发和循环模式不能同时使用;

- 软件触发一般适用于存储器到存储器的转运,因为存储器到存储器的转运是软件启动、不需要时机、想尽快完成的任务;

- 硬件触发源可以选择ADC、串口、定时器等等,使用硬件触发的转运, 一般都是与外设有关的转运,需要一定的时机,在硬件达到这个时机时,传一个信号来触发DMA进行转运;

- DMA进行转运的条件:开关控制;传输计数器必须大于0;触发源必须有触发信号;

- 注意写传输计数器时,必须先关闭DMA,再进行写入传输计数器,然后再开启DMA进行下一轮转运;

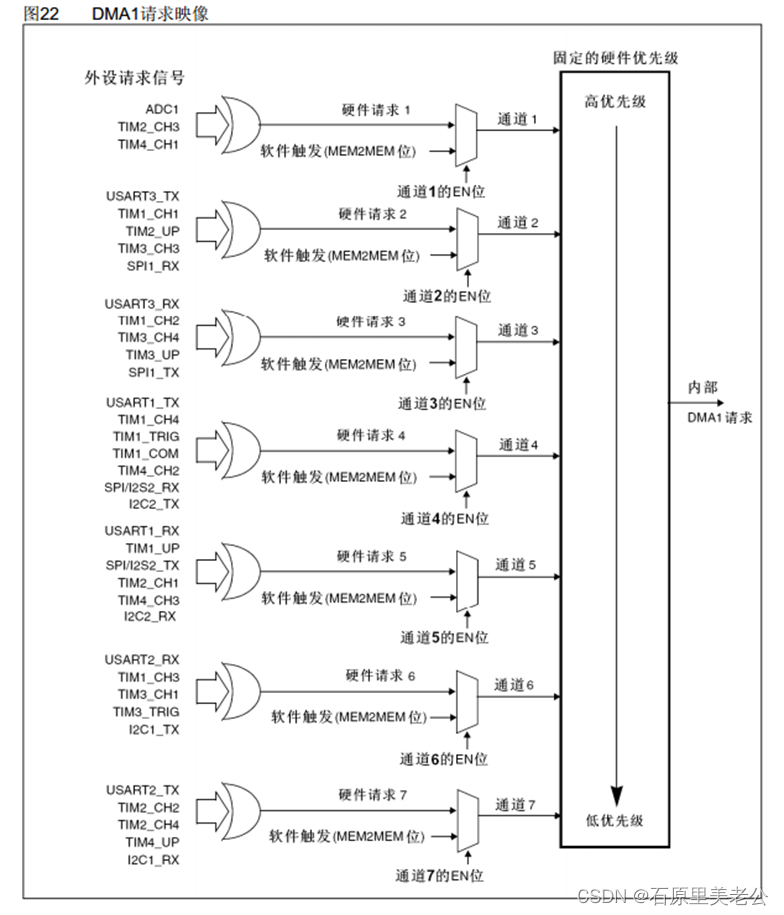

DMA请求

因为每个通道的硬件触发源都不同,所以想使用某个硬件触发源的时候,必须选择对应的通道;而软件触发可以随意选择,因为每个通道的软件触发都是一样的;

因为每个通道的硬件触发源都不同,所以想使用某个硬件触发源的时候,必须选择对应的通道;而软件触发可以随意选择,因为每个通道的软件触发都是一样的;

仲裁器的优先级原则是通道号越小,优先级越高;

数据宽度与对齐

如果目标宽度比源端宽度大,就在数据前面补0;

如果目标数据宽度比源端数据宽度小,就把多出来的高位舍弃;

例子

数据转运+DMA

两个站点的数据地址都需要自增

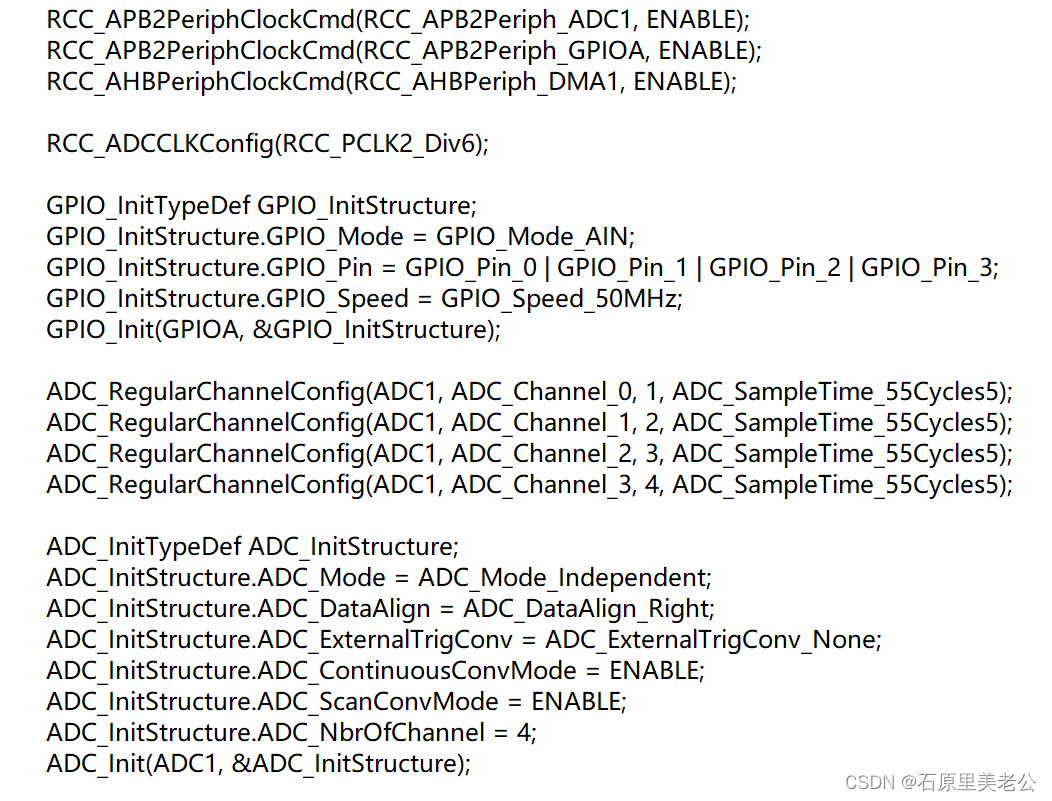

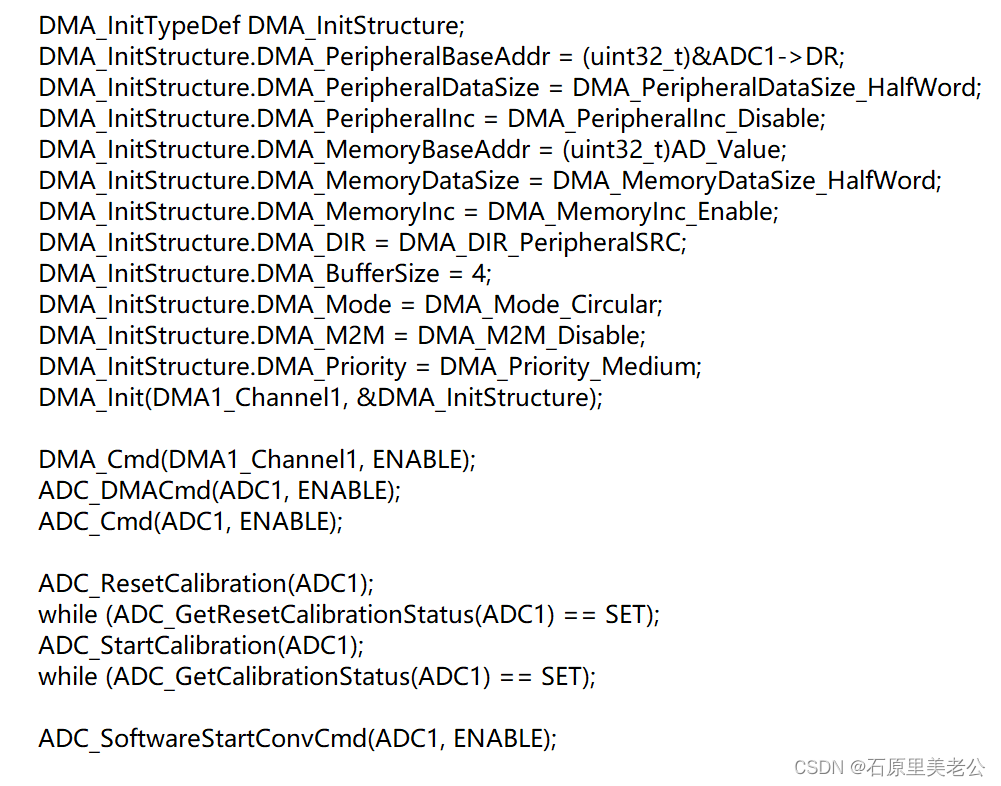

ADC扫描模式+DMA

外设地址不自增,存储器地址自增;

如果ADC是单次扫描,DMA的传输计数器可以不自动重装;如果ADC是连续扫描,DMA可以使用自动重装,在ADC启动下一轮转换的时候,DMA也启动下一轮的转运;

DMA转运的时机,需要与ADC单个通道转换完成同步。ADC单个通道的数据转换完成后,会产生一个DMA请求;

代码

DMA数据转运

接线图

代码思路

- RCC开启时钟;(DMA是AHB总线的设备)

- 调用DMA_Init初始化参数,包括外设和存储器站点的起始地址、数据宽度、地址是否自增、方向、传输计数器。是否需要自动重装、选择触发源、通道优先级;

- 开关控制,给指定地通道使能;

- 如果选择硬件触发,要在对应外设调用xxx_DMACmd,开启触发信号的输出;

库函数

- DMA_SetCurrDataCounter用于给传输计数器写数据;

- DMA_GetCurrDataCounter用于获取当前数据寄存器,返回传输计数器的值;

- 最后四个函数:获取标志位、清除标志位、获取中断状态、清除中断挂起位;

DMA-AD多通道

接线图

代码

总结

本节涉及的内容对应手册里的第二章 存储器和总线架构、以及第十章 DMA控制器。

139

139

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?