主要记录自己在利用verilog实现串口的时候一些简单的介绍和遇到问题和思考。备忘

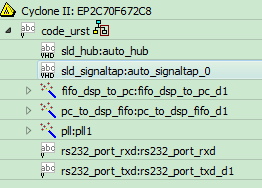

1、串口传输格式,可以百度,有很多也很简单。串口分为两部分,一个收,一个发。所以在verilog实现时可以把这两部分分开。也就是两个fifo配套收和发的.v文件,可以实现一个串口。一般人实现串口的都是这么想的吧。下面是文件的层级结构:

2、当然是coding了。写串口的代码。主要贴一下收和发的状态机(用一段来实现的):

(1)这是收的部分:

case(state_rxd)

state_rxd_idle : //0

begin

finished_rxd <= 1'b0;

rxd_error <= 1'b0;

if((!rxd_write_full) && ({port_rxd_d3,port_rxd_d2,port_rxd_d1}==3'b100))

begin

state_rxd <= state_rxd_head;

time_rxd <= 1'd0;

end

else

state_rxd <= state_rxd_idle;

end

state_rxd_head : //1

begin

if((time_rxd == rxd_half_band_rate) && ({port_rxd_d3,port_rxd_d2,port_rxd_d1}==3'b000))

begin

time_rx

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3606

3606

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?