概要

本项目主要以龙芯2k1000为CPU实现整个系统的管理,主要实现数据交换、时间同步和数据监控等功能。项目中龙芯作为一部分存在,考虑到项目涉密的原因,不能将整个项目的应用背景及项目整体方案做介绍,只能将龙芯过程开发做一个分享总结。

整体架构

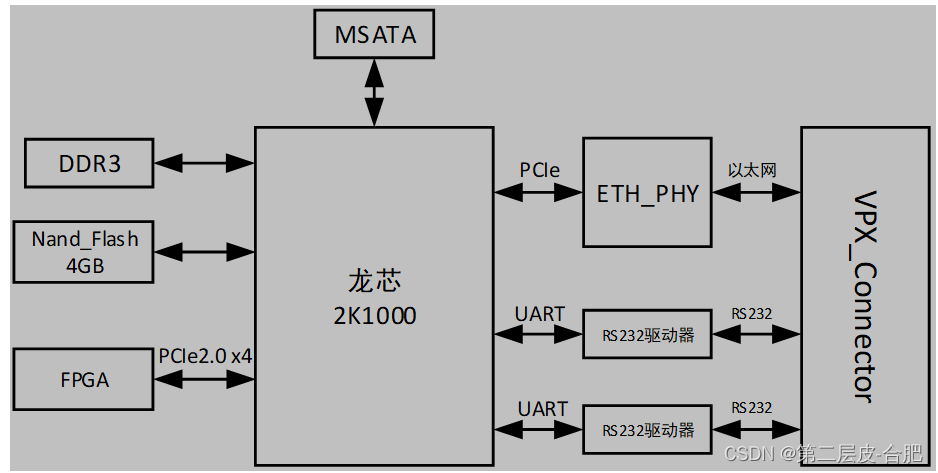

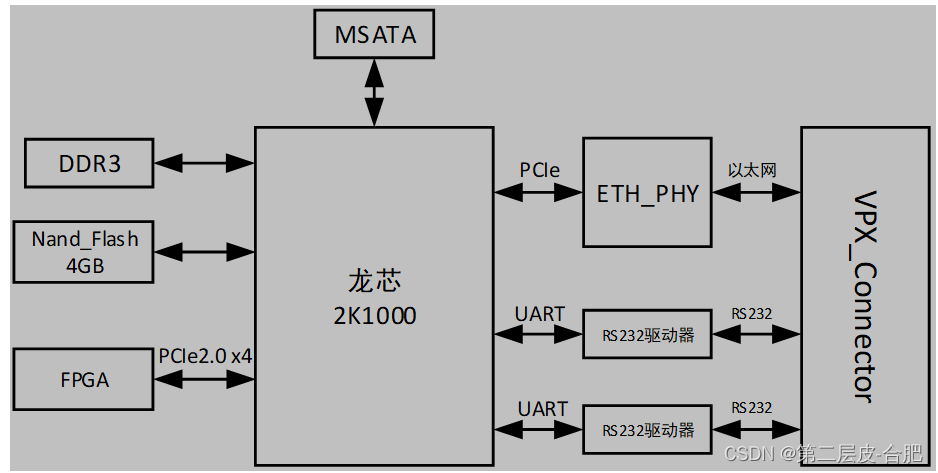

硬件采用龙芯CPU为核心,具体型号为2K1000,龙芯CPU外围挂载2GB大小的DDR3作为缓存、4GB的Nand_flash作为非易失的存储器、以及128GB的MSATA硬盘作为固态存储器。主要硬件框架如图 所示。

结构上基于6U VPX架构

本项目主要以龙芯2k1000为CPU实现整个系统的管理,主要实现数据交换、时间同步和数据监控等功能。项目中龙芯作为一部分存在,考虑到项目涉密的原因,不能将整个项目的应用背景及项目整体方案做介绍,只能将龙芯过程开发做一个分享总结。

硬件采用龙芯CPU为核心,具体型号为2K1000,龙芯CPU外围挂载2GB大小的DDR3作为缓存、4GB的Nand_flash作为非易失的存储器、以及128GB的MSATA硬盘作为固态存储器。主要硬件框架如图 所示。

结构上基于6U VPX架构

668

668

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?