龙芯2K1000处理器集成2个64位GS264处理器核,主频1GHz,以及各种系统IO接口,集高性能与高配置于一身。支持4G模块、GPS模块、千兆以太网、16GB固态硬盘、双路UART、四路USB、WIFI蓝牙二合一模块、MiniPCIE等接口、双路CAN总线、RS485总线,扩展能力更强。龙芯2K1000已经广泛应用于工控、轨道交通、电力、能源等领域,经过大量项目验证,是嵌入式领域一颗新星。拥有完全自主知识产权,供货稳定,也是龙芯中科面向嵌入式开发的主推产品。

【实验平台】:迅为龙芯2K1000开发板

【视频介绍】:成体系 | 龙芯教学视频

【内容来源】《iTOP龙芯2K1000开发指南》

【全套资料及网盘获取方式】联系淘宝客服加入售后技术支持群内下载

第二部分 龙芯2K1000简介

第二部分针对LS2K1000这款国产CPU进行一个初步的介绍,着重于LS2K1000芯片的特性,资源等以及对迅为基于这款CPU开发的迅为龙芯开发板进行介绍。

2.1初识龙芯2K1000

Kaifazengjia l 采用40nm工艺,片内集成2个GS264处理器核,主频1GHz,64位DDR3控制器,以及各种系统IO接口。

2.1.1龙芯2K1000主要特征

- 片内集成两个 64 位的双发射超标量 GS264 处理器核,主频 1GHz

- 片内集成共享的 1MB 二级 Cache

- 片内集成 GPU

- 片内显示控制器,支持双路 DVO 显示

- 片内集成 64 位 533MHz 的 DDR3 控制器

- 片内集成 2 个 x4 PCIE2.0 接口;可以拆分为 6 个独立 x1 接口

- 片内集成 1 个 SATA2.0 接口

- 片内集成 4 个 USB2.0 接口

- 片内集成 2 个 RGMII 千兆网接口

- 片内集成 HDA/I2S 接口

- 片内集成 RTC/HPET 模块

- 片内集成 12 个 UART 控制器

- 片内集成 1 个 NAND 控制器

- 片内集成 2 个 CAN 控制器

- 片内集成 1 个 SDIO 控制器

- 片内集成 2 个 I2C 控制器

- 片内集成 1 个 LIO 控制器

- 片内集成 1 个 VPU 解码器

- 片内集成 1 个 CAMERA 接口控制器

- 片内集成 1 个温度传感器

- 集成动态功耗控制模块

- 采用 FC-BGA 封装

2.1.2龙芯2K1000芯片特征

2.1.2.1 处理器核

- GS264

- MIPS64 R2 体系结构兼容

- 包括 1 个全流水的 64 位双精度浮点乘加部件

- 32KB 数据 Cache 和 32KB 的指令 Cache

- 1M 共享二级 Cache

- 通过目录协议维护 I/O DMA 访问的 Cache 一致性

- EJTAG 支持

2.1.2.2 GPU

- — 支持 OpenGL ES2.0, OpenGL ES 1.1

- —支持 OpenVG

- —通过 Futuremark 认证

- —动态电源管理

- —支持 BitBLT 和 Stretch BLT

- —矩形填充

- —硬件画线

- —单色字体渲染

- —ROP2, ROP3, ROP4

- —Alpha 混合

- —32Kx32K 坐标系统

- —90 度旋转

- —透明支持

- —YUV 色域空间转换

- —高质量缩放

2.1.2.3 显示控制器

- — 双 DVO 输出

- — 硬件光标

- — 伽玛校正

- — 输出抖动

- — 最高像素时钟(CRT 200MHz, DVO165MHz 1080p)

- — 支持线性显示缓冲

- 上电序列控制

- — 低功耗管理

2.1.2.4内存控制器

- — 64 位 DDR3 控制器,最高工作频率 533MHz

- — 不支持 ECC

- — 可配置为 32/16 位模式

- — 支持命令调度

2.1.2.5 SATA控制器

- — 1 个独立 SATA 端口

- — 支持 SATA 1.5Gbps 和 SATA2 代 3Gbps 的传输

- — 兼容串行 ATA 2.6 规范和 AHCI 1.1 规范

- — 低功耗设计

2.1.2.6 usb2.0控制器

- — 4 个独立的 USB2.0 的 HOST 端口

- — 其中端口 0 固定为 OTG 工作模式

- — 兼容 USB1.1 和 USB2.0

- — 内部 EHCI 控制和实现高速传输可达 480Mbps

- — 内部 OHCI 控制和实现全速和低速传输

- — 低功耗管理

2.1.2.7 GMAC控制器

- — 两路 10/100/1000Mbps 自适应以太网 MAC

- — 双网卡均兼容 IEEE 802.3

- — 对外部 PHY 实现 RGMII 接口

- — 半双工/全双工自适应

- — Timestamp 功能

- — 半双工时,支持碰撞检测与重发(CSMA/CD) 协议

- — 支持 CRC 校验码的自动生成与校验,支持前置符生成与删除

- — 支持网络开机

2.1.2.8 HDA控制器

- — 支持 16, 18 和 20 位采样精度支持可变速率

- — 最高达 192KHz

- — 7.1 频道环绕立体声输出

- — 三路音频输入

2.1.2.9 NAND控制器

- — 最大支持单片 16GB NAND Flash

- — 最大支持 4 个片选

- — 支持 MLC

- — 支持系统启动

- — 支持 512/2K/4K/8K 页

2.1.2.10 SPI控制器

- — 双缓冲接收器

- — 极性和相位可编程的串行时钟

- — 主模式支持

- — 支持到 4 个的变长字节传输

- — 支持系统启动

- — 支持标准读、连续地址读、快速读、 双路 I/O 等 SPI Flash 读模式

2.1.2.11 UART

- — 1 个全功能 UART 和流控 TXD,RXD,CTS, RTS, DSR,DTR,DCD, RI

- — 最大 12 个 UART 接口

- — 在寄存器与功能上兼容 NS16550A

- — 两路全双工异步数据接收/发送

- — 可编程的数据格式

- — 16 位可编程时钟计数器

- — 支持接收超时检测

- — 带仲裁的多中断系统

- — 可配置为 4 个两线串口(TXD/RXD)

2.1.2.12 I2C总线

- — 兼容 SMBUS(100Kbps)

- — 与 PHILIPS I2C 标准相兼容

- — 履行双向同步串行协议

- — 只实现主设备操作

- — 能够支持多主设备的总线

- — 总线的时钟频率可编程

- — 可以产生开始/停止/应答等操作

- — 能够对总线的状态进行探测

- — 支持低速和快速模式

- — 支持 7 位寻址和 10 位寻址

- — 支持时钟延伸和等待状态

2.1.2.13 PWM

- — 32 位计数器

- — 支持脉冲生成及捕获

- — 4 路控制器

2.1.2.14 HPET

- — 32 位计数器

- — 支持 1 个周期性中断

- — 支持 2 个非周期性中断

2.1.2.16 看门狗

- — 32 比特计数器及初始化寄存器

- — 低功耗模式暂停功能

2.1.2.15 RTC

- — 计时精确到 0.1 秒

- — 可产生 3 个计时中断

- — 支持定时开机功能

2.1.2.17 中断控制器

- — 支持软件设置中断

- — 支持电平与边沿触发

- — 支持中断屏蔽与使能

- — 支持固定中断均衡和智能中断均衡

2.1.2.18 ACPI功耗管理

- — 处理器核动态频率电压调节

- — 全芯片时钟门控

- — PHY 可关断

- — USB/GMAC 可唤醒

- — 来电可自动启动

2.1.2.19 PCIE接口

- — 兼容 PCIE 2.0

- — 双独立 X4 接口

- — 其中一路 X4 接口可以配置为 4 个 X1 接口

- — 其中一路 X4 接口可以配置为 2 个 X1 接口

2.1.2.20 I2S控制器

- — 支持 master 模式下 I2S 输入

- — 支持 master 模式下 I2S 输出

- — 支持 8、 16、 18、 20、 24、 32 位宽

- — 支持单声道和立体声道音频数据

- — 支持(16、 22.05、 32、 44.1、 48)kHz 采样频率

- — 支持 DMA 传输模式

2.1.2.21 CAN总线

- — 两路 CAN 接口

- — 复用 GPIO

2.1.2.22 加密模块

- — AES、 DES 算法支持

- — RSA 算法支持

2.1.2.23 SDIO控制器

- — 1 路独立 SDIO 控制器

- — 兼容 SD Memory 2.0/MMC/SDIO 2.0 协议

- — 支持 SDIO 启动

2.1.2.24 GPIO

- — 4 位专用 GPIO 引脚, 56 位复用 GPIO 引脚

- — 其余引脚与其他接口相复用,使用各个接口电压域

2.1.2.25 VPU解码器

- — 支持 H264

- — 支持 H263

- — 支持 SVC

- — 支持 MPEG-4

- — 支持 MPEG-2

- — 支持 MPEG-1

- — 支持 Sorenson Spark

- — 支持 JPEG

- — 支持 RV8、 RV9、 RV10

- — 支持 VP6.0、 VP6.1、 VP6.2

- — 支 持 DivX Home Theater Profile Qualified 、 DivX3 、 DivX4 、DivX5、 DivX6

2.1.2.26 CAMERA控制器

- — 兼容 ITU-R BT 601/656 8-bit 模式外部接口(支持同步信号产生的同步或是嵌入式同步)

- — 兼容 AMBA 2.0 AHB 接口

- — AMBA Interface word aligned memory transfer (32bit 宽度)

- — 使用内嵌的 DMA 方式进行存取数据操作

- — 8-bit 视 频 数 据 输 入 , 输 入 数 据 顺 序 固 定 , 为U01Y0V01Y1U23Y2V23Y3……(因为这是最为常用的 4: 2: 2 格式的数据顺序)

- — 独立于图片尺寸的水平和垂直的尺寸设置

- — 可编程水平、垂直同步信号极性

- — 3 个异步 FIFO,大小分别为 16×32bit(for Y) , 8×32bit(for U) ,8×32bit(for V)

2.1.3龙芯2K1000芯片分级

龙芯 2K1000 分有两个版本,不同版本芯片针对的工作环境、工作电压及实际功耗有所不同,不可相互替换。芯片在错误的工作电压下,可能会引起工作异常或使用寿命问题。在选用前必须明确对应的芯片分级。

不同版本的说明如下:

| 芯片标识 | 质量等级 | 典型电压 | 电源噪声 | 电流 | 最高环境温度 | 说明 |

| LS2K1000 | 商业级 | 1.2V | ±25mV | TBD | 65℃ | 工作频率 1.0GHz |

| LS2K1000-I | 工业级 | 1.1V | ±25mV | TBD | 85℃ | 工作频率 800MHz |

2.1.4龙芯2K1000引脚定义

2.1.4.1 DDR3接口

| 信号名称 | 类型 | 描述 | 电压 |

| DDR_DQ[63:0] | I/O | DDR3 SDRAM 数据总线信号 | 1V5/DDR |

| DDR_DQSp[7:0] DDR_DQSn[7:0] | DIFF I/O | DDR3 SDRAM 数据选通 | 1V5/DDR |

| DDR_DQM[7:0] | O | DDR3 SDRAM 数据屏蔽 | 1V5/DDR |

| DDR_A[15:0] | O | DDR3 SDRAM 地址总线信号 | 1V5/DDR |

| DDR_BA[2:0] | O | DDR3 SDRAM 逻辑 Bank 地址信号 | 1V5/DDR |

| DDR_WEn | O | DDR3 SDRAM 写使能信号 | 1V5/DDR |

| DDR_CASn | O | DDR3 SDRAM 列地址选择信号 | 1V5/DDR |

| DDR_RASn | O | DDR3 SDRAM 行地址选择信号 | 1V5/DDR |

| DDR_CSn[3:0] | O | DDR3 SDRAM 片选信号 | 1V5/DDR |

| DDR_CKE[3:0] | O | DDR3 SDRAM 时钟使能信号 | 1V5/DDR |

| DDR_CKp[7:0] DDR_CKn[7:0] | DIFF OUT | DDR3 SDRAM 差分时钟输出信号 | 1V5/DDR |

| DDR_ODT[3:0] | O | DDR3 SDRAM ODT 信号 | 1V5/DDR |

| DDR_RESETn | O | DDR3 SDRAM 复位控制信号 | 1V5/DDR |

| DDR_REXT | I/O | DDR3 SDRAM 参考电阻(外接 240 欧) | 1V5/DDR |

2.1.4.2 PCIE接口

| 信号名称 | 类型 | 描述 | 电压 |

| PCIE[1:0]_REFCLKp PCIE[1:0]_REFCLKn | DIFF IN | PCIE 参考时钟输入 | 1V1/PCIE |

| PCIE0_REFCLKp[3:0] PCIE0_REFCLKn[3:0] | DIFF OUT | PCIE0 参考时钟输出 | 1V1/PCIE |

| PCIE1_REFCLKp[1:0] PCIE1_REFCLKn[1:0] | DIFF OUT | PCIE1 参考时钟输出 | 1V1/PCIE |

| PCIE[1:0]_REFRES | A | 外部参考电阻,通过 200ohm(+/-1%)电阻连至地 | - |

| PCIE[1:0]_TXp[3:0] PCIE[1:0]_TXn[3:0] | DIFF OUT | PCIE 差分数据输出 | 1V1/PCIE |

| PCIE[1:0]_RXp[3:0] PCIE[1:0]_RXn[3:0] | DIFF IN | PCIE 差分数据输入 | 1V1/PCIE |

| PCIE0_PRSNT[3:0] | I | PCIE0 插卡检测 | 3V3/IO |

| PCIE1_PRSNT[1:0] | I | PCIE1 插卡检测 | 3V3/IO |

| PCIE_RSTn | O | PCIE 复位 | 3V3/IO |

2.1.4.3 DVO接口

| 信号名称 | 类型 | 描述 | 电压 |

| DVO[1:0]_CLKp | O | DVO 正向时钟输出 | 3V3/IO |

| DVO[1:0]_CLKn | O | DVO 反向时钟输出, 与 DVO*_CLKp 相差 180°, 非差分关系 | 3V3/IO |

| DVO[1:0]_HSYNC | O | DVO 水平同步 | 3V3/IO |

| DVO[1:0]_VSYNC | O | DVO 垂直同步 | 3V3/IO |

| DVO[1:0]_DE | O | DVO 数据有效 | 3V3/IO |

| DVO[1:0]_D[23:0] | O | DVO 显示数据 [23:16]为 R 数据 [15:08]为 G 数据 [07:00]为 B 数据 | 3V3/IO |

DVO 接口数据信号与 RGB 对应关系如下:

| DVO 接口信号 | 24 位模式 | 18 位模式 |

| DVO_D0 | B0 | |

| DVO_D1 | B1 | |

| DVO_D2 | B2 | B0 |

| DVO_D3 | B3 | B1 |

| DVO_D4 | B4 | B2 |

| DVO_D5 | B5 | B3 |

| DVO_D6 | B6 | B4 |

| DVO_D7 | B7 | B5 |

| DVO_D8 | G0 | |

| DVO_D9 | G1 | |

| DVO_D10 | G2 | G0 |

| DVO_D11 | G3 | G1 |

| DVO_D12 | G4 | G2 |

| DVO_D13 | G5 | G3 |

| DVO_D14 | G6 | G4 |

| DVO_D15 | G7 | G5 |

| DVO_D16 | R0 | |

| DVO_D17 | R1 | |

| DVO_D18 | R2 | R0 |

| DVO_D19 | R3 | R1 |

| DVO_D20 | R4 | R2 |

| DVO_D21 | R5 | R3 |

| DVO_D22 | R6 | R4 |

| DVO_D23 | R7 | R5 |

DVO0 接口与 LIO 以及 UART 有复用关系,如下表

| 信号名称 | 复用名称 | 复用类型 | 复用信号描述 | 电压 |

| DVO0_CLKp | LIO_WRn | O | LIO WRn 输出 | 3V3/IO |

| DVO0_CLKn | LIO_RDn | O | LIO RDn 输出 | 3V3/IO |

| DVO0_HSYNC | LIO_DEN | O | LIO DEN 输出 | 3V3/IO |

| DVO0_VSYNC | LIO_DIR | O | LIO DIR 输出 | 3V3/IO |

| DVO0_DE | LIO_ADLOCK | O | LIO ADLOCK 输出 | 3V3/IO |

| DVO0_D[15:0] | LIO_AD[15:0] | I/O | LIO 双向 AD 信号 | 3V3/IO |

| DVO0_D[22:16] | LIO_A[6:0] | O | LIO 地址低位 | 3V3/IO |

| DVO0_D23 | LIO_CSn | O | LIO 片选信号 | 3V3/IO |

| 信号名称 | 复用名称 | 复用类型 | 复用信号描述 | 电压 |

| DVO0_HSYNC | UART1_TXD | O | 串口数据输出 | 3V3/IO |

| DVO0_VSYNC | UART1_RXD | I | 串口数据输入 | 3V3/IO |

| DVO0_DE | UART1_RTS | O | 串口数据传输请求 | 3V3/IO |

| DVO0_D00 | UART1_DTR | O | 串口初始化完成 | 3V3/IO |

| DVO0_D01 | UART1_RI | I | 外部 MODEM 探测到振铃信号 | 3V3/IO |

| DVO0_D02 | UART1_CTS | I | 设备接受数据就绪 | 3V3/IO |

| DVO0_D03 | UART1_DSR | I | 设备初始化完成 | 3V3/IO |

| DVO0_D04 | UART1_DCD | I | 外部 MODEM 探测到载波信号 | 3V3/IO |

| DVO0_D05 | UART2_TXD | O | 串口数据输出 | 3V3/IO |

| DVO0_D06 | UART2_RXD | I | 串口数据输入 | 3V3/IO |

| DVO0_D07 | UART2_RTS | O | 串口数据传输请求 | 3V3/IO |

| DVO0_D08 | UART2_DTR | O | 串口初始化完成 | 3V3/IO |

| DVO0_D09 | UART2_RI | I | 外部 MODEM 探测到振铃信号 | 3V3/IO |

| DVO0_D11 | UART2_CTS | I | 设备接受数据就绪 | 3V3/IO |

| DVO0_D12 | UART2_DSR | I | 设备初始化完成 | 3V3/IO |

| DVO0_D13 | UART2_DCD | I | 外部 MODEM 探测到载波信号 | 3V3/IO |

DVO1 接口与 CAMERA 接口有复用关系,参考和 2.4.8 节。

2.1.4.4 GMAC接口

| 信号名称 | 类型 | 描述 | 电压 |

| GMAC[1:0]_TXCK | O | RGMII 发送时钟 | 2V5/3V3/GMAC |

| GMAC[1:0]_TCTL | O | RGMII 发送控制 | 2V5/3V3/GMAC |

| GMAC[1:0]_TXD[3:0] | O | RGMII 发送数据 | 2V5/3V3/GMAC |

| GMAC[1:0]_RXCK | I | RGMII 接收时钟 | 2V5/3V3/GMAC |

| GMAC[1:0]_RCTL | I | RGMII 接收控制 | 2V5/3V3/GMAC |

| GMAC[1:0]_RXD[3:0] | I | RGMII 接收数据 | 2V5/3V3/GMAC |

| GMAC[1:0]_MDCK | O | SMA 接口时钟, 需外接上拉 | 2V5/3V3/GMAC |

| GMAC[1:0]_MDIO | I/O | SMA 接口数据, 需外接上拉 | 2V5/3V3/GMAC |

GMAC1 接口与 GPIO 有复用关系,如下表所示:

| 信号名称 | 复用名称 | 复用类型 | 复用信号描述 | 电压 |

| GMAC1_TXCK | - | - | - | - |

| GMAC1_TCTL | GPIO13 | I/O | 通用输入输出 13 | 2V5/3V3/GMAC |

| GMAC1_TXD[3:0] | GPIO[12:9] | I/O | 通用输入输出 12-9 | 2V5/3V3/GMAC |

| GMAC1_RXCK | - | - | - | - |

| GMAC1_RCTL | GPIO8 | I/O | 通用输入输出 8 | 2V5/3V3/GMAC |

| GMAC1_RXD[3:0] | GPIO[7:4] | I/O | 通用输入输出 7-4 | 2V5/3V3/GMAC |

| GMAC1_MDCK | - | - | - | - |

| GMAC1_MDIO | - | - | - |

2.1.4.5 SATA接口

| 信号名称 | 类型 | 描述 | 电压 |

| SATA_REFCLKp SATA_REFCLKn | 差分 100MHz 参考时钟输入(内部有备份时钟,通过软件选择) | 1V1/SATA | |

| SATA_REFRES | A | 外部参考电阻,通过 200ohm(+/-1%)电阻连至地 | - |

| SATA_TXp SATA_TXn | DIFF OUT | SATA 差分数据输出 | 1V1/SATA |

| SATA_RXp SATA_RXn | DIFF IN | SATA 差分数据输入 | 1V1/SATA |

| SATA_LEDn | O | SATA 工作状态,低表示有数据传输 | 3V3/IO |

SATA 接口的 SATA_LEDn 与 GPIO 有复用关系,如下表所示:

| 信号名称 | 复用名称 | 复用类型 | 复用信号描述 | 电压 |

| SATA_LEDn | GPIO14 | I/O | 通用输入输出 14 | 3V3/IO |

2.1.4.6 USB接口

| 信号名称 | 类型 | 描述 | 电压 | |

| USB_XI USB_XO | I/O | 必须在 USB_XO 上接晶振, USB_XI保留不用 | A3V3/USB | |

| USB[3:0]_TXRTUNE | A | 参考电阻,通过 200ohm/1%电阻连接到地 | A3V3/USB | |

| USB[3:0]_DP | I/O | USB D+, 通过 15K 电阻下拉到地 | A3V3/USB | |

| USB[3:0]_DM | I/O | USB D-, 通过 15K 电阻下拉到地 | A3V3/USB | |

| USB0_ID | I | USB0 OTG ID 输入 | A3V3/USB | |

| USB0_VBUS | A | USB0 OTG VBUS 输入 | 5V | |

| USB[3:1]_OC | I | USB 过流检测输入,需注意该信号为高有效 | 3V3/RSM | |

| USB0_OC | O | OTG DRVVBUS 输出 | 3V3/RSM | |

2.1.4.7 HDA接口

| 信号名称 | 类型 | 描述 | 电压 |

| HDA_BITCLK | O | HDA BITCLK 输出 | 3V3/IO |

| HDA_SDI0 | I | HDA 数据输入,连接第一个 codec | 3V3/IO |

| HDA_SDI1 | I | HDA 数据输入,连接第二个 codec | 3V3/IO |

| HDA_SDI2 | I | HDA 数据输入,连接第三个 codec | 3V3/IO |

| HDA_SDO | O | HDA 数据输出 | 3V3/IO |

| HDA_SYNC | O | HDA 同步 | 3V3/IO |

| HDA_RESETn | O | HDA 复位 | 3V3/IO |

HDA 接口与 I2S 以及 GPIO 复用,具体复用关系如下:

HDA 与 I2S 复用关系

| 信号名称 | 复用名称 | 复用类型 | 复用信号描述 | 电压 |

| HDA_BITCLK | I2S_BCLK | I | I2S bit 时钟 | 3V3/IO |

| HDA_SDI0 | I2S_DI | I | I2S 数据输入 | 3V3/IO |

| HDA_SDI1 | - | - | - | 3V3/IO |

| HDA_SDI2 | - | - | - | 3V3/IO |

| HDA_SDO | I2S_DO | O | I2S 数据输出 | 3V3/IO |

| HDA_SYNC | I2S_MCLK | O | I2S MCLK | 3V3/IO |

| HDA_RESETn | I2S_LR | O | I2S 左右声道选择 | 3V3/IO |

HDA 与 GPIO 复用关系

| 信号名称 | 复用名称 | 复用类型 | 复用信号描述 | 电压 |

| HDA_BITCLK | GPIO24 | I/O | 通用输入输出 24 | 3V3/IO |

| HDA_SDI0 | GPIO28 | I/O | 通用输入输出 28 | 3V3/IO |

| HDA_SDI1 | GPIO29 | I/O | 通用输入输出 29 | 3V3/IO |

| HDA_SDI2 | GPIO30 | I/O | 通用输入输出 30 | 3V3/IO |

| HDA_SDO | GPIO27 | I/O | 通用输入输出 27 | 3V3/IO |

| HDA_SYNC | GPIO25 | I/O | 通用输入输出 25 | 3V3/IO |

| HDA_RESETn | GPIO26 | I/O | 通用输入输出 26 | 3V3/IO |

2.1.4.8 CAMERA接口

| 信号名称 | 类型 | 描述 |

| CAM_PCLK | I | 像素时钟,被摄像头的处理器驱动 |

| CAM_HSYNC | I | 水平同步,被摄像头的处理器驱动 |

| CAM_VSYNC | I | 帧同步,被摄像头的处理器驱动 |

| CAM_DATA[7:0] | I | 像素数据,被摄像头的处理器驱动 |

| CAM_CLOCK | O | XCLK 被摄像头控制器驱动,用于摄像头模块 |

注意:控制信号都是单向的,只支持 camera 提供时钟和同步信号的模式

CAMERA 与 DVO1 复用关系

| 信号名称 | 复用名称 | 复用类型 | 复用信号描述 |

| AM_PCLK | DVO1_CKN | I | DVO1 负时钟输出 |

| AM_HSYNC | DVO1_HSYNC | I | DVO1 水平同步信号 |

| AM_VSYNC | DVO1_VSYNC | I | DVO1 垂直同步信号 |

| AM_DATA[7:0] | DVO1_D[7:0] | I | DOV1 数据输出信号 |

| AM_CLOCK | DVO1_CKP | O | DVO1 正时钟输出 |

2.1.4.9 SPI接口

| 信号名称 | 类型 | 描述 | 电压 |

| SPI_SCK | O | SPI 时钟输出 | 3V3/IO |

| SPI_CSn0 | O | SPI 片选 0 | 3V3/IO |

| SPI_CSn1 | O | SPI 片选 1 | 3V3/IO |

| SPI_CSn2 | O | SPI 片选 2 | 3V3/IO |

| SPI_CSn3 | O | SPI 片选 3 | 3V3/IO |

| SPI_SDO | O | SPI 数据输出 | 3V3/IO |

| SPI_SDI | I | SPI 数据输入 | 3V3/IO |

2.1.4.10 IIC接口

| 信号名称 | 类型 | 描述 | 电压 |

| I2C0_SCL | O | I2C0 时钟 | 3V3/IO |

| I2C0_SDA | I/O | I2C0 数据 | 3V3/IO |

| I2C1_SCL | O | I2C1 时钟 | 3V3/IO |

| I2C1_SDA | I/O | I2C1 数据 | 3V3/IO |

I2C 与 GPIO 有复用,复用关系见下表:

I2C 与 GPIO 复用关系

| 信号名称 | 复用名称 | 复用类型 | 复用信号描述 | 电压 |

| I2C0_SCL | GPIO16 | I/O | 通用输入输出 16 | 3V3/IO |

| I2C0_SDA | GPIO17 | I/O | 通用输入输出 17 | 3V3/IO |

| I2C1_SCL | GPIO18 | I/O | 通用输入输出 18 | 3V3/IO |

| I2C1_SDA | GPIO19 | I/O | 通用输入输出 19 | 3V3/IO |

2.1.4.11 UART接口

| 信号名称 | 类型 | 描述 | 电压 |

| UART_TXD | O | 串口数据输出 | 3V3/IO |

| UART_RXD | I | 串口数据输入 | 3V3/IO |

| UART_RTS | O | 串口数据传输请求 | 3V3/IO |

| UART_DTR | O | 串口初始化完成 | 3V3/IO |

| UART_RI | I | 外部 MODEM 探测到振铃信号 | 3V3/IO |

| UART_CTS | I | 设备接受数据就绪 | 3V3/IO |

| UART_DSR | I | 设备初始化完成 | 3V3/IO |

| UART_DCD | I | 外部 MODEM 探测到载波信号 | 3V3/IO |

2K1000 仅有一个独立的全功能串口,该串口通过设置可以工作在 2x4 和 4x2 模式,各种模式的管脚对应关系如下。其它引脚复用的 UART 接口的内部复用关系也如下表所示。

接口复用关系

| 1x8 | 2x4 | 4x2 |

| TXD0(O) | TXD0(O) | TXD0(O) |

| RTS0(O) | RTS0(O) | TXD5(O) |

| DTR0(O) | TXD3(O) | TXD3(O) |

| RXD0(I) | RXD0(I) | RXD0(I) |

| CTS0(I) | CTS0(I) | RXD5(I) |

| DSR0(I) | RXD3(I) | RXD3(I) |

| DCD0(I) | CTS3(I) | RXD4(I) |

| RI0(I) | RTS3(O) | TXD4(O) |

2.1.4.12 NAND接口

| 信号名称 | 类型 | 描述 | 电压 |

| NAND_CEn[3:0] | O | NAND 片选 3-0 | 3V3/IO |

| NAND_CLE | O | NAND 命令锁存 | 3V3/IO |

| NAND_ALE | I | NAND 地址锁存 | 3V3/IO |

| NAND_WRn | O | NAND 写信号 | 3V3/IO |

| NAND_RDn | I | NAND 读信号 | 3V3/IO |

| NAND_RDYn[3:0] | I | NAND 准备好输入 3-0,需要外接4.7k 上拉电阻 | 3V3/IO |

| NAND_D[7:0] | I/O | NAND 命令/地址/数据线 | 3V3/IO |

NAND 与 GPIO 有复用,复用关系见下表:

NAND 与 GPIO 复用关系

| 信号名称 | 复用名称 | 复用类型 | 复用信号描述 | 电压 |

| NAND_CEn[3:0] | GPIO[47:44] | I/O | 通用输入输出 47-44 | 3V3/IO |

| NAND_CLE | GPIO48 | I/O | 通用输入输出 48 | 3V3/IO |

| NAND_ALE | GPIO49 | I/O | 通用输入输出 49 | 3V3/IO |

| NAND_WRn | GPIO50 | I/O | 通用输入输出 50 | 3V3/IO |

| NAND_RDn | GPIO51 | I/O | 通用输入输出 51 | 3V3/IO |

| NAND_RDYn[3:0] | GPIO[55:52] | I/O | 通用输入输出 55-52 | 3V3/IO |

| NAND_D[7:0] | GPIO[63:56] | I/O | 通用输入输出 63-56 | 3V3/IO |

2.1.4.13 CAN接口

| 信号名称 | 类型 | 描述 | 电压 |

| CAN0_RX | I | CAN 通道 0 数据接收 | 3V3/IO |

| CAN0_TX | O | CAN 通道 0 数据发送 | 3V3/IO |

| CAN1_RX | I | CAN 通道 1 数据接收 | 3V3/IO |

| CAN1_TX | O | CAN 通道 1 数据发送 | 3V3/IO |

CAN 接口与 GPIO 有复用, 如下表所示:

CAN 与 GPIO 复用关系

| 信号名称 | 复用名称 | 复用类型 | 复用信号描述 | 电压 |

| CAN0_RX | GPIO32 | I/O | 通用输入输出 32 | 3V3/IO |

| CAN0_TX | GPIO33 | I/O | 通用输入输出 33 | 3V3/IO |

| CAN1_RX | GPIO34 | I/O | 通用输入输出 34 | 3V3/IO |

| CAN1_TX | GPIO35 | I/O | 通用输入输出 35 | 3V3/IO |

2.1.4.14 SDIO接口

| 信号名称 | 类型 | 描述 | 电压 |

| SDIO_CLK | O | SDIO 时钟输出 | 3V3/IO |

| SDIO_CMD | I/O | SDIO 命令输入输出 | 3V3/IO |

| SDIO_DATA[3:0] | I/O | SDIO 数据信号 | 3V3/IO |

SDIO 与 GPIO 有复用, 复用关系见下表:

SDIO 与 GPIO 复用关

| 信号名称 | 复用名称 | 复用类型 | 复用信号描述 | 电压 |

| SDIO_CLK | GPIO41 | I/O | 通用输入输出 41 | 3V3/IO |

| SDIO_CMD | GPIO40 | I/O | 通用输入输出 40 | 3V3/IO |

| SDIO_DATA[3:0] | GPIO[36:39] | I/O | 通用输入输出 36-39 | 3V3/IO |

2.1.4.15 PWM接口

| 信号名称 | 类型 | 描述 | 电压 |

| PWM[3:0] | O | PWM 输出 | 3V3/IO |

PWM 与 GPIO 有复用,复用关系如下:

PWM 与 GPIO 复用关系

| 信号名称 | 复用名称 | 复用类型 | 复用信号描述 | 电压 |

| PWM[3:0] | GPIO[23:20] | I/O | 通用输入输出 23-20 | 3V3/I |

2.1.4.16 GPIO接口

下表仅列出专用的 4 个 GPIO 引脚信号,其他 GPIO 为复用信号,可参考其他信号定义。 默认情况下所有与 GPIO 复用的引脚为 GPIO 功能,且都为输入状态。

| 信号名称 | 类型 | 描述 | 电压 |

| GPIO00 | I/O | 通用输入输出 | 3V3/IO |

| GPIO01 | I/O | 通用输入输出 | 3V3/IO |

| GPIO02 | I/O | 通用输入输出 | 3V3/IO |

| GPIO03 | I/O | 通用输入输出 | 3V3/IO |

2.1.4.17 PLL电源接口

| 信号名称 | 类型 | 描述 | 电压 |

| PLL_CORE_VDD | P | CORE PLL 电源 | 1V1/IO |

| PLL_SOC_VDD | P | SOC PLL 电源 | 1V1/IO |

| PLL_DDR_VDD | P | DDR PLL 电源 | 1V1/IO |

| PLL_PIX0_VDD | P | PIXEL0 PLL 电源 | 1V1/IO |

| PLL_PIX1_VDD | P | PIXEL1 PLL 电源 | 1V1/IO |

| PLL_CORE_VSS | P | CORE PLL 地 | 0V/IO |

| PLL_SOC_VSS | P | SOC PLL 地 | 0V/IO |

| PLL_DDR_VSS | P | DDR PLL 地 | 0V/IO |

| PLL_PIX0_VSS | P | PIXEL0 PLL 地 | 0V/IO |

| PLL_PIX1_VSS | P | PIXEL1 PLL 地 | 0V/IO |

2.1.4.18 电源管理接口

| 信号名称 | 类型 | 描述 | 电压 |

| ACPI_SYSRSTn | I | 系统复位 | 3V3/RSM |

| ACPI_RINGn | I | 振铃唤醒 | 3V3/RSM |

| ACPI_WAKEn | I | PCIE 唤醒 | 3V3/RSM |

| ACPI_LID | I | 屏盖状态 | 3V3/RSM |

| ACPI_PWRTYPE | I | 供电来源 | 3V3/RSM |

| ACPI_BATLOWn | I | 电源电量低 | 3V3/RSM |

| ACPI_SUSSTATn | O | 低功耗状态 | 3V3/RSM |

| ACPI_S3n | O | S3 状态 | 3V3/RSM |

| ACPI_S4n | O | S4 状态 | 3V3/RSM |

| ACPI_S5n | O | S5 状态 | 3V3/RSM |

| ACPI_VID[5:0] | O | 调压控制 | 3V3/RSM |

| ACPI_PLTRSTn | O | 平台复位 | 3V3/RSM |

| ACPI_SLPLANn | O | 网络电源控制 | 3V3/RSM |

| ACPI_PWRBTNn | I | 电源开关 | 3V3/RSM |

| ACPI_PWROK | I | 电源有效 | 3V3/RSM |

2.1.4.19 EJTAG接口

| 信号名称 | 类型 | 描述 | 电压 |

| EJTAG_SEL | I | JTAG 选择(1: JTAG; 0: EJTAG) | 3V3/IO |

| EJTAG_TCK | I | JTAG 时钟 | 3V3/IO |

| EJTAG_TDI | I | JTAG 数据输入 | 3V3/IO |

| EJTAG_TMS | I | JTAG 模式 | 3V3/IO |

| EJTAG_TRST | I | JTAG 复位 | 3V3/IO |

| EJTAG_TDO | O | JTAG 数据输出 | 3V3/I |

2.1.4.20 测试接口

| 信号名称 | 类型 | 描述 | 电压 |

| ACPI_DOTESTn | I | 测试模式控制(RTC 电压域) 0: 测试模式 1: 功能模式 | 2V5/RTC |

2.1.4.21 时钟配置信号

| 信号名称 | 类型 | 描述 | 电压 |

| SYS_SYSCLK | I | 100MHz 参考时钟 | 3V3/IO |

| SYS_TESTCLK | I | 测试时钟输入,默认不用连接 | 3V3/IO |

2.1.4.22 系统相关信号

| 信号名称 | 类型 | 描述 | 电压 |

| SYS_CLKSEL[1:0] | I | PLL 时钟配置输入000=低频模式,01=高频模式,10=软件模式(DFT),11=bypass 模式 | 3V3/IO |

| SYS_BOOTSEL[1:0] | I | 启动选择输入 00=LIO,01=SPI(DFT),10=SDIO,11=NAND | 3V3/IO |

| SYS_USBCLKMODE[1:0] | I | USB 时钟输入配置输入 10=one 12MHz clock input 11=use sysclk(DFT) | 3V3/IO |

| SYS_PCIECLKSEL | I | PCIE 参考时钟选择输入 0=内部(DFT),1=PAD 输入 | 3V3/IO |

| SYS_PCIECLKDIV | I | PCIE 参考时钟频率输入 0=100MHz(DFT),1=200MHz | 3V3/IO |

| SYS_NANDRSRD | I | NAND ECC 功能使能输入 1=enable,0=disable(DFT) | 3V3/IO |

| SYS_NANDTYPE[1:0] | I | 启动 NAND 类型选择 00=512Mb(page 512B) 01=1Gb(page 2KB) 10=16Gb(page 4KB) 11=128Gb(page 8KB) | 3V3/IO |

2.1.4.23 RTC相关信号

| 信号名称 | 类型 | 描述 | 电压 |

| RTC_RSMRSTn | I | RSM 域复位,要求在 RSM 域电源稳定 1ms 后拉高,在RSM 域电源降至 95%及以下时立即拉低。 | 2V5/RTC |

| RTC_RSTn | I | RTC 域复位,建议在 RTC 电源稳定 10ms 后再解除复位。 | 2V5/RTC |

| RTC_XI | I/O | 32.768KHz 晶体输入 | 2V5/RTC |

| RTC_XO | I/O | 32.768KHz 晶体输出 | 2V5/RTC |

| 信号名称 | 类型 | 描述 | 电压 |

| VSS | P | 数字地 | 0 |

| VDD | P | 数字电源 | 1.1V |

| ACPI_3V3 | P | ACPI 模拟电源 | 3.3V |

| DDR_VDDE | P | DDR 模拟电源 | 1.5V |

| DDR_VREF | P | DDR 数字电源 | 0.75V |

| GMAC_VDDE | P | GMAC 数字电源 | 2.5V/3.3V |

| IO_3V3 | P | IO 电源 | 3.3V |

| PEST_1V1 | P | PEST 电源 | 1.1V |

| PEST_3V3 | P | PEST 电源 | 3.3V |

| RTC_2V5 | P | RTC 域电源 | 2.5V |

| USB_A3V3 | P | USB 模拟电源 | 3.3V |

| VDD_RSM | p | RSM 域 RGMII 接口电源 | 1.1V |

| NC_EFUSE_AVDD | P | NC_EFUSE 模拟电源 |

2.1.4.24 外设功能复位表

模块层次的功能复用关系如下表所示

| 功能 0 | 功能 1 | 功能 2 | 功能 3 | 功能 4 | 功能 5 |

| DDR3 | |||||

| PCIE | |||||

| SATA | GPIO(1) | ||||

| USB | |||||

| GMAC0 | |||||

| GMAC1 | GPIO(14) | ||||

| DVO0 | Local Bus | UART1(8) | UART1(4) | UART1(2) | |

| UART8(2) | |||||

| UART6(4) | UART6(2) | ||||

| UART7(2) | |||||

| UART2(8) | UART2(4) | UART2(2) | |||

| UART11(2) | |||||

| UART9(4) | UART9(2) | ||||

| UART10(2) | |||||

| DVO1 | CAMERA | ||||

| CAN | GPIO(4) | ||||

| HDA | GPIO(7) | I2S | |||

| SPI | |||||

| RTC | |||||

| I2C | GPIO(4) | ||||

| UART0(8) | UART0(4) | UART0(2) | |||

| UART5(2) |

2.1.5龙芯2K1000不使用引脚的处理

当我们在自行设计底板时,核心板上有的引脚并一定会用到,不使用的引脚最好按照以下原则处理:

| 信号组 | 不使用的处理方式 |

| DDR3 | DDR 32/16 位模式只用低 32/16 位数据线,不用的信号需拉低。 |

| PCIE | 输出可悬空,输入需拉低 |

| DVO | 可悬空 |

| GMAC | 输出可悬空,输入需拉低 |

| SATA | 输出可悬空,输入需拉低 |

| USB | 需拉低 |

| HDA | 输出可悬空,输入需拉低 |

| SPI | 输出可悬空,输入需拉低, 配置引脚必须正确上下拉 |

| I2C | 需拉低 |

| UART | 输出可悬空,输入需拉低 |

| NAND | 配置引脚必须正确上下拉 |

| GPIO | 由软件设置为输出则可悬空 |

| ACPI | ACPI_SYSRSTn 作系统复位, ACPI_DOTESTn 上拉, ACPI_RSMRSTn 上拉, 其它信号输出可悬空,输入需拉低 |

| EJTAG | EJTAG_TRST/TDI 需下拉,其它信号可悬空 |

| 时钟配置 | 必须正确连接 |

| 电源地 | 电源地不可悬空 PCIE和SATA均不使用时,相关电源可接地 其它电源地必须正确连接 |

2.2迅为龙芯开发板简介

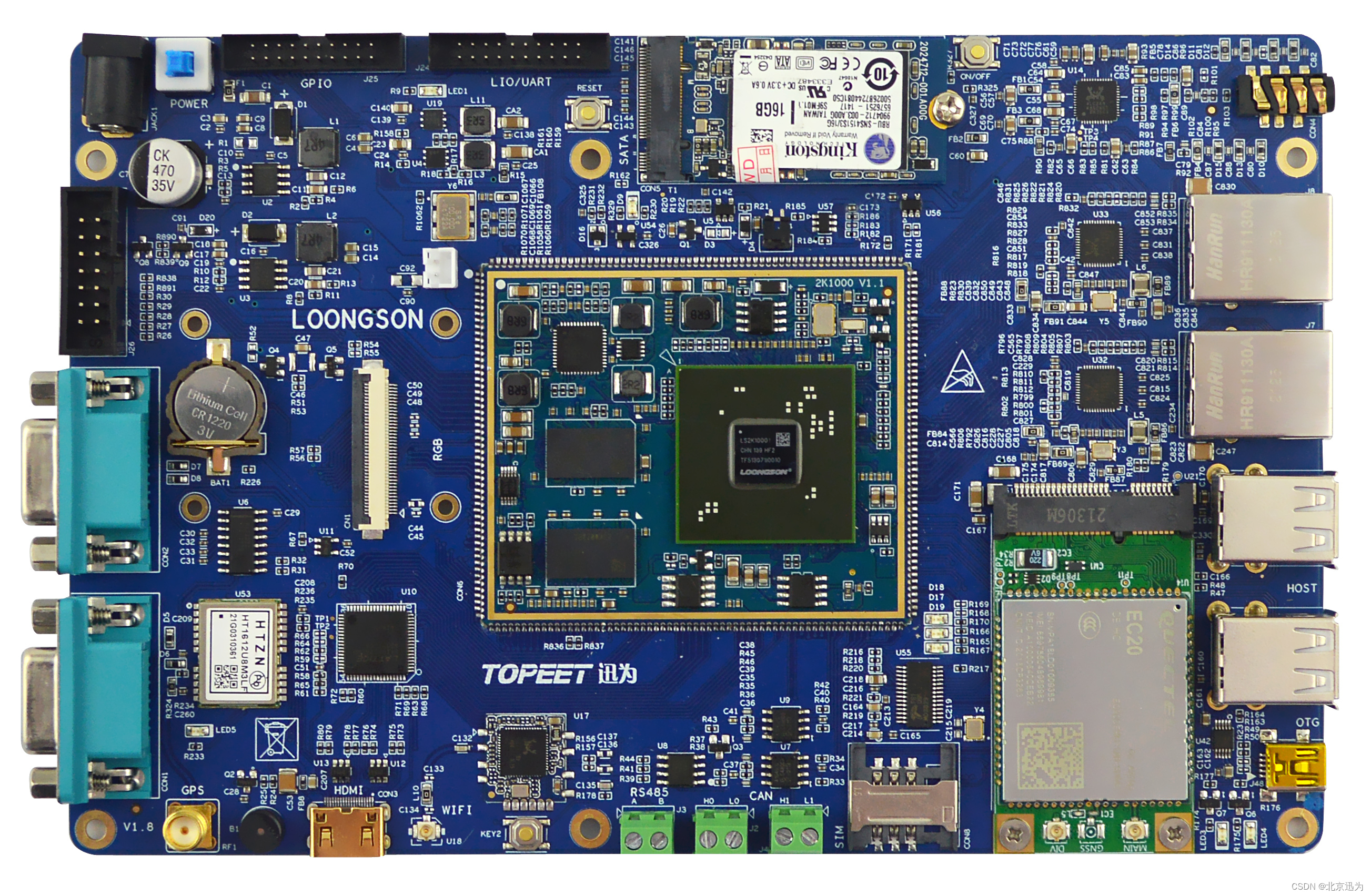

2.2.1 LS2K1000开发板

迅为龙芯开发板是北京迅为电子推出的一款基于国产CPU龙芯2K1000开发板。采用核心板+底板的方式,

如下图所示:

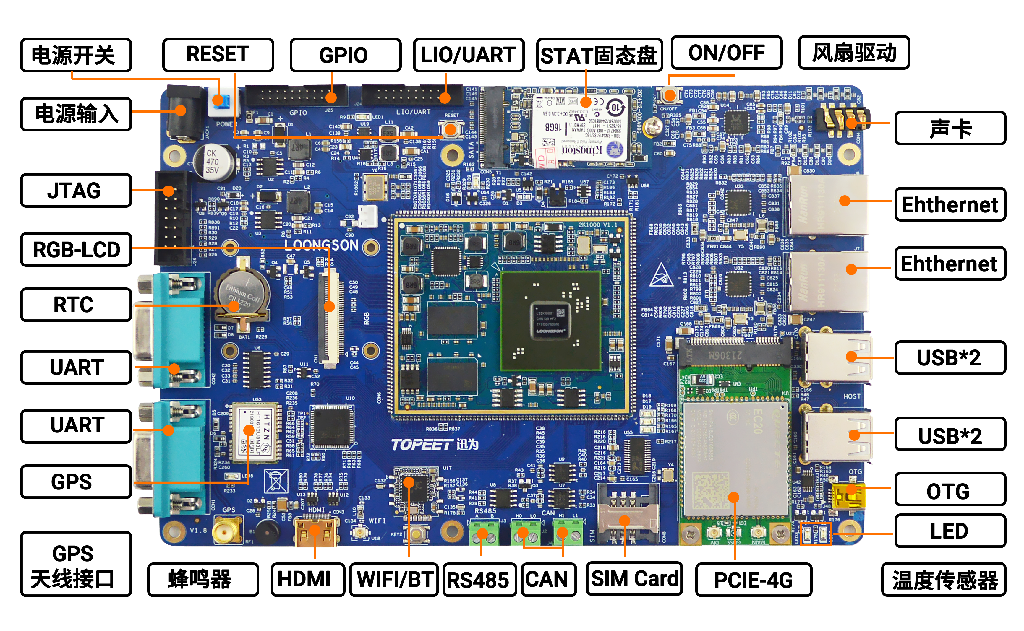

2.2.2 LS2K1000底板资源介绍

迅为龙芯LS2K1000开发板硬件资源非常丰富, 几乎将芯片的所有资源都扩展引出到底板上了,底板提供了丰富的外设接口, 并充分考虑了人性化设计, 整体显得十分高端大气。迅为龙芯开发板不光是一个开发平台,更是一个小型迷你计算机,我们可以跟方便的在上面进行开发学习,甚至是直接编译程序。

迅为龙芯LS2K1000开发板底板板载资源如下:

1.邮票孔核心板接口, 支持北京迅为电子的龙芯LS2K1000核心板。

2.一个电源指示灯

3.倆个用户指示灯

4.板载 Wifi/蓝牙二合一模块

5.四路 USB HOST 接口

6.板载 Mini PCIE 4G 模块接口

7.一路 RS485 接口

10.两路 CAN 接口

11.一个用户按键

12. 一个有源蜂鸣器

13. 两路 10M/100M/1000M自适应以太网

14. 标准3.5mm耳机接口

15. 一路 RGB 屏幕接口

16. 一路标准 HDMI 接口

17. 一路 JTARG 调试接口

18. 一路GPS

19. 一路固态硬盘接口

20.俩组扩展接口

21.一个开关机按键

22.两路232接口

23.一路RTC

24.一路复位按键

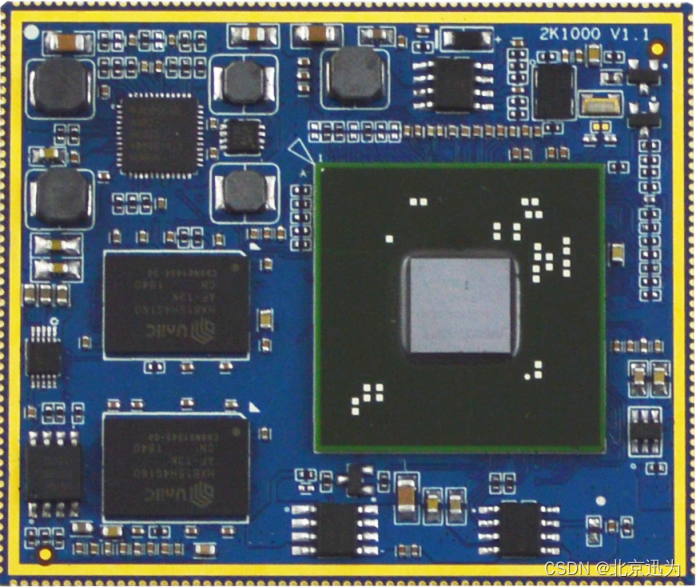

2.2.3 LS2K1000核心板

迅为电子的LS2K1000核心板对外提供的接口是邮票孔方式。 下面我介绍下这款核心板的硬件参数:

LS2K1000工业级核心板的实物图片如下图所示:

核心板正面:

核心板背面:

2.2.4 LS2K1000核心板资源介绍

LS2K1000工业级核心板板载资源如下:

1. CPU: LS2K1000工业级/商业级 主频为800/1GMHz, 采用FC-BGA 封装

2. DDR3: 采用国产紫光工业级ddr,每片大小为512MB。核心板一共4片,内存为2G

3. NAND FLASH:可选。最大支持单片 16GB NAND Flash

4.采用1.0mm间距的邮票孔方式引出232个引脚

1224

1224

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?