目录

简介:

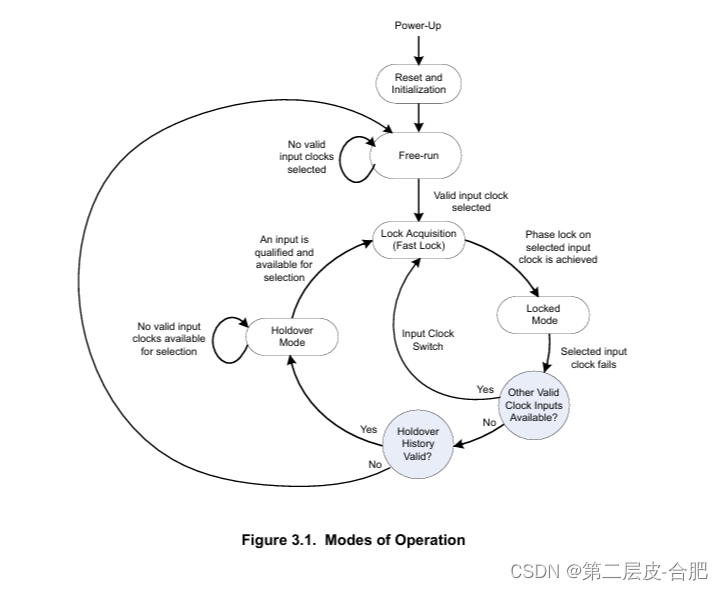

最近在时钟同步分析种,疑问是恢复时钟怎么和参考时钟的切换?从而又设计到一系列时钟方面的知识,本文主要解释时钟锁定的几个模式,并介绍他们的作用。

模式介绍:

freerun:自由震荡状态;

locked:锁定状态;

holdover:保持状态;

lost:信号丢失状态;

详细介绍:

holdover:在实际的应用当中,给时钟芯片提供的参考时钟可能由于各种原因出现偏移或者丢失,从而导致 时钟芯片失锁,使得输出的时钟误差比较大,进而导致整个板卡误码甚至系统的紊乱。为了避免这个 问题的出现,系统要求时钟芯片即便在参考丢失或者出现比较大的偏移时,仍然能够输出一个比较稳 定的时钟。

本项目种就是一个例子。需要切换时钟。那就需要PLL支持holdover模式,此模式也叫无缝切换。

当锁相环锁定的时候,锁相环的鉴相器输出电压控制VCXO的振荡频率;同时holdover电路会跟 踪记录鉴相器输出的压控电压,同时实时更新 holdover 电路的输出,使其等于鉴相器输出的压控电 压;当 CLKin 参考丢失时,锁相环的锁定指示检测到锁相环失锁,VCXO 的压控电压会切换到 holdover 电路的输出电压,同时 holdover 电路不再跟踪鉴相器的的压控电压,从而实现了输出频率 的稳定;当CLKin恢复时,芯片不会立即切换到鉴相器输出的电压,而是等到VCXO N分频之后输 出的频率(Nout)和 CLKin R 分频之后的频率(Rout)相位误差连续多次小于特定的误差范围,才 会退出holdover 并切换到鉴相器的输出,从而保证芯片退出holdover 并重新进入跟踪、锁定过程也 不会产生时钟的跳变。

其他几个状态就不需要再细讲了,可以看下图,简单介绍下:

freerun:一旦设备通电并完成初始化,DSPLL 将自动进入自由运行模式。在自由运行模式下,生成的输出时钟的频率精度完全取决于外部晶振或XA/XB引脚上的参考时钟的频率精度。例如,如果晶体频率为 ±100 ppm,则在自由运行模式下,所有输出时钟都将在其配置频率 ±100 ppm 下生成。晶振频率的任何漂移都将在输出时钟频率下进行跟踪。TCXO 或 OCXO 推荐用于在自由运行或保持模式下需要更高频率精度和稳定性的应用

锁定采集模式:

锁定采集模式该器件监控所有输入的有效时钟。如果至少有一个有效的时钟可用于同步,DSPLL 将自动启动锁采集过程。如果启用了快速锁定功能,DSPLL 将使用快速锁定环路带宽设置获取锁,然后在锁获取完成后转换到 DSPLL 环路带宽设置。在锁采集期间,输出将生成一个时钟,该时钟在拉入输入时钟频率时跟随VCO频率变化

lock:

锁定后,DSPLL将生成输出时钟,这些时钟的频率和相位都锁定到其选定的输入时钟。此时,任何XTAL频率漂移都不会影响输出频率。锁销丢失 (LOL) 和状态位指示锁何时失效。

2594

2594

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?