前言:

之前的工作中使用有限状态机模型管理游戏流程,趁这段工作空窗期总结一下状态机的相关知识。

一.状态机相关概念:

有限状态机(Finite State Machine),以下简称FSM,是一种描述离散状态的数学模型,在FSM模型中,可以将系统分解成有限数目的离散稳定,相互独立又有联系的状态。FSM中最基本的三点:

(1)状态的定义;

(2)状态的迁移;(在FSM中,一般通过事件使状态发生迁移)

(3)伴随状态迁移而产生的动作;

除了这最基本的三点,还有其他的扩展,如:状态监护条件,状态进入或离开动作,状态机嵌套(子状态机),并行状态机,状态历史记录(深层,浅层记录)等等。

二.在游戏中的应用

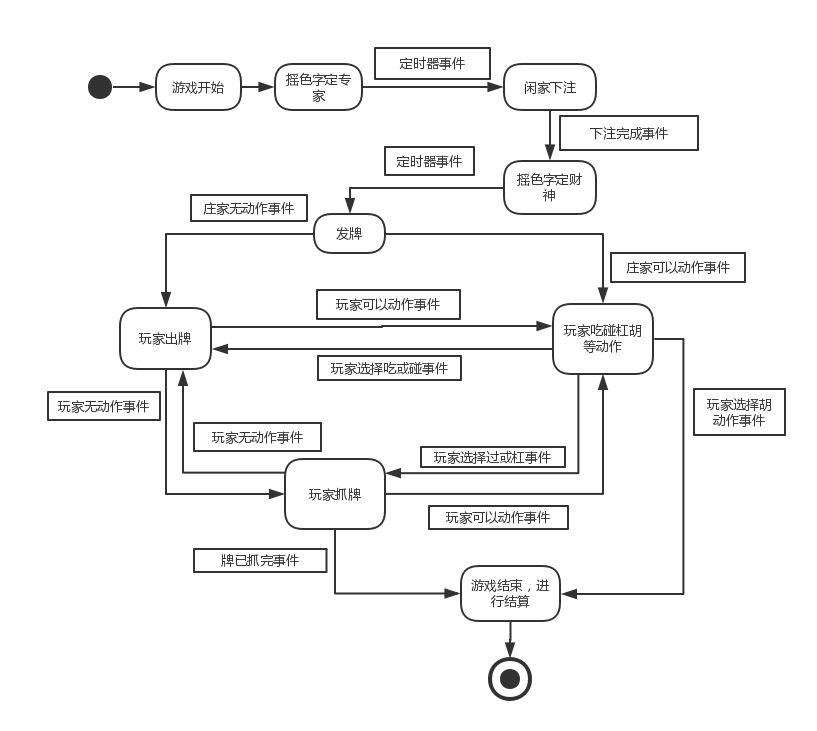

这里只谈棋牌游戏类型,其本质是在游戏规则的约束下,通过一系列事件来改变自身的状态,直到游戏结束。以麻将游戏为例,其状态机图类型如1.0图(简化版):

图1.0 麻将状态机图

椭圆形为状态,例如:游戏开始,摇色子定庄家,闲家下注等;

方形为驱动状态变迁的事件,例如:定时器事件,下注完成事件等;

注意到,状态的拓扑结构是静态的,而驱动状态变迁的事件发生是动态的。意思是游戏一旦开始跑起来,当前状态的变迁路径是固定的,A状态只能变迁到B状态或C状态,而不能变迁到D状态;而事件何时发生,能不能发生则和当局游戏过程,玩家的选择相关。

因此,游戏维护人员只要看游戏的状态拓扑结构就能知道整个游戏的流程是怎么样的。另外,当我们把游戏的状态拓扑关系放在配置文件中,例如用XML文件来配置游戏的状态变迁关系,则当需要改变游戏流程时可以只改配置文件,而无需改动代码。一个例子:如果现在不需要闲家下注,则只需要改配置文件,将摇色字定庄家状态的下一个变迁状态定为摇色字定财神状态就可以了。

三.现有的FSM工具

(1)UML状态机图:

本文介绍了有限状态机(FSM)的概念及其在游戏开发中的应用,特别是棋牌游戏。通过UML状态机图进行设计,并讨论了使用boost::statechart库和自造轮子的方式实现FSM。文中详细阐述了FSM基类的设计,以及如何根据项目需求扩展功能,以实现游戏状态机GameFSM。

本文介绍了有限状态机(FSM)的概念及其在游戏开发中的应用,特别是棋牌游戏。通过UML状态机图进行设计,并讨论了使用boost::statechart库和自造轮子的方式实现FSM。文中详细阐述了FSM基类的设计,以及如何根据项目需求扩展功能,以实现游戏状态机GameFSM。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1407

1407

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?