run behavioral simulation

run post-synthesis simulation

run post-synthesis timing simulation

run post-implementation function simulation

run post-implementation timing simulation

运行行为仿真

运行综合后仿真

运行综合后时序仿真

运行实现后的功能仿真

运行实现后时序仿真

RTL ANALYSIS:RTL分析;

Elaboration : 详细描述,将RTL优化到FPGA技术

Open Elaboration Design:

(1):report methodology:运行设计方法检查,以发现当前设计错误

(2):report DRC 运行设计规则检查,并报告检查结果

(3):Report Noise:基于XDC文件,检查sso(同时开关输出)

综合(SYNTHESIS):将RTL级设计描述转换为门级的描述,在该过程中将进行逻辑优化并且映射到Xilinx器件原语(技术映射),器件原语指的是那些门级原语

SYNTHESIS Settings:综合选项参数

RTL行为级仿真:功能仿真

综合后门级仿真:前仿真,输出一个标准网表文件,输出verilog/VHDL网表

时序仿真:后仿真,在设计布局布线后提供一个时序仿真模型

设计实现及分析(Implentation),对设计的逻辑和物理转换,Implentation setting :实现过程中的参数设置

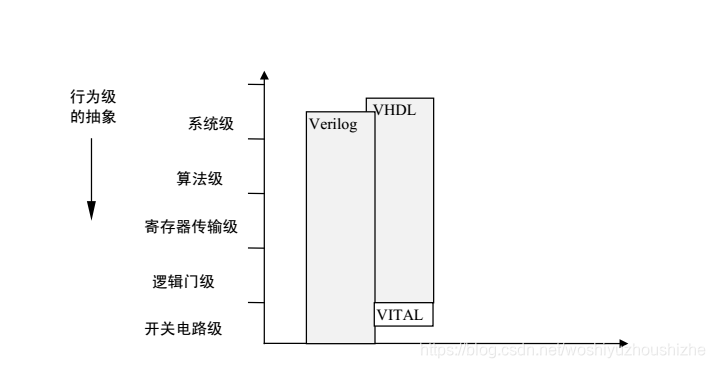

FPGA从上到下各个系统抽象模型依次为:系统级(System)———>>算法级(Alogrithem)————>>寄存器传输级(RTL)————>>逻辑级(Logic)———>>门级(Gate)———>>电路开关级(Switch)

在不同的层次做具体模块的设计所用的方法也有所不同, 在高层次上往往编写一些行为级的模块通过仿真加以验证,其主要目的是系统性能的总体考虑和各模块的指标分配,并非具体电路的实现。

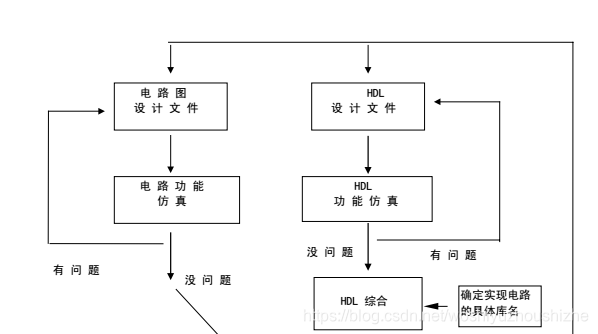

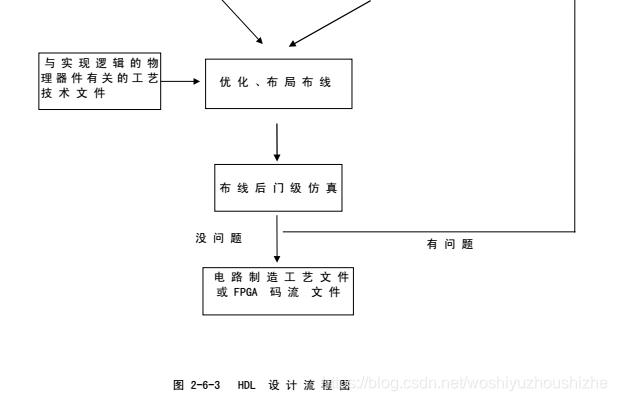

因而综合及其以后的步骤往往不需进行。而当设计的层次比较接近底层时行为描述往往需要用电路逻辑来实现,这时的模块不仅需要通过仿真加以验证,还需进行综合、优化、布线和后仿真。总之具体电路是从底向上逐步实现的。EDA工具往往不仅支持HDL描述也支持电路图输入,有效地利用这两种方法是提高设计效率的办法之一。

下面的流程图简要地说明了模块的编译和测试过程:

817

817

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?