Vivado 结合Modelsim 实现综合后仿真的一种方法 Post-Synthesis Timing Simulation

使用Vivado 生成仿真所需文件

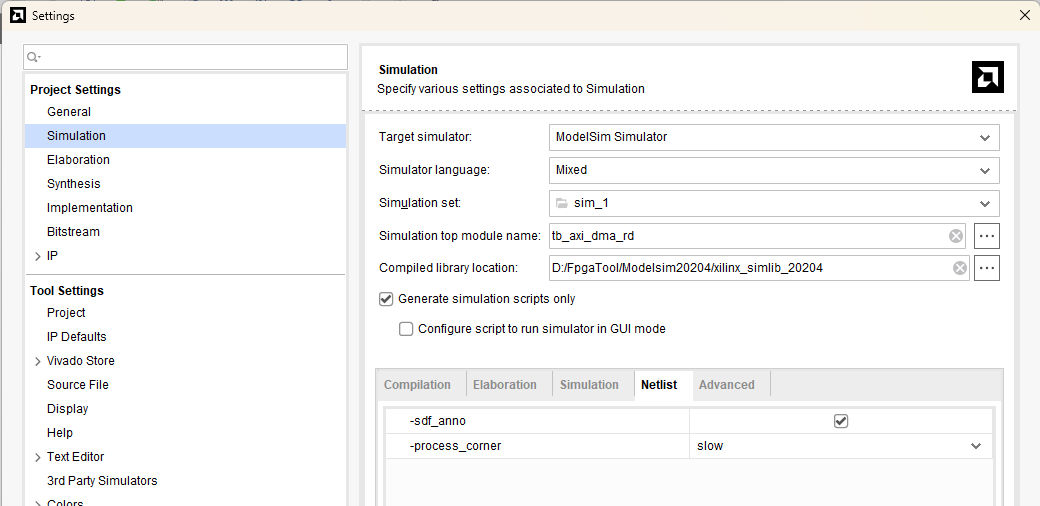

- Vivado simulation 中可勾选

Generate simulation scripts only; - 勾选

-sdf_anno;

- 在

testbanch文件中例化glbl,该文件可在vivado安装路径下找到,将其放到vivado工程的sim文件中; - 综合工程

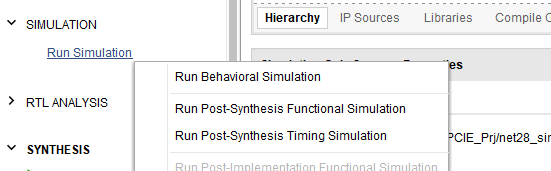

- 运行

Post-Synthesis Timing Simulation

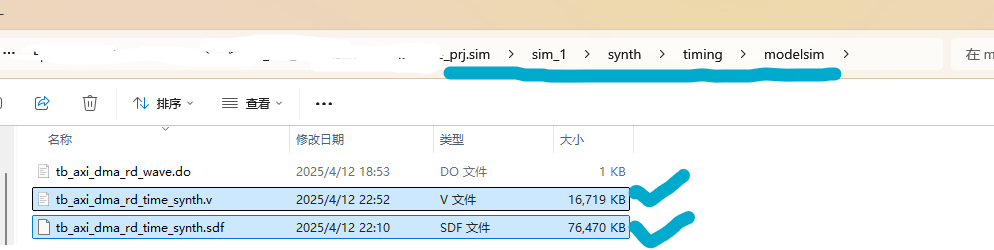

- 运行结束后可在工程目录下找到生成好的

sdf和网表文件;

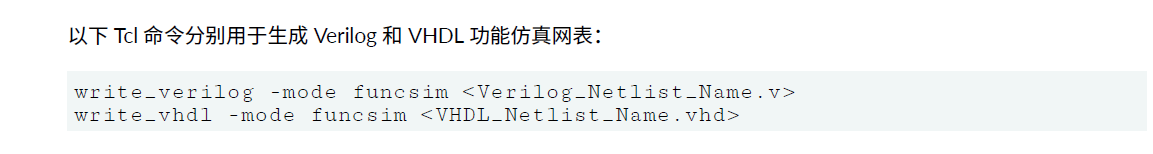

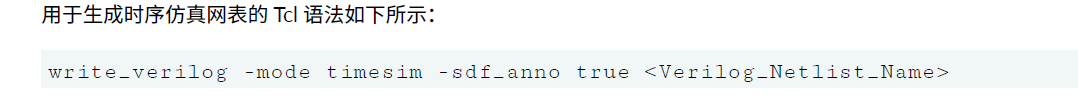

上述两个文件也可使用

TCL命令得到

创建Modelsim工程

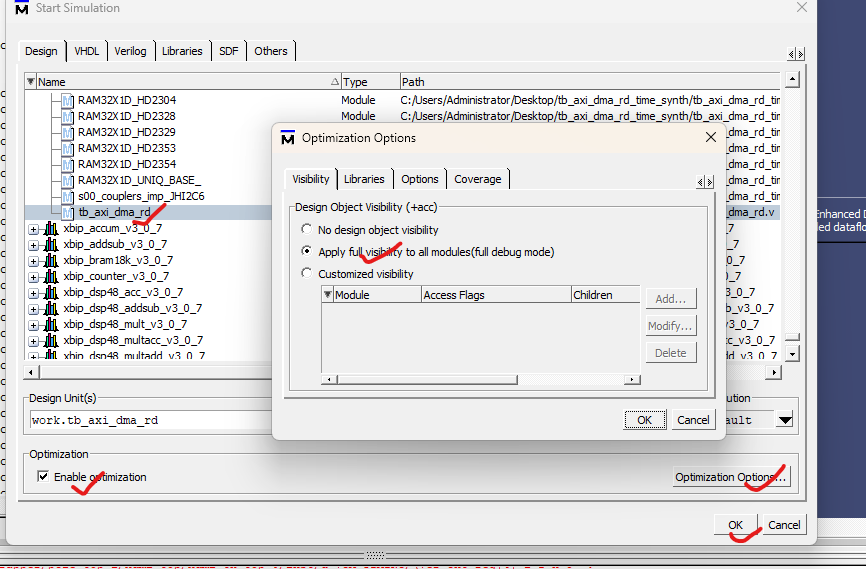

- 与功能仿真一致,创建工程,添加激励文件、模型文件;

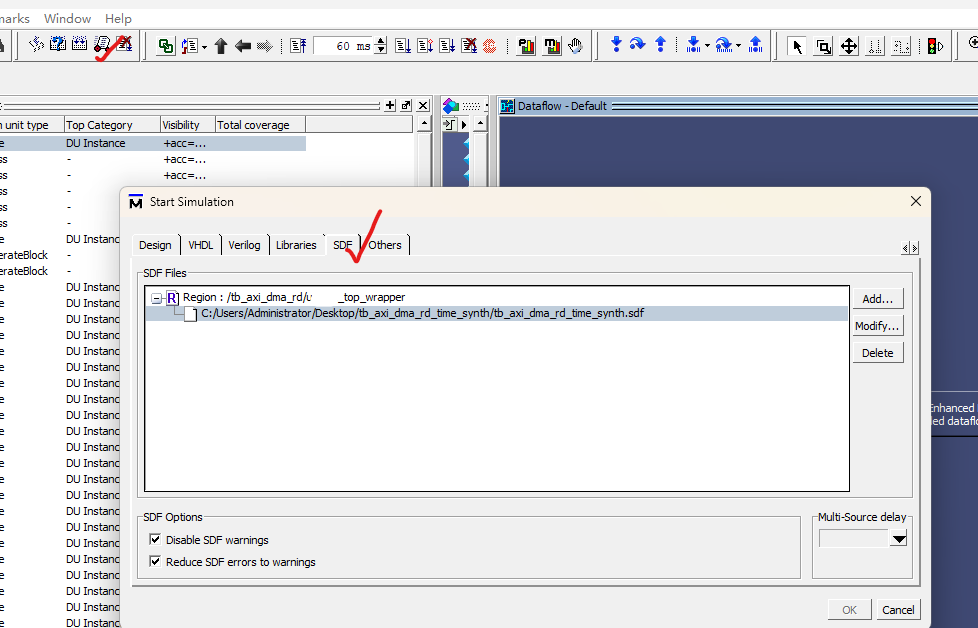

- 将待测文件使用

xxx_time_synth.v代替即可; - GUI界面添加SDF

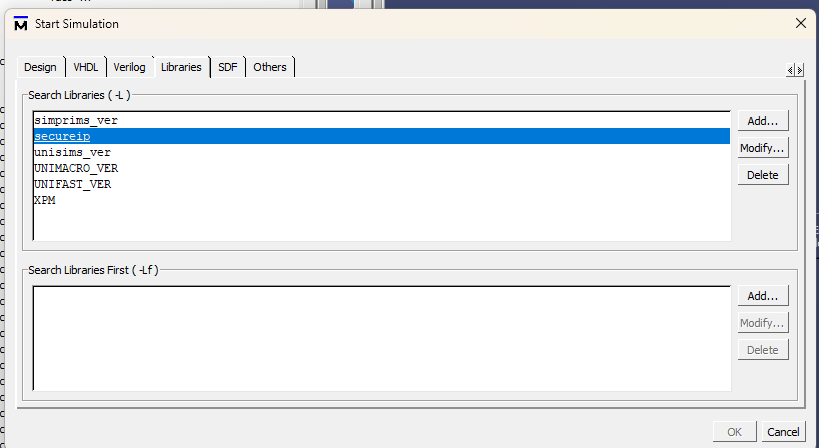

- 添加相关库文件

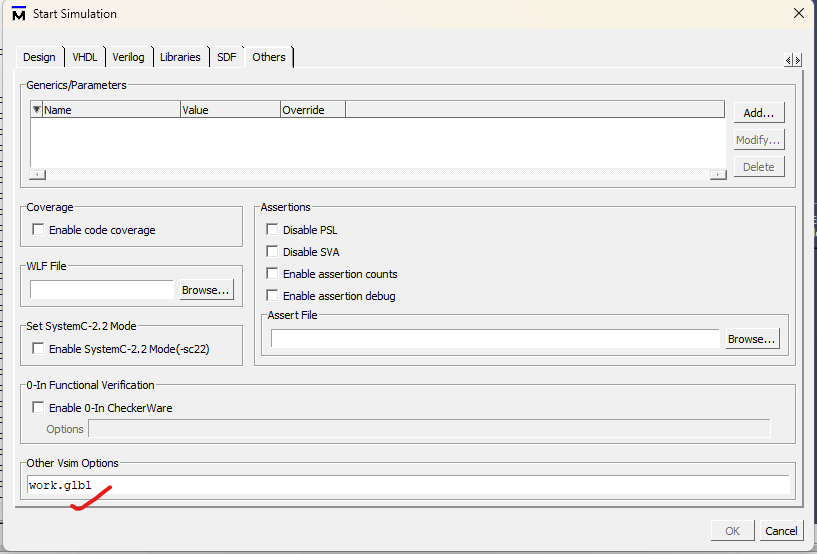

- 添加

glbl

- 启动仿真

- 添加波形、运行仿真即可

参考文档

- 《Vivado Design Suite 用户指南: 逻辑仿真 》(UG900)

1894

1894

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?