出自《基于Cadence的信号完整性仿真步骤.pdf》

目录

1.仿真前的准备工作1.1 找到需要仿真的芯片的IBIS 模型

1.2 模型转换(IBIS→DML)

1.3 添加模型到Cadence 的模型库中

2.对电路板进行设置(Setup Advisor)

2.1 准备好要仿真的电路板

2.2 调用参数设置向导

2.3 叠层设置

2.4 设置DC 电压值

2.5 器件设置(Device Setup)

2.6 SI 模型分配

2.7 SI 检查(SI Audit)

2.8 完成参数设置

3.进行信号完整性仿真(反射)

3.1 开始仿真

3.2 选择所要仿真的网络

3.3 提取网络的拓扑结构

3.4 给驱动端U8 添加激励信号

3.5 设置激励信号的参数

3.6 执行反射仿真

3.7 仿真结果

1.仿真前的准备工作

1.1 找到需要仿真的芯片的IBIS 模型

一般可以从芯片制造商网站上找到,如果没有,可能要通过其它途径获得如从SPICE 模型中提取。

1.2 模型转换 (IBIS→DML)

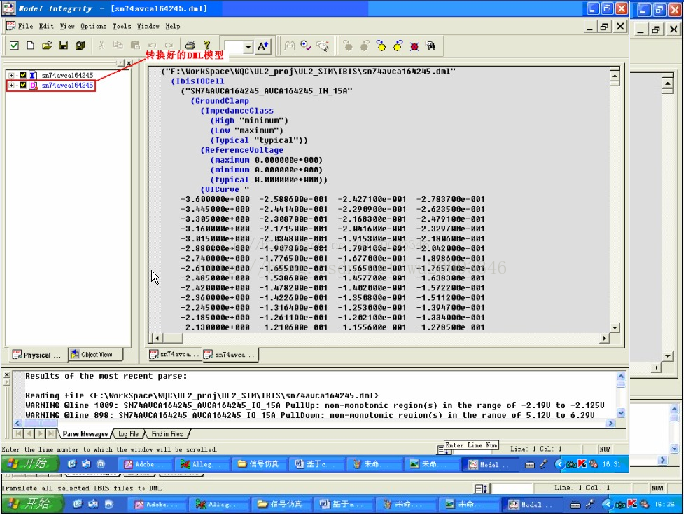

将IBIS 模型转换为DML 模型,运用Cadence 的Model Integrity 工具将IBIS 模型转化为Cadence 能识别的DML 模型,并验证仿真模型。

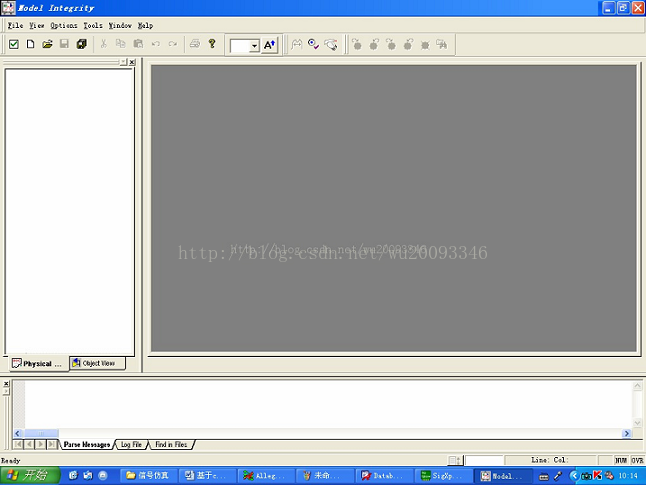

(1)单击“开始”按钮→“所有程序”→“Allegro SPB 15.5”→“Model Integrity”,如图1-1 所示:

图 1-1 Model Integrity 工具窗口

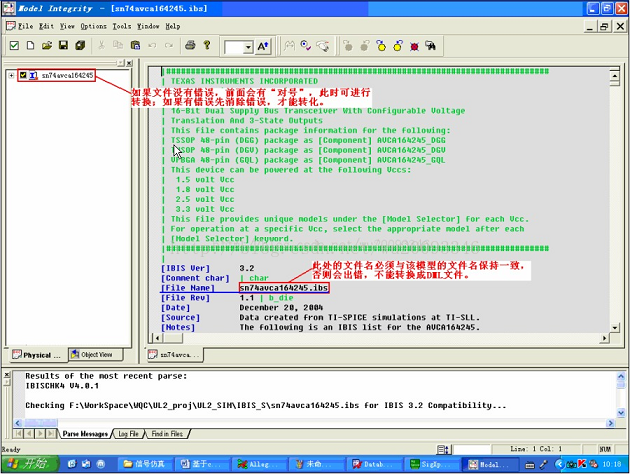

(2)选择“File”→“Open”,打开一个IBIS 模型如图1-2 所示:

图 1-2 打开一个IBIS 模型

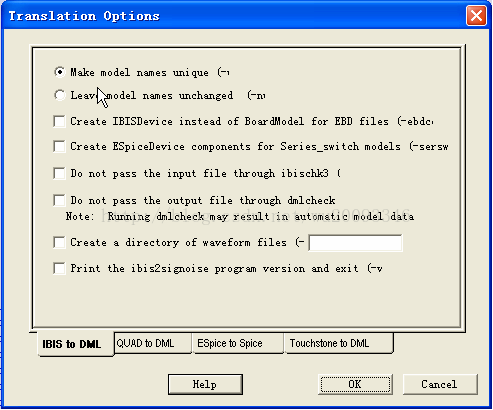

(3)在“Physical View”栏中,单击IBIS 文件“sn74avca16245”→选择菜单栏里的“Options”→“Translation Options Editor”→弹出“Translation Options”窗口,如图1-3 所示:

图 1-3 Translation Options 窗口

(4)默认选择“Make model names unique”,这个设置为每个IOCell 模型名附加IBIS 文件名。单击“OK”,关闭“Translation Options”窗口。

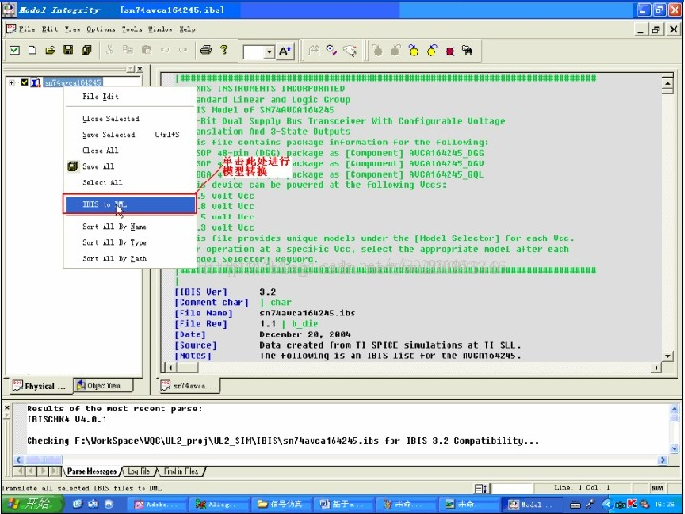

(5)在“Physical View”栏中,单击IBIS 文件“sn74avca16245”→单击鼠标右键→选择“IBIS to DML”(如图1-4 所示),系统会提示是否重写→选择“是”(如图1-5所示),重写文档。这时在原先IBIS 文件的目录下面会生成相应的DML 模型(如图1-6所示)。

图 1-4 IBIS→DML 转换窗口

图 1-6 转换好的DML 模型

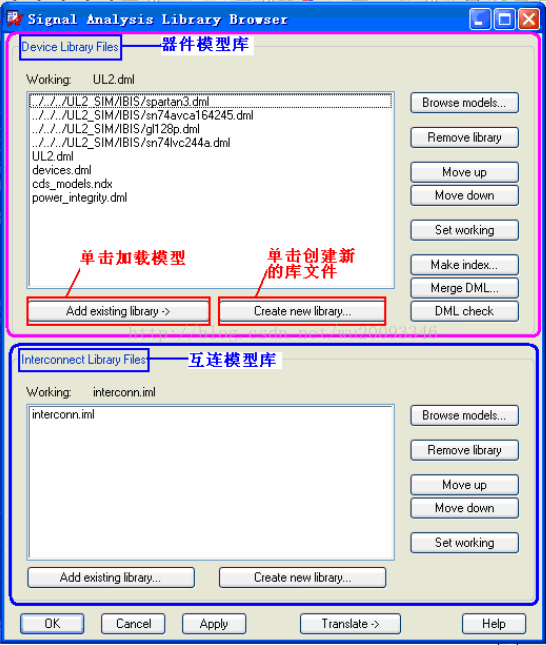

1.3 添加模型到Cadence 的模型库中将转换好的DML 模型加载到Cadence 的模型库中,在Allegro PCB SI 610 选“Analyze”,“SI/EMI Sim”,“Library”,如图1-7 所示。窗口分上下两个部分,上半部分是器件模型库;下半部分是互连模型库,包括传输线模型和Via 模型。当提取网络的拓扑结构时,互连模型会自动创建。这里主要是加载器件的模型。

图 1-7 将DML 模型加载到Cadence 的模型库中

未完。

1842

1842

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?