在数字电路中,时钟十分重要,时钟处理是fpga的特色,在后续设计中使用频率很高。一般分频我们有俩种方式,一种是用fpga自带的pll核,另一种是自己动手写代码描述。下面我们先用6分频举例来看看如何实现偶数分频。

module clk_6(

input wire clk,

input wire rst,

output reg clk_6

);

reg [2:0] div_cnt;//声明时钟计数,6个计数,即是0-5,所以3比特即可

always@(posedge clk)begin

if(rst == 1'b1)begin

div_cnt <= 3'd0;

end

else if(div_cnt =='d5)begin

div_cnt<=3'd0;

end

else begin

div_cnt <= div_cnt +1'b1;

end

end

always@(posedge clk)begin

if(rst == 1'b1)begin

clk_6 <= 1'd0;

end

else if(div_cnt == 'd2)begin

clk_6 <= 1'd1;

end

else if(div_cnt == 'd5)begin

clk_6 <= 1'd0;

end

end

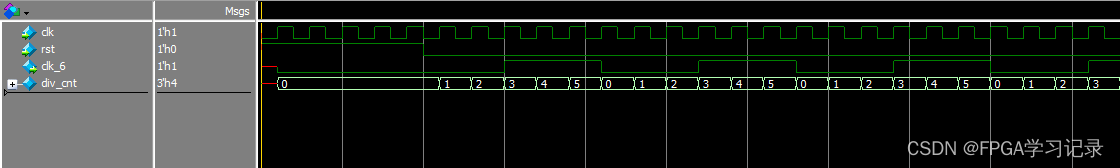

endmodule实现之后,我们用modelsim进行仿真测试

结果图如下

总结如下:偶数分频较为简单,通过计数器计数即可解决。如果进行N倍(偶数)分频,那么通过时钟触发计数器计数,当计数器从0计数到时,输出时钟进行翻转,以此循环下去。

441

441

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?