1、模块级建模

(1)模块调用方式

语法格式:模块名 <参数值列表> 示例名(端口名列表)

示例如下:

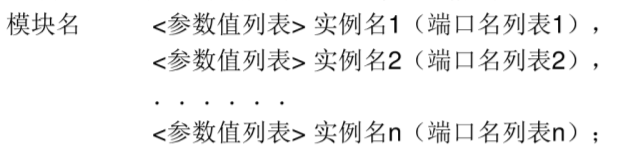

当一个模块在当前模块被调用多次,其语法格式为:

当定义的模块为标量时,若对其进行矢量调用,语法格式为:

<被调用模块名> <实例阵列表> [阵列左边界:阵列右边界](<端口连接表>)

(2)模块对应方式

a)端口位置对应方式

语法格式:模块名 <参数值列表> 实例名 (<信号1>,<信号2>,…,<信号n>)

b)端口名对应方式

语法格式:模块名 <参数值列表> 实例名 (端口名1<信号1>,端口名2<信号2>,…,端口名n<信号n>)

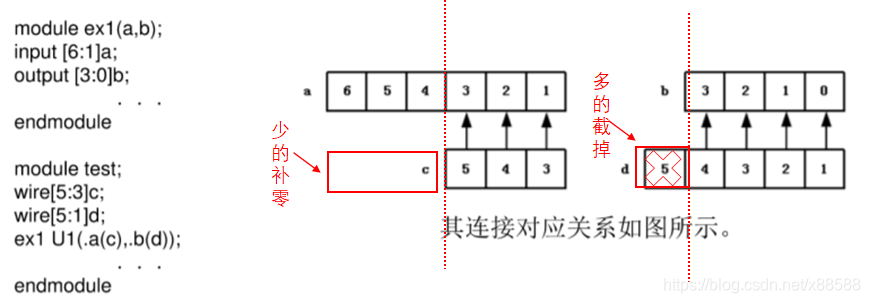

c)不同端口位宽的匹配

当端口和端口的表达式位宽不一致时,会进行端口的匹配。

d)模块参数值

使用带有参数的模块实例语句修改参数值,语法格式为:模块名 <参数值列表> 调用名(端口名列表)

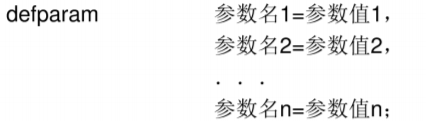

使用定义参数语句(defparam)修改参数值,语法格式为:

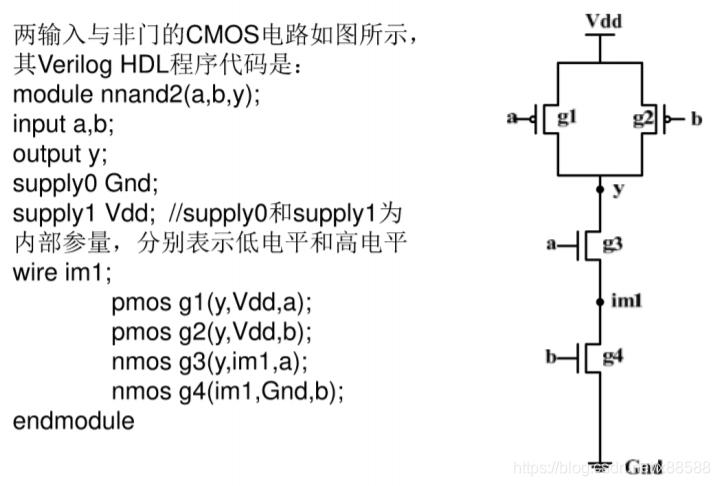

2、门级建模

(1)基本门级元件类型

(2)门模块调用

语法格式:门类型 <实例名> (<输出端口>,<输出端口1>,…<输出端口n>);

最多输入信号不能超过9。

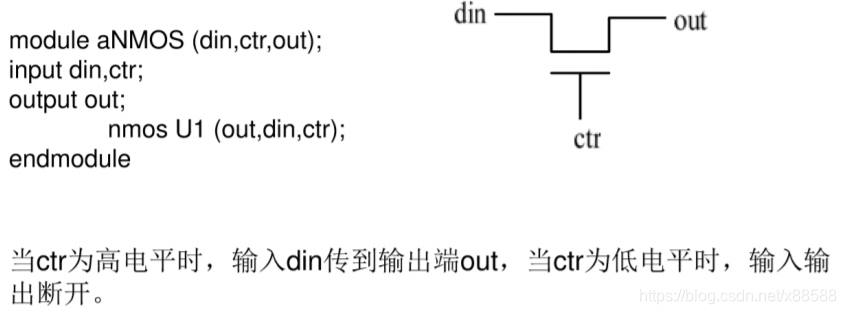

3、开关级建模(区别于VHDL的特点)

(1)MOS开关

(2)双向开关

647

647

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?