AHB介绍

AHB总线一开始面向系统级高性能,低功耗的系统互连。随着系统的发展,AXI总线作为高速总线的优势更加明显。AHB更多用于简单的数据传输,后来对AHB协议进行简化,定义了AHB-Lite,简化后的AHB主要用于单master数据访问。目前AHB多用于片上memory或低带宽需求的外设接口。

AHB总线接口的定义如下表所示:

Signal | Width | Destination | description |

hclk | 1 | salve | 总线时钟,上升沿有效 |

hrstn | 1 | slave | 总线复位信号,低有效 |

hsel | 1 | slave | 由Decoder产生,高电平表示当前slave被master选中 |

hwrite | 1 | slave | 表示传输方向,high(写),low(读) |

haddr | 32 | slave | 总线地址 |

hwdata | 32 | slave | 总线数据 |

htrans | 2 | slave | 传输类型,0(IDLE),1(BUSY),2(NONSEQ),3(SEQ) |

hsize | 3 | slave | 传输大小,size=(2**hsize)*8bits,最大支持1024bits |

hburst | 3 | slave | 突发类型 |

hprot | 4 | slave | 保护控制信号,需slave带保护功能,一般不用 |

hmastlock | 1 | slave | 当前master正在执行locked操作,与hmaster时序相同。 |

hmaster | 4 | slave | master识别符,由具有多个独占线程的主机产生 |

hready | 1 | slave | 由multiplexor产生,用于slave判断master是否对其它设备完成操作 |

hreadyout | 1 | multiplexor | 由slave产生,当master发起读写操作时,如果slave不能及时响应,把此信号拉低,用于延长传输。 |

hrdata | 32 | multiplexor | 从slave读取的数据,数据位宽可以扩展,推荐32bits |

hresp | 2 | multiplexor | slave发出的传输状态,0(OKAY),1(ERROR),2(RETRY),3(SPLIT) |

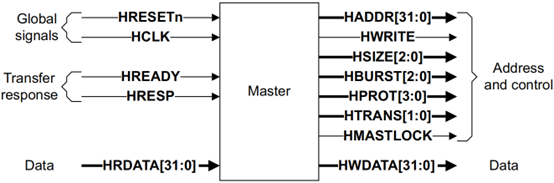

在一个系统中,主机提供地址和控制信号来发起读写操作,主机的接口如下图所示:

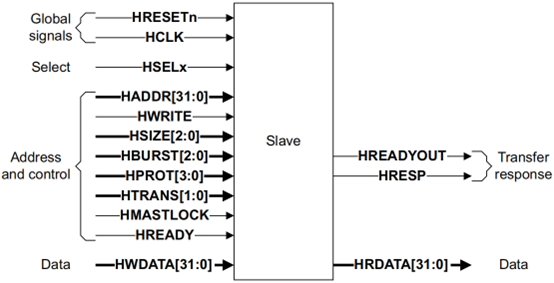

从机通过hsel信号来确定是否要响应主机发起的操作请求,从机的接口如下图所示:

基本传输

一次传输包含两个阶段:

地址传输阶段:除非前一个传输需要延展,否则只需一个hclk周期;

数据传输阶段:根据hready信号控制完成传输的时钟周期。

无等待传输

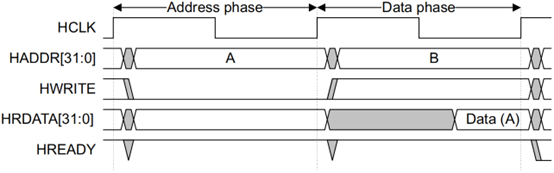

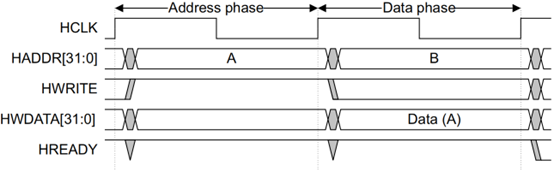

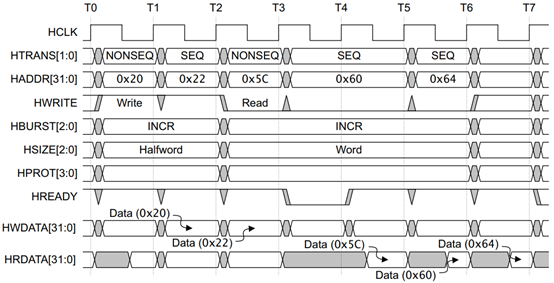

下图是一个无等待读操作的时序关系图

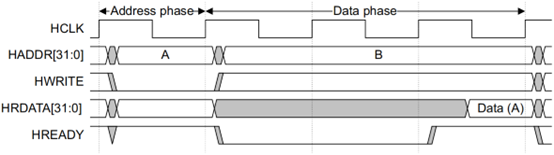

下图是一个无等待写操作的时序关系图:

步骤分析:

Step1:Master在hclk上升沿驱动地址和控制信号到AHB总线上;

Step2:在下一个hclk上升沿,从机采集地址和控制信号;

Step3:Slave采集到地址和控制信号后,驱动hready进行响应,在第三个hclk上升沿Master采集hready信号。

有等待传输

下图是等待2个时钟周期读操作时序关系图:

步骤分析:

Step1:Master在hclk上升沿驱动地址和控制信号到AHB总线上;

Step2:在下一个hclk上升沿,从机采集地址和控制信号,但hready在两个时钟周期内没响应,Master保持当前地址和控制信号;

Step3:第4个hclk上升沿后,Slave驱动hready拉高,进行响应,完成读操作。在第5个hclk上升沿Master采集hready信号。

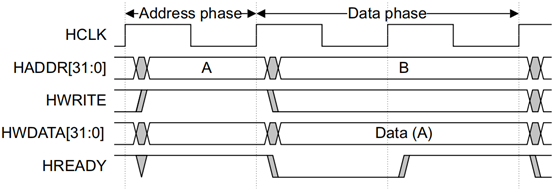

下图是等待1个时钟周期写操作时序关系图:

步骤分析:

Step1:Master在hclk上升沿驱动地址和控制信号到AHB总线上;

Step2:在下一个hclk上升沿,从机采集地址和控制信号,但hready在接下来1个时钟周期内没响应,Master保持当前地址和控制信号;

Step3:第3个hclk上升沿后,Slave驱动hready拉高,进行响应,完成写操作。在第4个hclk上升沿Master采集hready信号。

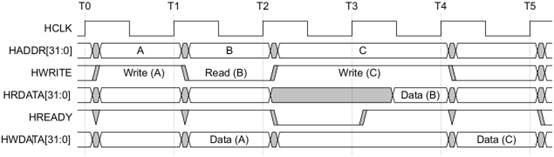

下图是等待1个时钟周期读写交替操作的时序关系图:

步骤分析:

Step1:Master在第1个hclk上升沿驱动A写地址和控制信号到AHB总线上;

Step2:第2个hclk上升沿,Slave采集A写地址和控制信号,hready为高,完成A的写操作。同时,Master发起B读地址和控制信号到总线上;

Step3:第3个hclk上升沿,Slave采集B读地址和控制信号,由于Slave不能及时响应hready为低,总线进入等待状态;

Step4:第4个hclk上升沿后,Slave进行响应,hready拉高,完成读操作;

Step5:第5个hclk上升沿,Slave采集Master请求的C写地址和控制信号;

Step6:信号hready为高,完成C写数据操作。

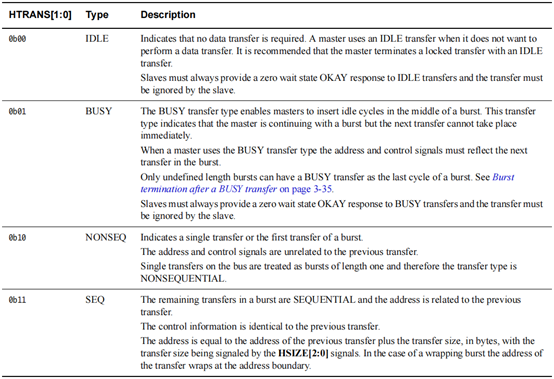

传输类型

总线AHB通过htrans[1:0]信号来控制总线的传输类型,类型如下表所示:

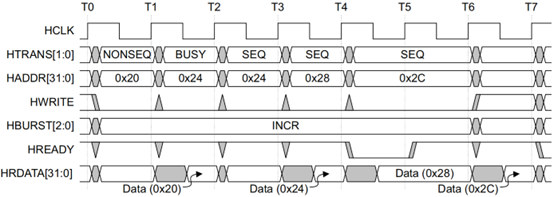

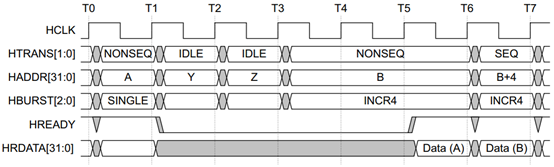

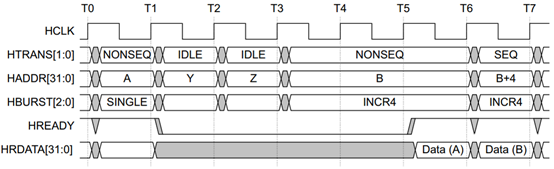

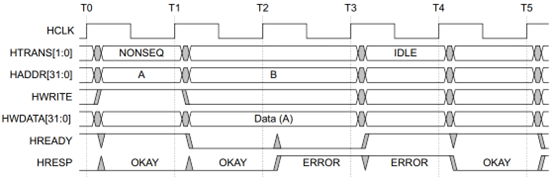

下图展现的是传输类型的时序图:

步骤分析:

T0-T1:突发长度为4beats,以NONSEQ起始的读操作;

T1-T2:hready为高,Slave发送读数据到总线。Master插入BUSY传输类型,推迟Burst的第2beats的传输;

T2-T3:Master继续Burst传输,发送SEQ传输类型到总线;

T3-T4:Master继续Burst第3beat读请求;

T4-T5:Master继续Burst第4beat读请求,hready为低,进入等待状态;

T5-T6: hready拉高,Slave提供第3beat读数据;

T6-T7: Slave提供第4beat读数据;

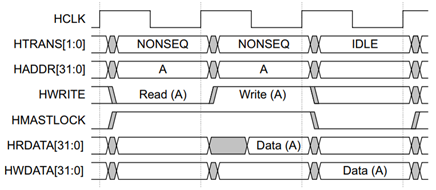

锁定传输

通常,锁定传输是为了维护信号量的完整性,从机在读或写完成之前不进行其他操作。

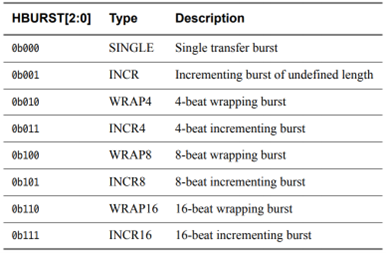

突发操作

突发操作支持incrementing和wrapping突发。

主机不要发送超过1KB地址范围的递增突发。

传输一个busy后突发终止

在未定义突发长度的incrementing突发传输中,主机可以插入busy确定没有数据需要被传输。但协议不允许主机通过在固定突发长度的情况下插入busy来终止突发传输。固定长度的如法必须以SEQ传输类型终止。

不允许主机在single突发后立即执行busy传输。single突发后必须跟随IDLE或NONSEQ传输。

提前终止突发

1、从机发送error response

如果从机发出error响应,主机可以取消突发中的剩余传输,或,继续突发中剩余传输。如果主机取消了突发中的剩余传输,主机必须在两个周期error响应期间将HTRANS变为IDEL状态。

2、多层互连终止

在一个多主机系统的多层互连设备的情况下,可以终止一个突发,使另一个主机获取从机的存取权限。从机必须终止原主机的突发,并且给新主机适当的响应。

突发举例

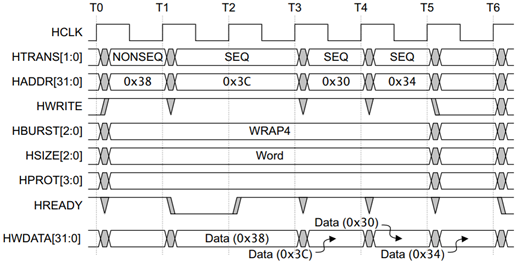

下图,突发长度为4的wrapping(WRAP4)写突发传输。

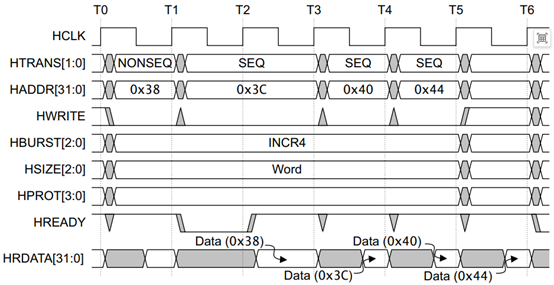

下图,突发长度为4的incrementing(INCR4)读突发传输。

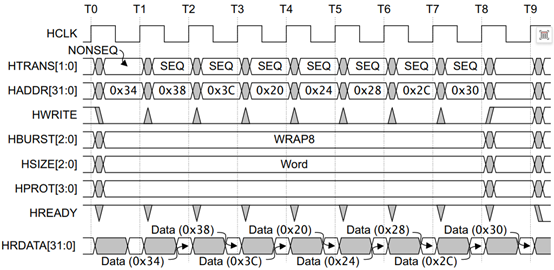

下图,突发长度为8的wrapping(WRAP8)读突发传输。

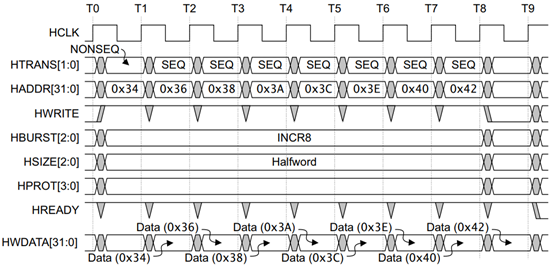

下图,突发长度为8的incrementing(INCR8)写突发传输。

未定义突发长度的递增突发(INCR)传输。

传输等待

从机可以用hreadyout信号插入等待状态。等待期间,主机被限制改变传输类型和地址。

等待期间传输类型的改变

在从机请求等待状态时,除了下面三种情况,主机不能改变传输类型:

IDLE传输;

固定突发长度的BUSY传输;

不定义突发长度的BUSY传输。

下图,在等待状态下,IDLE状态,传输类型可以发生改变。

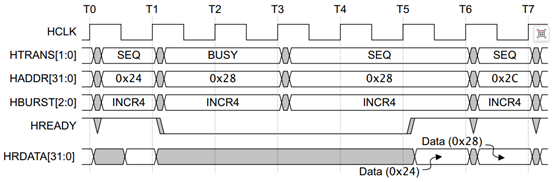

下图,固定突发长度,在等待状态下,BUSY状态,传输类型可以发生改变。

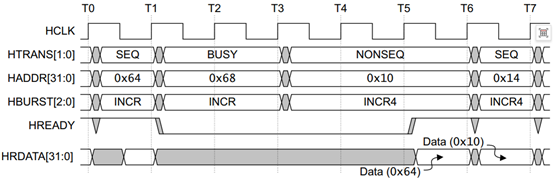

下图,不固定突发长度的递增突发,在等待状态下,BUSY状态,传输类型可以发生改变。

等待期间地址的改变

在从机请求等待状态时,除了下面两种情况,主机只能改变地址一次:

IDLE传输期间;

一个ERROR响应后。

下图,在IDLE期间,地址发生改变。

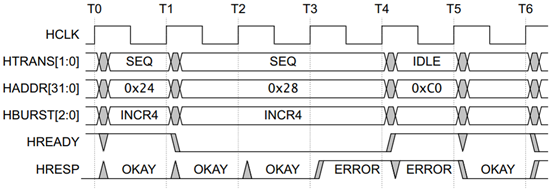

下图,从机发送ERROR响应后,地址发生改变。

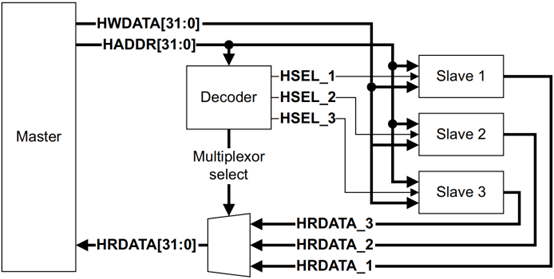

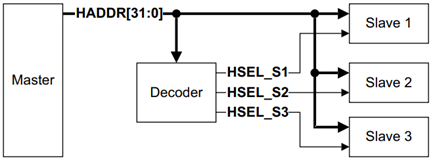

总线互连

互连组件是提供主机和从机之间的连接。单个主机系统只需要解码器(Decoder)和多路复用器(Multiplexor)。多主机系统需要提供仲裁器(Arbiter)和路由器(Router)。

地址解码

地址解码器提供一个选择信号HSELx,是根据高位地址产生。

分配给单个从机的最小地址空间是1KB。所有主机在不执行超过1KB的递增传输,确保突发传输不超过地址解码的边界。

如果一个系统不包含一个完整填充的地址映射,则需要实现一个额外的默认从机,以在访问任何不存在的地址空间时提供一个响应。

读数据和响应多路复用器

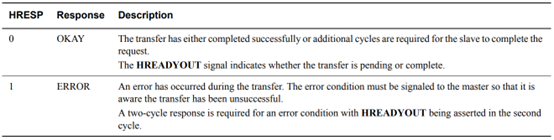

从机响应信号

主机发起一个传输后不能取消,从机必须提供一个响应,以指示传输访问的状态。

从机发送ERROR响应需要两个周期,在hreadyout信号为低电平时驱动hresp为高表示ERROR,在下一个周期驱动hreadyout为高以结束传输,同时保持hresp为高电平表示ERROR。由于总线的流水线性质,所以需要两个周期响应。当从机开始发送ERROR响应时,下一个地址已经发送到总线上。两个周期可以提供充足的时间让主机取消下一个访问,在开始下一个传输前,启动htrans进入IDLE状态。

独占传输

AHB5定义了独占传输属性。独占访问序列是单个主机独占传输的序列。操作步骤如下:

从一个地址执行独占读传输;

根据独占读数据,计算一个新数据写入到该地址;

独占读和独占写之间可以有其它非独占传输;

对同一个地址执行独占写传输,新数据的值为;

如果独占读之后没有其它主机写入该位置,独占写传输成功,并更新memory;

如果独占读之后有其它主机写入该位置,独占写传输失败,并memory位置不被更新。

5、独占写传输响应表明传输是成功还是失败。

独占传输相关联的信号:

HEXCL:独占传输,指示传输是独占访问序列的一部分,该信号是一个地址相位信号,与HADDR有相同的有效性约束;

HMASTER:主机识别符,一个主机拥有多个独占能力的线程必须产生该信号来区分线程。地址相位信号,与HADDR有相同的有效性约束;

HEXOKAY:独占成功,指示独占传输成功或失败的响应信号。

原子性

单拷贝原子大小

单拷贝原子大小定义了一次传输自动更新的字节数。

为一组相互通信的组件定义单拷贝原子大小,例如:

CPU、DSP和DRAM控制器在一个64bits单拷贝原子组中;

一个更大的组,包含CPU、DSP、DMA、DRAM、SRAM和外设在一个32bits单拷贝原子组中;

当一个写传输更新memory位置时,必须保证观测者看到其中一种情况:

memory位置未更新;

更新了至少一个单拷贝原子大小数量的数据。

字节选通信号(strobe)相关的传输不影响单拷贝原子大小。

多拷贝原子

如果一个系统有如下特征,则被定位为多拷贝原子性:

所有agent以同样的顺序能观察到相同位置的写入;

对一个agent(不是发行人)可以观察到的位置的写入,所有agent都可以观察到。

923

923

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?