AHB 协议学习

参考的是ARM AMBA3,仅供学习。信号大致看看,先看后边的传输和 other case 解释,这样理解的更快。

一、 AHB 协议 信号

HCLK:hCLK上升沿,进行传输

HRESETn:复位信号,低有效,直接接系统总线的reset信号

HADDR[31:0] : 32位系统地址总线

HTRANS[1:0] : 指示当前传输的类型,

2’b00 IDLE: master 占用总线,master没有收到requset ,master 没有transfer data;两次burst 传输之间,master 可以用idle;slave被使能,此时也无法得到地址信号,而且需要HRESP 回一个OKAY 给 master,

2’b01 BUSY: master 占用总线,burst 传输中还没有准备好下一次传输; 在burst 传输中间可以发送BUSY ;slave 不会在总线上收取数据,而是等待;slave 需要HRESP 回 一个OKAY 给master;master 需要给出下一拍的地址和控制信号;

2’b10 NONSEQ: 指示一次single传输或是burst传输的第一次数据传输,说明使用的地址和控制信号与时间顺序上上一次数据传输没有关系

2’b11 SEQ: 指示burst传输中非第一次数据传输,说明地址和之前的数据传输有相关,控制信息和上一次数据传输相同,访问的地址=上一次数据传输访问的地址+数据大小(单位是byte)。如果burst传输的类型是warp,则地址会存在循环的情况

HWRITE: 传输类型

'b1 表示写传输,'b0为低表示读传输

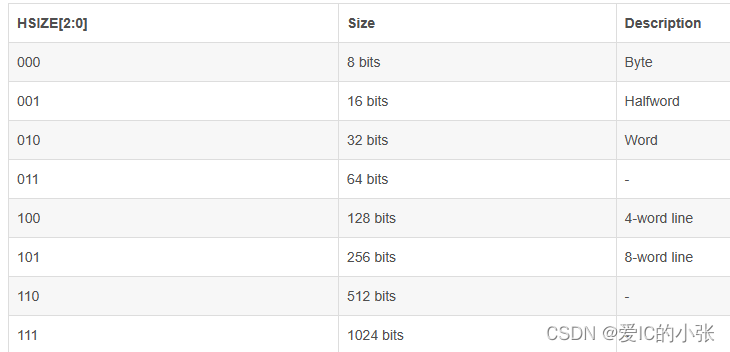

HSIZE[2:0]: 指示要传输的数据尺寸,

数据传输的大小。(注意:transfer size必须小于等于数据总线的宽度)

3’b000: 8bits ; 3’b001: 16bits ; 3’b010: 32bits ;

3’b011: 64bits ; 3’b100: 128bits ; 3’b101: 256bits ;

3’b110: 512bits ; 3’b111: 1024bits

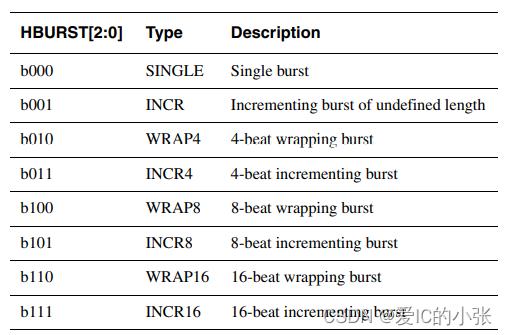

HBURST[2:0]: 指示本次传输对应的burst传输的包含多少beat,一个burst传输可以包含4,8,16个beat等

Burst类型。 WRAP(回环): :是固定的几个haddr 循环,INCR:地址增长

3’b000: SINGLE (单个传输burst)

3’b001: INCR (未定义长度的incrementing burst)

3’b010: WRAP4 (4拍 回环 burst)

3’b011: INCR4 (4拍 incrementing burst)

3’b100: WRAP8 (4拍 回环 burst)

3’b101: INCR8 (4拍incrementing burst

3’b110: WRAP16 (4拍 回环 burst)

3’b111: INCR16 (16拍incrementing burst)

HPROT[3:0]: 提供总线访问的额外信息,由master提供给slave

AHB协议的保护控制

HPROT[0] data/inst (1:数据访问, 0:取操作)

HPROT[1] privileged特权位 (1:特权模式访问,0 :用户模式访问)

HPROT[2] bufferable位 (1:write响应可以在中间点给出,0 :write响应必须在终点给出)

HPROT[3] modifiable位 (1:传输特性可以被修改,0 :传输特性不能修改)

HPROT[6:4] Slave HPROT[4] lookup位 (1: 传输必须在cache中查找,0 :传输不需要再cache中查找)

HPROT[5] allocate位,性能相关 (1:传输被分配到cache,0 :传输没有被分配到cache)

HPROT[6] shareable位 (1:传输与系统中其他masters共享,0 :传输没有与系统中其他masters共享)

HWDATA[31:0]: 由 master提供到总线上要写入的数据

HSELx: 片选信号, 选择哪个slave,选择信号是高位地址信号地组合译码。

从机 只能在HREADY信号为高时,采样地址和控制信号以及HSELx,HSELx为高表示当前传输已经完成。在特定地情况下有可能在HREADY为低时采样HSELx,但是被选中地从机将会在当前传输完成后变更。

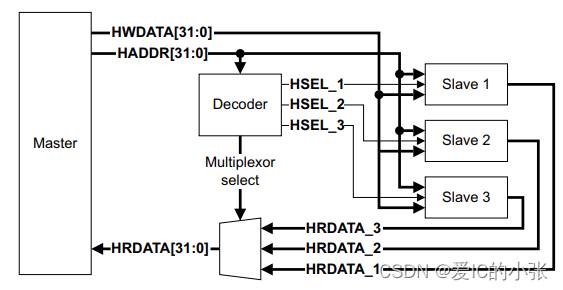

HRDATA[31:0]: 读数据总线,从decoder中选择的。

HREADY: 由slave提供,如果是master写表示写完成,拉高表示总线上一次transfer的结束,表示传输完成; 如果是master读表示读出的数据已放置在总线上。可以通过拉低延长一次transfer,即HREADY信号拉低时,master必须等待

从机放弃总线之前插入的最大等待状态数目,从机不要插入多于16个等待状态以阻止任何单个访问。

HRESP[1:0]: 由slave提供,包含关于transfer的额外信息,可选的信号有OKAY,ERROR,RETRY,SPLIT

[01]: ERROR: 传输失败返回error,响应终止。

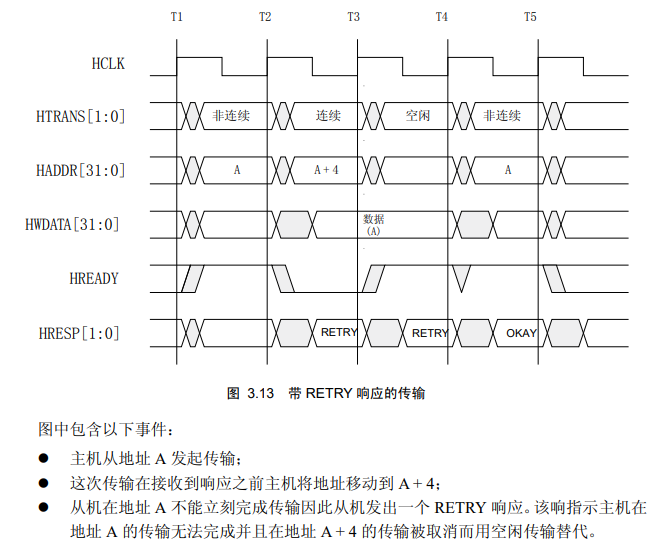

[10]: RETRY: 传输未完成,请求 master重新开始一个传输,arbiter 会继续使用通常 的优先级

[11]: SPLIT :传输未完成,请求 master 分离一次传输, arbiter 调整优先级方案 以便 其他总线的 master 可以访问总线,从机必须通知arbiter何时数据可用。释放总线给其他master访问总线。但更复杂了。

[00]: OKAY 表示传输正常并且当HREADY变高时 表示传输成功完成。

HBUSREQx: 由某个master发出到arbiter,用于请求总线

HLOCKx: 拉高表示master请求总线的独占访问,不允许其他master访问总线

HGRANTx: arbiter发出,指示某一个master具有访问总线的最高优先级,当一次传输完成即HREADY拉高时,优先级会发生改变,因此某一个master在HGRANTx和HREADY同时为高时获取总线权限

HMASTERx: arbiter发出,用于指示当前正在进行总线访问的master,可以为slave的split操作提供信息

HMASTLOCK: 指示当前总线上存在master正在进行独占访问; 当为高的时候, 表示当前的传输为locked sequence的一部分,该sequence不可分割,slave不能在sequence中间插入任何操作。它与地址和控制信号同步的。

HSPLITx[15:0]: slave发出,用于告诉arbiter哪一个master需要重试一次split传输

二、 AHB 协议 传输

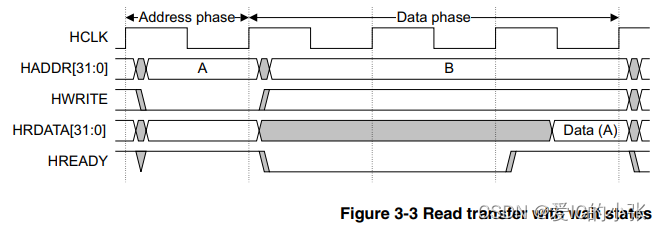

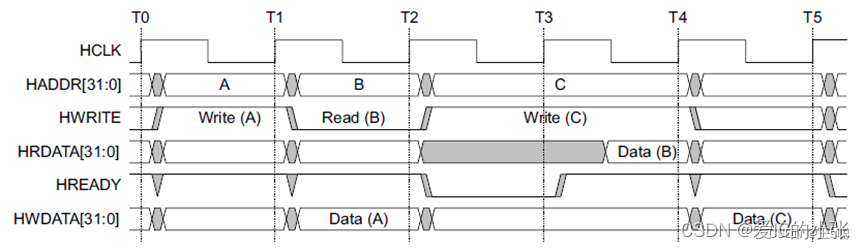

2.1 a read transfer with two wait states

由于HREADY 在第三个和第四个 clk 上升沿为低, 会告诉master, slave不能立即处理data(A)。当第五个clk上升沿检测到HREDAY 拉高,则master 立即读到 HRDATA;

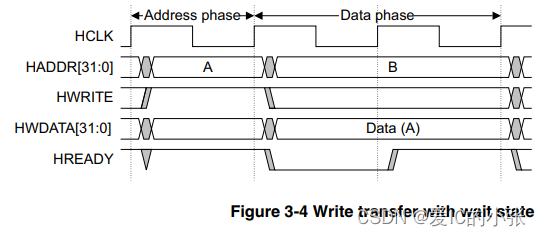

2.2 a write transfer with one wait states

直到HREADY 拉高,才表示master 的write data 传输完成

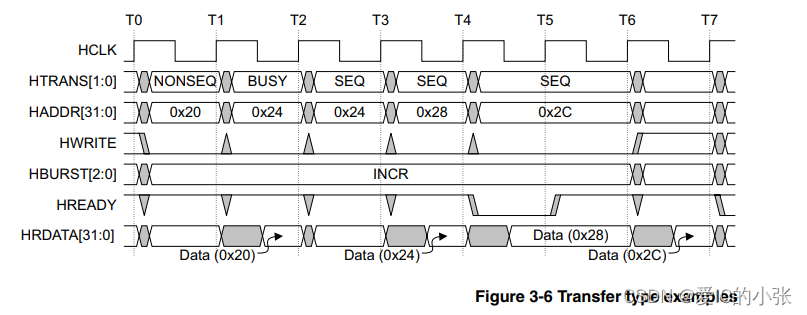

2.3 transfer with HTRANS(控制信号)

控制信号:

IDLE: master 占用总线,master没有收到requset ,master 没有transfer data;两次burst 传输之间,master 可以用idle;slave被使能,此时也无法得到地址信号,而且需要HRESP 回 一个OKAY 给 master,

BUSY: master 占用总线,但是在burst 传输中还没有准备好下一次传输; 在burst 传输中间可以发送BUSY ;slave 不会在总线上收取数据,而是等待;slave 需要HRESP 回 一个OKAY 给 master;master 需要给出下一拍的地址和控制信号;

NONSEQ: 指示一次single传输或是burst传输的第一次数据传输,说明使用的地址和控制信号与时间顺序上上一次数据传输没有关系

SEQ: 指示burst传输中非第一次数据传输,说明地址和之前的数据传输有相关,控制信息和上一次数据传输相同,访问的地址=上一次数据传输访问的地址+数据大小(单位是byte)。如果burst传输的类型是warp,则地址会存在循环的情况

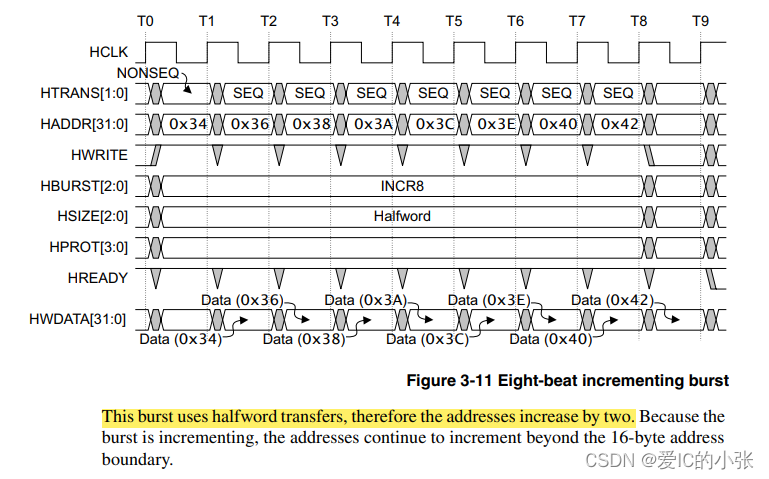

2.4 transfer :Eight-beat incrementing burst, INCR8

因为是HSIZE 是halfword 所以地址自增 2;

半字传输,连续增加通过了16字节边界。

未定义长度地 burst 传输

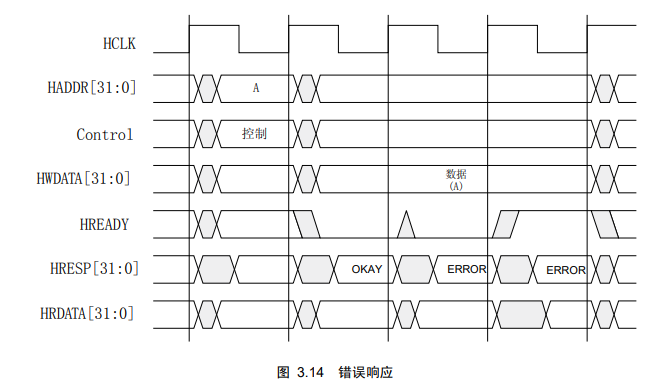

2.4.1 双周期响应传输

从机用了双周期的ERROR响应结束了传输,ERROR响应,当前传输不被重复。

注意图3.14在第一时间HREDAY为低电平时,同时响应必须被设为okay。在从机开始发出ERROR、SPLIT或者RETRY中任何一个响应时接下来传输的地址已经广播到纵向上了,所以会有双周期响应。

双周期响应允许主机有足够的时间来 取消该地址 并且在开始下一次传输之前驱动HTRANS[1:0]为空闲传输。

**2.5 other case

AHB 操作

master要访问总线首先要向arbiter申请权限,获得允许后就可以开始一次数据传输。首先master将地址和控制信号驱动到总线上,信号包括地址信息,读还是写,传输的数据尺寸,是否是一次burst传输的一部分等。

然后发送地址信息的周期无法被延长,所以slave必须在对应的周期采样地址和控制信息。但是数据传输周期可以被延长,只要slave拉低HREADY即可告诉master把当前数据在总线上多停留一拍(master写)或是在下一拍再读总线上数据(master读)

HRESP信息:OKAY表示传输正常,当HREADY和OKAY同时出现表示一次成功的数据传输;ERROR表示失败;RETRY和SPLIT表示传输无法立刻完成,但是master应当继续/重新尝试数据传输。

-

master 发起一笔传输后, slave 可以决定这笔传输的进程,而master 不能取消已经发出多的传输。

-

slave 通过HREADY 信号反映传输是否完成

slave 通过HRESP[1:0] 反映传输的状态, 如:立即完成传输;延迟几拍完成传输;延迟传输,释放总线 -

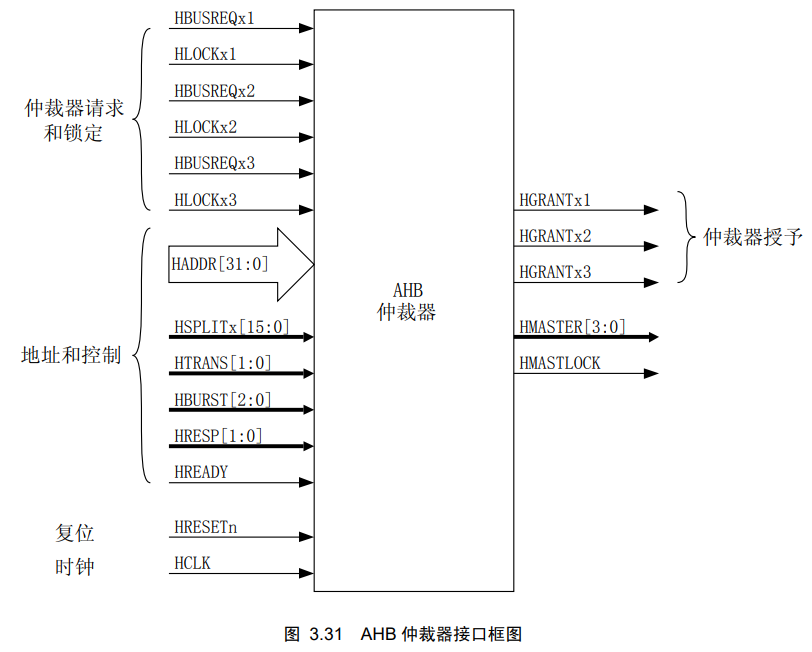

仲裁 arbiter

仲裁机制保证 任意时刻只有一个master 可以寄接入总线。 arbiter优先级算法,设计者需要根据具体的系统要求定义,AHB协议里没有写。 如果是一笔 burst 传输被打断,等master 重新获得接入授权后,会传递剩余的部分;

HBUSREQx: master 向 arbiter发出接入的请求信号;

HLOCKx: 指示是否要进行不可中断的传输,这一信号与HBUSREQx 同时由 master向arbiter 发出;

HGRANTx:arbiter产生指示master 获得授权,当HGRANTx信号为高同时HREADY为高时,master可以向总线传输地址信号。

HMASTER[3:0] : arbiter产生指示哪个master 获得授权,这一信号用于地址空制多路来选择哪个master接入总线;

HMASTERLOCK: arbiter产生指示当前传输是否为锁定序列传输;

HSPLIT : 支持split 传输使用 -

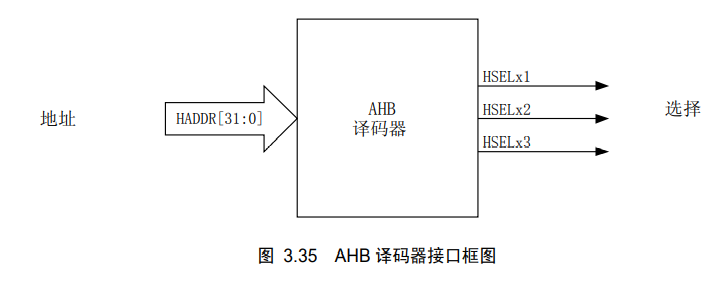

地址译码

地址译码器 为每个slave 提供选择信号 HSELx,组合逻辑对地址码译码;

HSELx 信号产生同时 HREADY 信号拉低,当前传输后 slave 会改变;

每个slave 最小的地址空间为1KB,所以master的burst 传输上线也是1KB,如此设计保证了不会出现地址越界问题;

当SEQ 或 NONSEQ 传输 访问到一个不存在的地址,默认slave应该提供ERROR 响应; 当IDLE或BUSY 传输 访问到一个不存在的地址,默认slave 响应 OKAY。

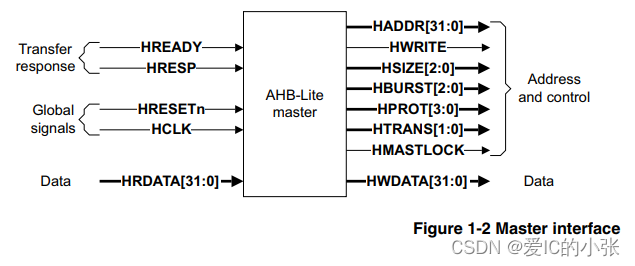

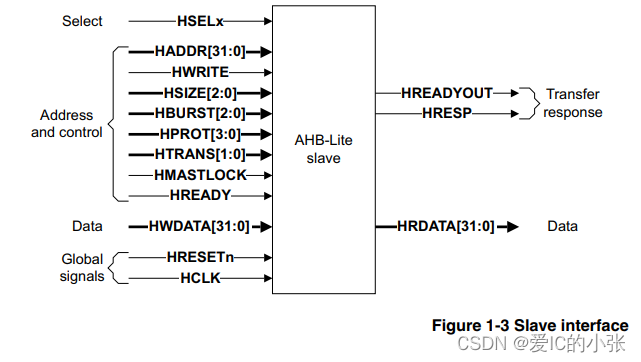

三、 AHB 模块接口(重要,会画)

四、burst transfer

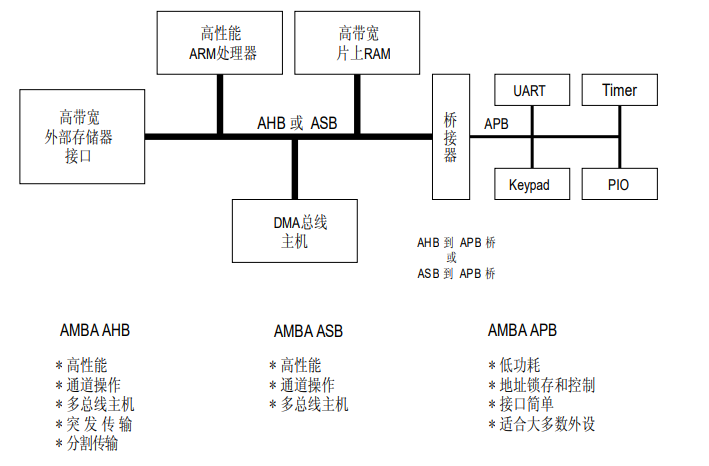

4.1 AHB -高效能系统总线 Advanced High-performance Bus 高性能、高时钟频率

写操作: 总线主机必须保持数据在整个扩展周期中稳定;

读操作: 从机没必要提供有效数据直到传输将要结束时;

4.2 AHB 突发操作 burst transfer

突发大小 表示 突发的节拍数量,并不是一次突发传输的实际字节数量。

一次突发传输的数据总量 = 节拍数(节拍数由hburst[2:0]指示) * 每拍字节数(每拍字节数由HSIZE[2:0]指示),一次突发是htrans的IDLE或NONSEQ分界的,而BUSY或SEQ是还在本次突发中。

所有突发传输 必须将 地址边界 和 传输大小对齐。: 例如:字传输必须对齐到字地址边界 (A[1:0] = 00) , 半字传输必须对齐到半字地址边界(A[0] = 0)。

- 如果 总线主机 因为 失去对总线的占有 而 不能完成一次突发 那么它必须在下一次获取访问总线时 正确地重建突发。

- 控制信号 和 地址总线 有严格一致地时序,在一次突发传输过程中 它们必须保持不变。

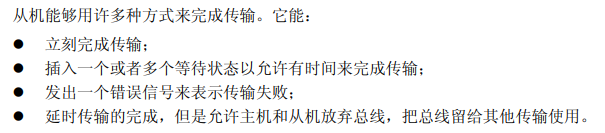

4.3 从机传输响应

主机发起传输后,由从机决定传输该如何进行。 AHB规范没有做出总线主机在传输已经开始后取消传输的规定。

只要从机被访问,那么它必须提供一个表示传输状态(由HREADY和HRESP[1:0结合表示传输状态])的响应。

仅有okay响应是单周期,ERROR、SPLIT、RETRY响应需要两个周期。

4.4 数据总线宽度和位传输

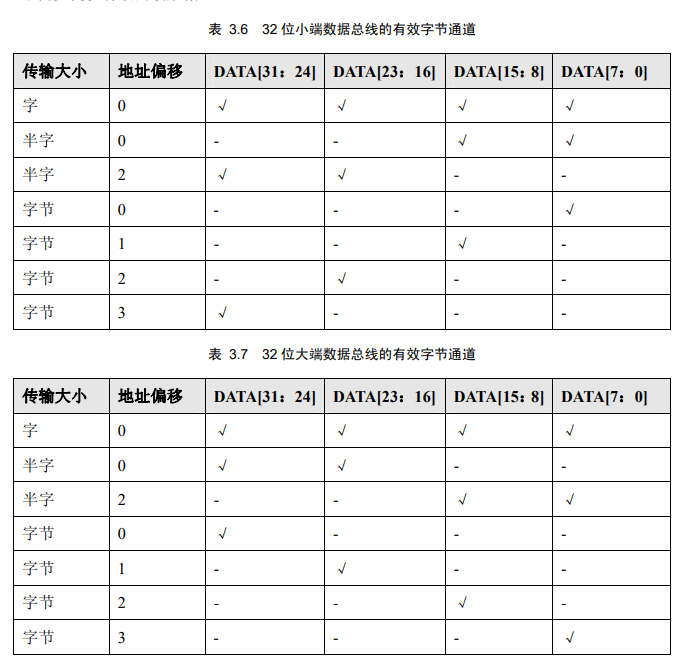

- HWDATAT[31:0]: 对于宽度小于总线宽度的传输:在32位总线上的16位传输,那么 总线主机 仅需要驱动相应的字节通道,从机 必须负责 从正确的字节通道选择写数据。

在 每拍 突发传输中 有不同 有效字节通道。

AHB对端结构没有要求,主机和从机结构要相同。 - HRDATAT[31:0]: 对于宽度小于总线宽度的传输:从机 仅需要驱动相应的字节通道,总线主机 必须负责 从正确的字节通道选择写数据。

不支持动态端结构,为了产生 体积更小、功耗更低、性能更高 的接口。

4.4 arbiter

用来确保任意时刻只有一个主机能够访问总线。

功能是 检测许多不同的使用总线的请求 和 决定当前请求总线的主机中哪一个的优先级最高。

4.5 AHB数据总线的位宽

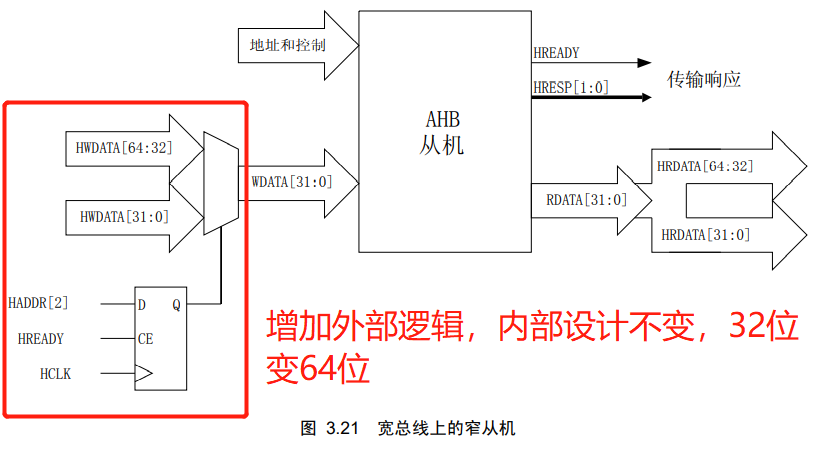

- 在宽总线上实现窄从机

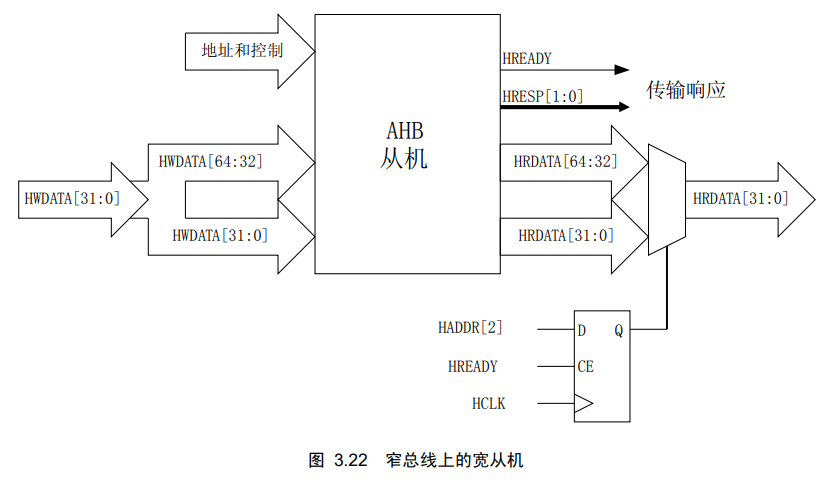

- 在窄总线上实现宽从机

- 在宽总总线上实现窄主机:

复制输出总线;多路选择输入总线。 - 总线主机不能工作在比原先设计要窄的总线上。

五、面试问题

- 当AHB写入数据之后从 同一地址读取 并且读取传输的地址阶段和写传输的数据阶段在同一周期时,读取返回的数据是旧数据还是新数据?

这个问题的答案取决于slave的设计。一个简单的slave将不会缓冲(cache或者buffer)任何数据,因此返回的读取数据将是最新的。对于复杂的slave 设计可能实现写数据的缓冲,这时候它可以返回以前存储的数据,或者"snoop"写缓冲中的内容。不管怎样都是符合AMBA AHB规范的,只要返回数据即可。

- 如果slave 可以被gate(clock gate或者power gate),需要哪些系统支持?

方案一:如果在slave 处于power gated或clock gated时进行访问,则必须确保该访问能够唤醒相应的slave,

方案二:将AHB decoder 配置为dummy slave,以便在访问gated slave时系统不会挂死。同时,在这种情况下需要确保“IDLE”访问时dummy slave拉高HREADY并且返回HRESP=OKAY;而“NONSEQ”访问和“SEQ” 访问返回ERROR

- 什么时候可以提前终止burst传输?

在一个Burst 传输中的任何一拍,slave返回非OKAY响应之后Bursts 传输可以提前终止,或者仲裁器将HGRANT给其他master。但是请注意,除非收到相应的仲裁器或slave响应提示,否则master不能主动地决定终止burst传输。

- HTRANS能在HREADY值拉低时改变吗?

一般来说,AHB master 不应在HREADY拉低时改变控制信号。但允许在以下条件下更改HTRANS:

-

HTRANS=IDLE

AHB master 正在执行内部操作,并且尚未开始进行总线传输。但是,在AHB等待状态(HREADY低)期间,master 决定开始总线传输,并在下一个周期中将HTRANS更改为NONSEQ。 -

HTRANS=BUSY

HTRANS被用来给master 来完成内部操作,这可能是完全独立于HREADY信号。因此,HTRANS可以在HREADY为低的周期中改变为任何值(SEQ:继续完成burst传输;NONSEQ:开始新的传输)。 -

HRESP=SPLIT/RETRY

如AHB规范中所述,非OKER响应需要两个周期才能完成(具体参见AMBA SPEC)。master 必须在SPLIT/RETRY响应的第二个周期的HTRANS上置起IDLE 。

-

HRESP=ERROR

和SPLIT/RETRY响应的处理需要两个周期一样,ERROR也需要两个周期处理,即在第二个周期刷新未进行传输的地址和控制信号。此时,第二个周期的HTRANS可以是IDLE或者继续完成当前的传输,这不是严格规定的。

- BUSY传输能够在burst刚结束时开始么?

BUSY传输只能在未定义长度的burst传输(INCR)结束时发生,不能在固定长度burst传输(SINGLE, INCR4, WRAP4, INCR8, WRAP8, INCR16, WRAP16)的末端发生。

- 所有slaves 是否都必须支持BUSY传输类型?

是的。所有slaves 必须支持BUSY 传输类型,以确保它们与任何总线master兼容。

- 地址是否必须对齐,即使是对于IDLE传输?

是的。即使对于IDLE传输,地址也应根据传输大小(HSIZE)进行对齐,防止在仿真过程中使用的总线monitor误报错误或者警告。

- 在一个AHB系统中可以有多少个master ?

AHB规范最多能有了16个master 。然而其中还包含一个dummy bus master,这意味着实际总线master 的最大数量实际上是15个。

在具有支持SPLIT 传输响应的slave 的系统中都需要一个dummy master,以便如果所有其他master 都收到SPLIT 响应,可以授予总线给dummy master。 dummy master需要将HTRANS驱动为IDLE,HLOCK驱动为低,所有其他输出驱动为合法值。

- HREADY是来自slaves的input 还是output?

AHB slaves必须同时将HREADY信号作为输入和输出。

HREADY需要作为slaves的输出,以便slaves可以扩展传输的数据阶段。

HREADY还需要作为slaves的输入,以便slaves可以确定先前选择的slaves何时完成最终的数据传输 。

每个AHB slaves应有一个HREADYOUT信号 ,该信号连接到Slave-to-Master多路复用器。这个多路复用器的输出是全局HREADYOUT信号,它被路由到AHB上的所有masters ,并作为HREADYIN反馈给所有slaves 。

- 一定需要有一个default slave么?

如果定义了整个4G地址空间,则不需要默认的slave。如果内存映射中存在未定义的区域,那么必须确保对不存在的地址的访问不会锁定系统。在decoder中实现default slave非常简单并且通常是有意义的。

- 当transfer 被扩展时,master 能否更改HADDR ?

如果master 指示它想要执行NONSEQ、SEQ或BUSY传输,那么在扩展传输期间(当HREADY较低时)不能更改地址。除非master 收到ERROR、RETRY 或SPLIT 响应,在第二个响应处理周期master 要进行IDLE传输,那么它可能会更改地址。

- 在整个burst传输期间,HPROT、HSIZE和HWRITE是否保持不变?

是的**,控制信号必须在整个burst期间保持不变。**

- AMBA AHB规范建议只使用16个wait 状态。如果需要超过16个周期,应该怎么办?

对于一些slaves ,可以插入超过16个等待状态。例如,只有在初始上电时才访问的boot ROM可以插入大量的等待状态周期,因为一旦系统上电完成,它不会影响系统性能 。slaves可以使用SPLIT 或者RETRY 响应来指示尚未完成的数据传输,或者可以使用中断或者状态寄存器查询slaves能否完成数据传输再发起请求。

- 不同bursts 的用处是什么?

通常,wrapping bursts被用来进行 cacheline数据填充。此时,master首先获取它所请求的数据,然后预取cacheline中剩余的数据。

incr bursts可以被DMA控制器使用进行不与特定地址边界对齐的cacheline的数据填充

- slave的HREADY信号和HRESP 信号的默认值应该是高还是低?

建议HREADY的默认值较高,HRESP的默认值为OKAY。此组合可确保slave正确响应IDLE传输类型,即使该slave处于低功耗省电模式。

- dummy master和default master有什么区别?

default master用于描述当系统中没有任何一个master请求访问总线时被仲裁选择到的master。通常,最有可能请求总线的master设置成default master。

dummy master是一个只执行IDLE传输的master。它在一个系统中是必需的,以便arbiter可以授予一个master仲裁,但是并保证不执行任何真正的传输。在两种场景下,仲裁需要dummy master:1、LOCK传输返回SPLIT 响应,2、当返回SPLIT 响应时,其他的master也正处于等待SPLIT响应的状态。

- HPROT的默认值建议是什么?

对于不需要这些保护信息的masters ,建议HPROT默认值为HPROT[3:0]=4‘b0011,即Non-cacheable, Non-bufferable, Privileged, Data Accesses

- 在复位过程中,AHB信号的状态是什么?

SPEC规定,在复位期间总线信号应处于有效电平(即逻辑“0”或者逻辑“1”),不能是 X态 或者 高阻态。 当然,具体是高电平还是低电平由设计去把握,需要强制约束的是,HTRANS需要为IDLE。

另外在复位过程中,需要确保系统中所有slave输出的HREADY需要为高,避免发生死锁, 特别是针对多slave的系统。 在这里需要了解输出hready和输出hready的区别。

- master 重建被终止的burst 传输时,是否有限制?

唯一的限制是,master 需要使用合法的burst组合来重建被终止的burst传输。 例如,如果一个master 执行8拍burst传输,但在完成3次传输后就失去了对总线的控制。这时其余的5次burst传输可以使用SINGLE burst传输,和INCR4 burst传输,也可以使用5拍INCR burst传输。

为简单起见,建议master 使用INCR burst传输来重建剩余的传输。

- AHB如何处理LOCKed SPLITs?

当传输被SPLIT 时,arbiter 将该master 从仲裁选择中移除 ,直到slave 指示传输可以完成。当访问是LOCKed 时,访问不能被另一个master访问中断。

AHB系统能够同时处理这两个需求的唯一方法是在访问请求LOCKed 并且被SPLIT时授予一个 “dummy master” 仲裁。dummy master在锁定传输期间只执行IDLE传输。 因为将 仲裁 授予任何其他的 master 都将违反 AHB LOCK 相关的协议。

当所有的请求响应都处于SPLIT 状态时,也需要使用 dummy master 在此期间一直发送IDLE传输 。 所以,建议支持split的slave要一直监测 HMASTLOCK 输入信号,因为此时split响应没有任何意义。

- AHB中的 wrapping burst 可以和 总的传输字节数 对齐么?

可以,此行为符合AHB协议。

以四拍传输大小为4字节的 wrapping burst 传输为例(共传输16字节)。 如果传输的起始地址是0x30,则 burst 传输的四次地址为0x30、0x34、0x38和0x3C。尽管HBURST 被设置为 WRAP4,但实际上不会发生wrap,当然这也是AMBA AHB协议允许的。

- master 应该在什么时候 拉高和拉低 locked 传输中的HLOCK信号?

HLOCK信号 至少在 locked 传输的地址阶段 开始 之前至少一个周期拉高,以便 arbiter 能够在地址阶段开始时采样到 HLOCK 信号。

在 locked 传输的最后一次传输的地址阶段,master 应该拉低 HLOCK 信号。

- master 什么时候应该拉低 HBUSREQ 信号?

对于一个未定义长度的burst 传输(INCR),master 必须保持其 hbusreq 信号的拉高状态,直到它开始了 burst 传输中最后一次传输的地址阶段。

对于定义长度的 burst 传输,一旦获得了第一次总线传输的授权,master 就可以拉低hbusreq 信号。 可以这样做的原因是,arbiter 可以计算 burst 传输中的传输数量,并保持授予给定 master 总线权限,直到 burst 传输完成。

- 在一次locked 传输后,arbiter 什么时候才可以授予另一个master 总线权限?

arbiter 总是在 locked 传输结束时 授予该 master 一拍额外的传输, 即 master 在 locked 传输的最后一次传输的数据阶段会在拉低 HMASTLOCK 信号执行一次传输的地址阶段。

在此期间,仲裁器可以将HGRANT信号更改为新的master,但如果上次locked 传输的数据阶段接收到SPLIT 或RETRY 响应,则master将驱动HGRANT信号给正在执行locked 传输的master (RETRY 响应场景) 或者授权给Dummy master (SPLIT 响应场景)。

- master 可以在burst传输期间拉低HLOCK吗?

AHB SPEC要求在burst传输期间所有控制信号(除HADDR和HTRANS外)保持不变。

因此,HLOCK必须在burst传输期间保持高,并且只能在最后一次的地址阶段拉低。

- 当master 没有请求但是被授予总线权限时,master 可以执行非IDLE以外的传输吗?

是的。master 没有请求总线时,可以执行IDLE以外的传输。 在这种情况下,仍然建议master 拉高其请求信号,以便arbiter 在传输进行期间不会将总线的权限授予给其他的master 。

- 如果默认情况下当前master 被授予了总线权限,那么在启动非idle传输之前,它必须拉高hbusreq多少个周期?

它可以立即启动一个非IDLE 传输。

- HLOCK 信号和 HMASTLOCK 信号之间的关系是什么?

在每个传输的地址阶段,arbiter 会采样master的HLOCK信号。如果此时HLOCK被拉高,则arbiter 将在传输的地址阶段拉高HMASTLOCK 信号。

- HGRANT信号什么时候可以改变?

HGRANT信号可以在任何周期中发生改变,可能出现以下情况:

1)、有可能在当前传输完成之前拉高然后拉低HGRANT信号,因为HGRANT信号只有在HREADY为高时才由masters采样。

2)、master 可以在没有请求总线的时候被授予总线 ,也可能在master请求的同一周期被授予总线

- 为什么 HADDR 有时为 arbiter 的输入?

地址总线HADDR不需要作为arbiter 的输入。 但在某些系统设计中,使用地址总线来确定在master之间切换的时间点可能很有用。例如,arbiter 可以被设计为在burst 传输边界改变总线所有权。

- 为什么在AHB中有一个1KB边界的限制?

1KB边界限制在AHB中表示burst传输不能跨越1KB边界的约束。 该限制旨在防止burst传输从一个slave交叉到另一个slave。在实践中,这意味着如果master必须要进行跨1KB边界的burst传输则必须切分成两次传输。例如:

0x3F00 x3F40 x3F80 x3FC0 x4000 x4040 x4080

这种1KB地址边界地址传输需要划分成

NSEQ SEQ SEQ SEQ NSEQ SEQ SEQ

- 举例说明什么是Wrap 边界 ? WRAP4,WRAP8,WRAP16 ?

Wrap边界取决于Hsize和burst beat的数量(4,8,16)

Case1: Start Address is 0x4,Wrap4,Hsize is 2.

beat1 - 0x4

beat2 - 0x8

beat3 - 0xc

beat4 - 0x0

Hsize为2,意味着一次传输4字节。Wrap4 意味着一次burst共4拍,并且总的传输字节为16(beats*Hsize)字节。如果起始地址从0x4开始,则在0x10处wrap

Case2: Start Address is 0x4,Wrap4,Hsize is 1.

beat1 - 0x4

beat2 - 0x6

beat3 - 0x0

beat4 - 0x2

Hsize为1,意味着一次传输2字节。Wrap4 意味着一次burst共4拍,并且总的传输字节为8(beats*Hsize)字节。如果起始地址从0x4开始,则在0x8处wrap

Case3: Start Address is 0x4,Wrap8,Hsize is 1.

beat1 - 0x4

beat2 - 0x6

beat3 - 0x8

beat4 - 0xa

beat5 - 0xc

beat6 - 0xe

beat7 - 0x0

beat8 - 0x2

Hsize为1,意味着一次传输2字节。Wrap8 意味着一次burst共8拍,并且总的传输字节为16(beats*Hsize)字节。如果起始地址从0x4开始,则在0x10处wrap。

828

828

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?