名称:电子数字钟设计Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

要求

电子数字钟设计

1、可以按键切换正常计时和闹钟

2、可以通过按键修改时分秒

3、可以通过按键修改闹钟时间

4、数码管显示时间

使用方法:一共4个控制按键,F1~F4,F1为模式设置按键,通过这个按键可以设置当然显示的是闹钟时间还是实际计时时间,F2是修改时间按键,修改方法为,先按下F2,再按F4修改小时,修改后按下F3确认,再按F4修改分钟,修改后按下F3确认,再按F4修改秒钟,修改后按下F3确认就推出修改模式了。闹钟时间修改也是一样,就是先按F1切换到闹钟显示,再修改。闹钟响时,按下F4关闭。

F1,//模式设置按键--4'd0:计时,4'd1:闹钟

F2,//设置修改

F3,//修改确认

F4,//修改时分秒,闹钟关闭

使用方法:一共4个控制按键,F1~F4,F1为模式设置按键,通过这个按键可以设置当然显示的是闹钟时间还是实际计时时间,F2是修改时间按键,修改方法为,先按下F2,再按F4修改小时,修改后按下F3确认,再按F4修改分钟,修改后按下F3确认,再按F4修改秒钟,修改后按下F3确认就推出修改模式了。闹钟时间修改也是一样,就是先按F1切换到闹钟显示,再修改。闹钟响时,按下F4关闭。

1. 工程文件

2. 程序文件

数码管显示模块

按键消抖模块

3. 程序编译

4. 管脚分配

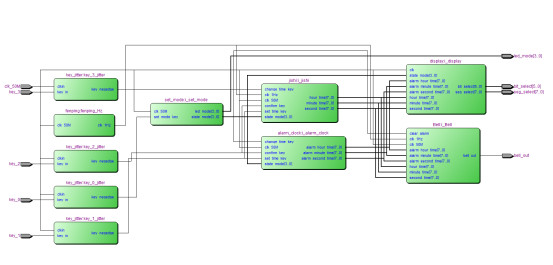

5. RTL图

6. 模块说明

包括按键消抖模块用于按键消抖、模式设置模块用于切换闹钟时间和计时时间、计时模块用于计时及设置时间,闹钟模块用于设置闹钟、显示模块用于控制数码管显示、闹铃模块用于整点报时和闹钟响铃。

部分代码展示:

module Digital_clock( input clk_50M, input key_0,//模式设置按键--4'd0:计时,4'd1:闹钟 input key_1,//设置修改 input key_2,//修改确认 input key_3,//修改时分秒,闹钟关闭 output [2:0] led_jishi_time, output [2:0] led_alarm_time, output bell_out,//闹钟 output [3:0] led_mode,//led显示当前模式 output [5:0] bit_select,//数码管位选 output [7:0] seg_select//数码管段选 ); wire [3:0] state_mode;//当前模式,4'd0:计时,4'd1:闹钟 wire [7:0] hour_time;//时 wire [7:0] minute_time;//分 wire [7:0] second_time;//秒 wire [7:0] alarm_hour_time;//闹钟时 wire [7:0] alarm_minute_time;//闹钟分 wire [7:0] alarm_second_time;//闹钟秒 wire key_0_negedge; wire key_1_negedge; wire key_2_negedge; wire key_3_negedge; wire clk_1Hz; wire clk_100Hz; //分频模块 fenping fenping_Hz( . clk_50M(clk_50M), . clk_1Hz(clk_1Hz) ); //按键消抖 key_jitter key_0_jitter( . clkin(clk_50M), . key_in(key_0), . key_posedge(), . key_negedge(key_0_negedge), . key_value() ); //按键消抖 key_jitter key_1_jitter( . clkin(clk_50M), . key_in(key_1), . key_posedge(), . key_negedge(key_1_negedge), . key_value() ); //按键消抖 key_jitter key_2_jitter( . clkin(clk_50M), . key_in(key_2), . key_posedge(), . key_negedge(key_2_negedge), . key_value() ); //按键消抖 key_jitter key_3_jitter( . clkin(clk_50M), . key_in(key_3), . key_posedge(), . key_negedge(key_3_negedge), . key_value() ); //模式设置 set_mode i_set_mode( . clk_50M(clk_50M), . set_mode_key(key_0_negedge), . led_mode(led_mode),//led显示当前模式 . state_mode(state_mode)//当前模式,4'd0:计时,4'd1:闹钟 ); //计时 jishi i_jishi( . clk_50M(clk_50M), . clk_1Hz(clk_1Hz), . state_mode(state_mode),//当前模式,4'd0:计时,4'd1:闹钟 . set_time_key(key_1_negedge),//设置时间 . confirm_key(key_2_negedge),//确认 . change_time_key(key_3_negedge),//设置时分秒 . led_jishi_time(led_jishi_time), . hour_time(hour_time),//时 . minute_time(minute_time),//分 . second_time(second_time)//秒 ); //闹钟设置 alarm_clock i_alarm_clock( . clk_50M(clk_50M), . state_mode(state_mode),//当前模式,4'd0:计时,4'd1:闹钟 . set_time_key(key_1_negedge),//设置时间 . confirm_key(key_2_negedge),//确认 . change_time_key(key_3_negedge),//设置时分秒 . led_alarm_time(led_alarm_time), . alarm_hour_time(alarm_hour_time),//时 . alarm_minute_time(alarm_minute_time),//分 . alarm_second_time(alarm_second_time)//秒 ); //响铃 Bell i_Bell( . clk_50M(clk_50M), . clk_1Hz(clk_1Hz), . clear_alarm(key_3_negedge),//关闭闹钟键(key3) . alarm_hour_time(alarm_hour_time),//闹钟时 . alarm_minute_time(alarm_minute_time),//闹钟分 . alarm_second_time(alarm_second_time),//闹钟秒 . hour_time(hour_time),//时 . minute_time(minute_time),//分 . second_time(second_time),//秒 . bell_out(bell_out)//蜂鸣器,为低电平时,蜂鸣器响 ); //数码管显示 display i_display( . clk(clk_50M), . state_mode(state_mode),//当前模式,4'd0:计时,4'd1:闹钟 . hour_time(hour_time),//时 . minute_time(minute_time),//分 . second_time(second_time),//秒 . alarm_hour_time(alarm_hour_time),//闹钟时 . alarm_minute_time(alarm_minute_time),//闹钟分 . alarm_second_time(alarm_second_time),//闹钟秒 . bit_select(bit_select),//数码管位选 . seg_select(seg_select)//数码管段选 ); endmodule

源代码

扫描文章末尾的公众号二维码

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?