名称:基于DDS和PLL组合的波形发生器Verilog代码Quartus DE1-SoC板子(文末获取)

软件:Quartus

语言:Verilog

代码功能:基于DDS和PLL组合的波形发生器:利用DDS和PLL(锁相环,调IP核)实现输出频率在一定范围内连续可调的信号发生器

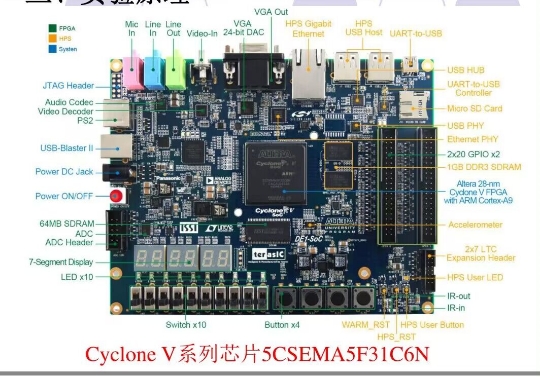

本代码已在DE1-SoC板子验证,DE1-SoC板子如下,其他开发板可以修改管脚适配:

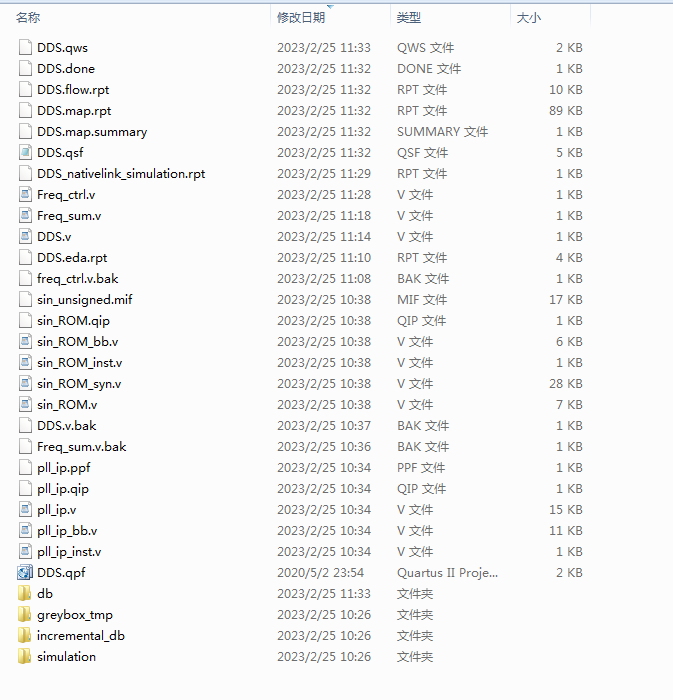

1. 工程文件

2. 程序文件

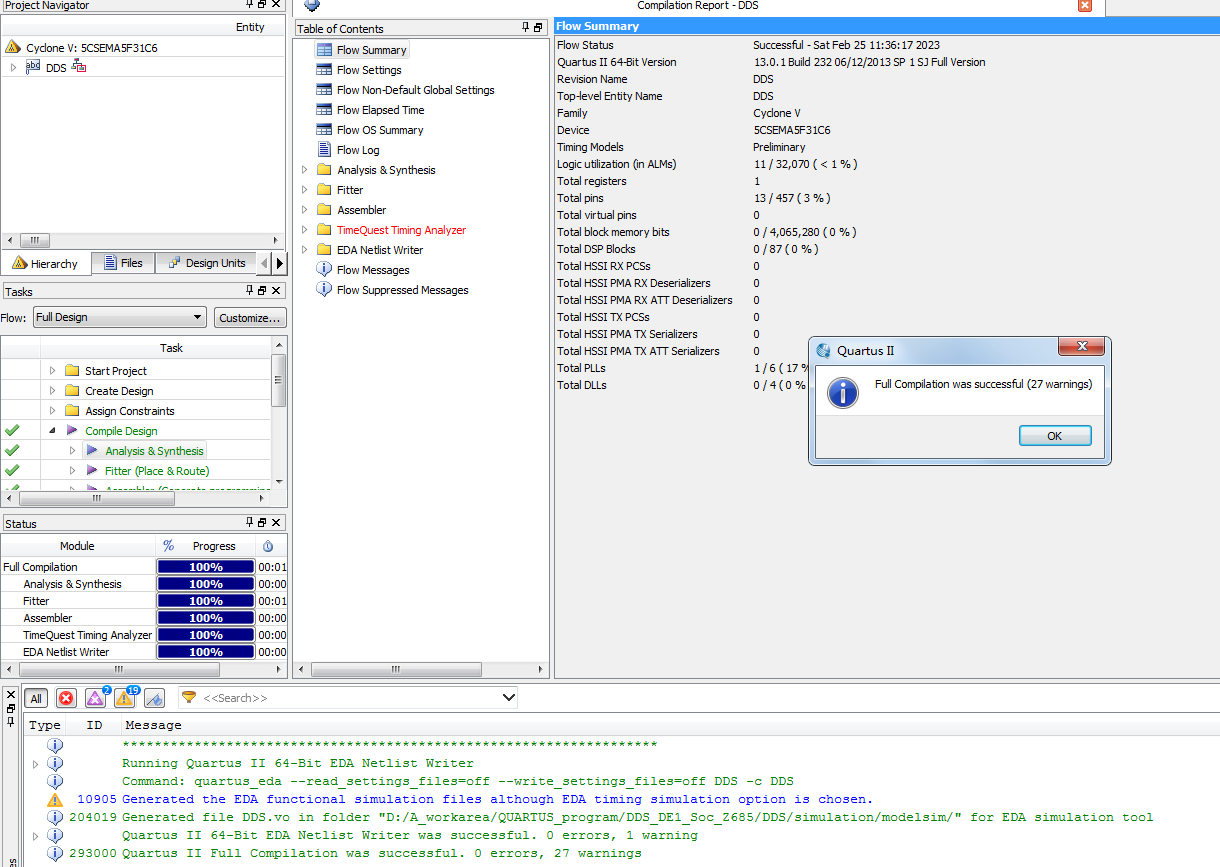

3. 程序编译

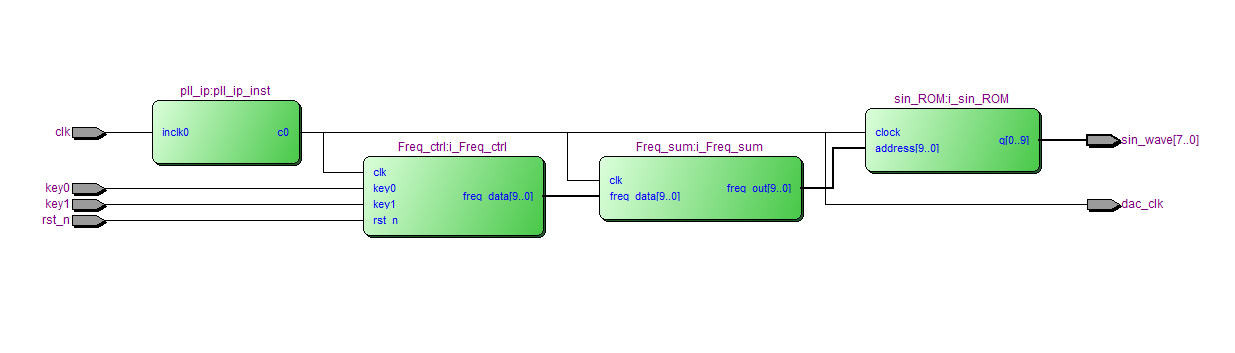

4. RTL图

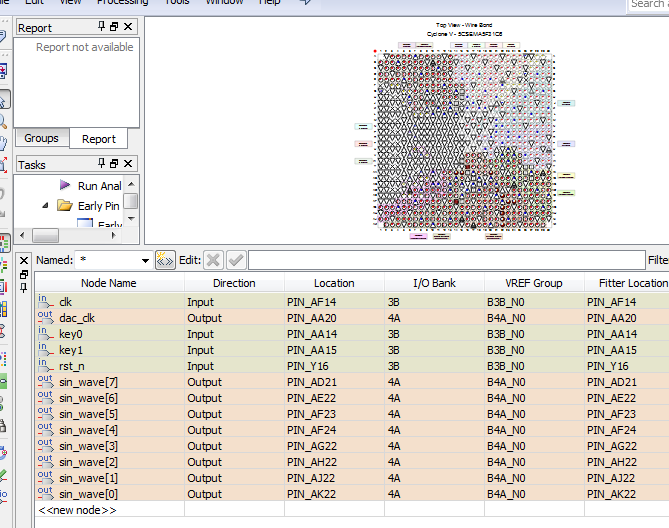

5. 管脚分配

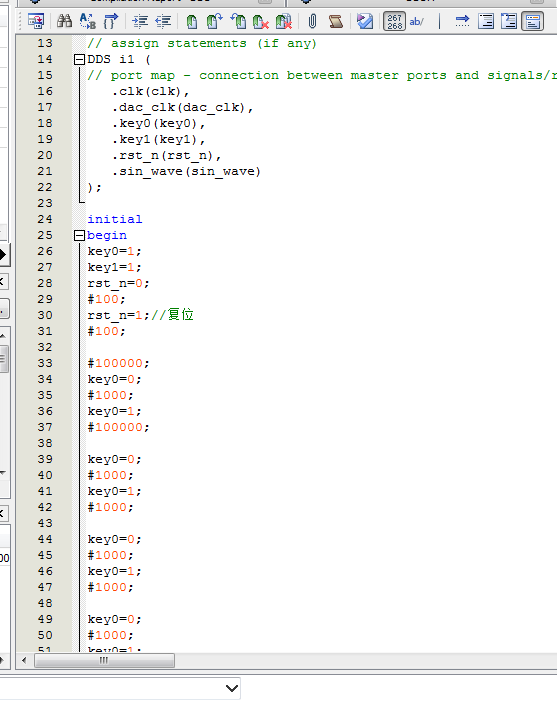

6. Testbench

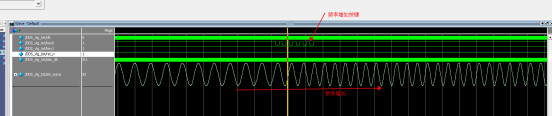

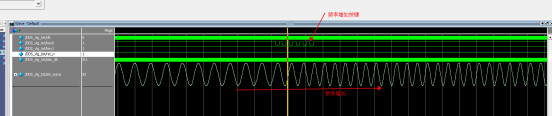

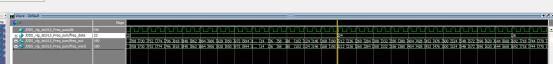

7. 仿真图

整体仿真图

PLL模块

频率控制模块

正弦波ROM表

相位累加器模块

部分代码展示:

module DDS( input clk,//时钟50M input rst_n,//复位 input key0,//频率增加 input key1,//频率减小 output dac_clk,//DA时钟 output [7:0] sin_wave//输出波形 ); wire clk_10M; wire [9:0] address; wire [9:0] q;//输出波形 assign dac_clk=clk_10M; wire [9:0] freq_data;//频率控制字10bit //PLL_ip 50M->10M pll_ippll_ip_inst ( .inclk0 ( clk ),//输入50M .c0 ( clk_10M )//输出10M ); //频率控制模块 Freq_ctrl i_Freq_ctrl( . clk(clk_10M), . rst_n(rst_n),//复位 . key0(key0),//频率增加 . key1(key1),//频率减小 . freq_data(freq_data)//频率控制字9bit ); //sin存储Rom表 sin_ROM i_sin_ROM ( .address(address),//查找表地址 .clock(clk_10M),//时钟 .q(q)//输出波形 ); //相位累加器 Freq_sum i_Freq_sum( . clk(clk_10M), . rst_n(rst_n), . freq_data(freq_data),//频率控制字32bit . freq_out(address)//累加器输出 ); assign sin_wave=q[9:2];//输出最终波形 endmodule

源代码

扫描文章末尾的公众号二维码

5705

5705

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?