名称:自动打铃控制系统设计VHDL代码Quartus 实验箱(文末获取)

软件:Quartus

语言:VHDL

代码功能:

自动打铃控制系统设计

要求:根据学校打铃系统设计,打第一个上课铃后,隔45分钟打一次下课休息铃,5分钟后再打一次上课铃,再隔45分钟后打下课铃

包括总体电路、各模块设计和相应模块的VHDL程序,系统框图,仿真图,引脚锁定,最

终需要上开发板调试。

本代码已在实验箱验证,实验箱如下,其他实验箱可以修改管脚适配:

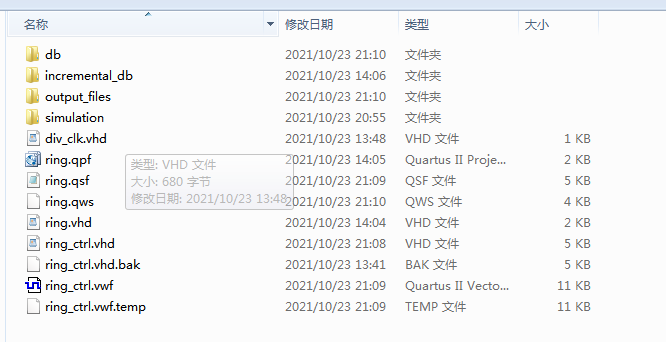

1. 工程文件

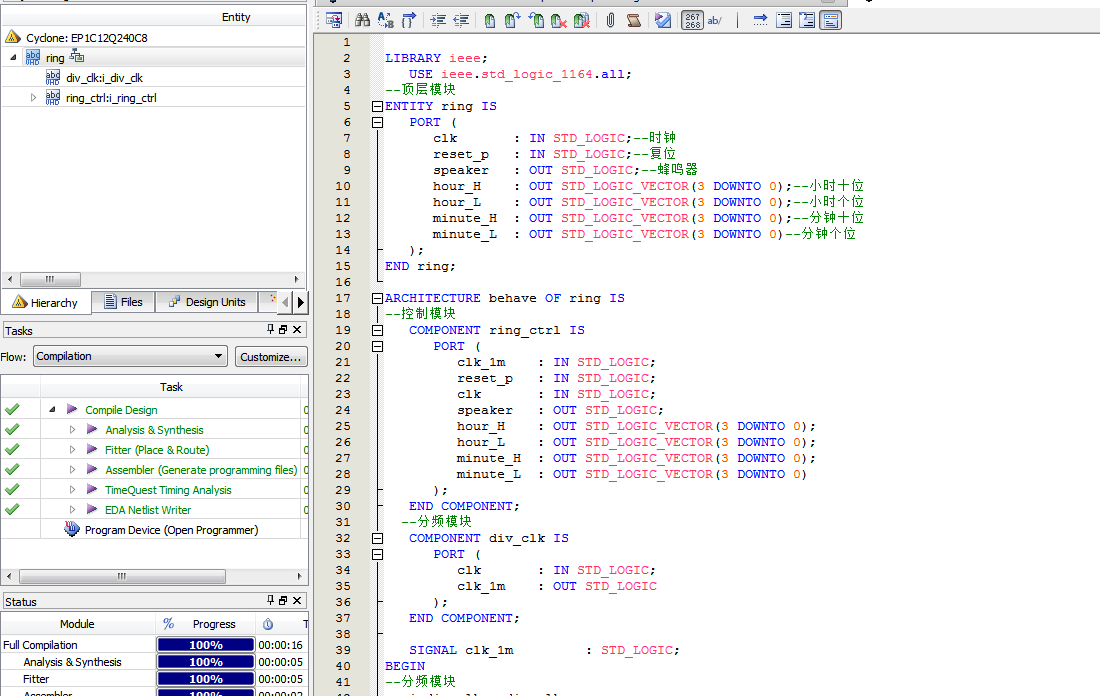

2. 程序文件

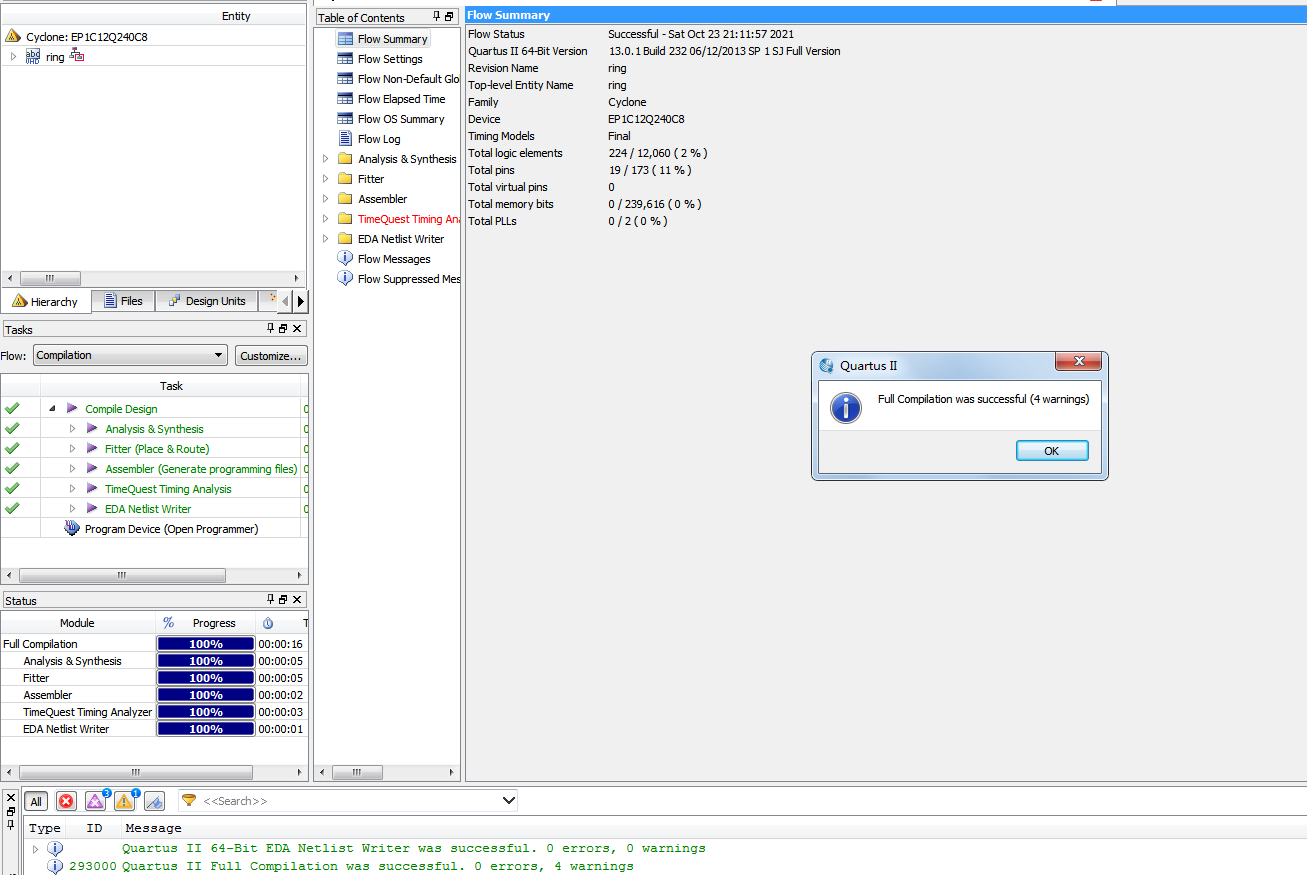

3. 程序编译

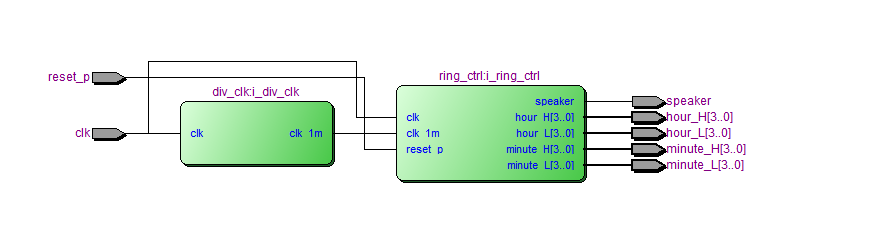

4. RTL图

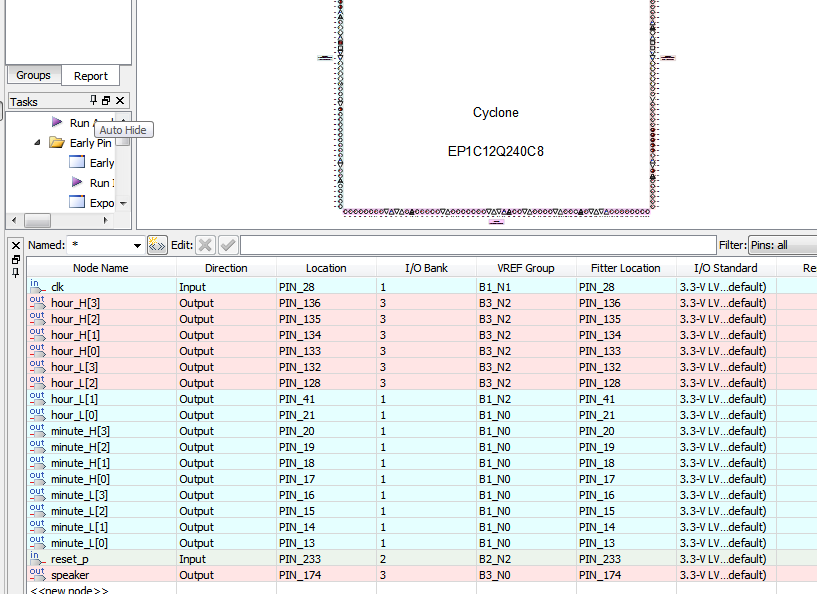

5. 管脚分配

6. 仿真图

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; --顶层模块 ENTITY ring IS PORT ( clk : IN STD_LOGIC;--时钟 reset_p : IN STD_LOGIC;--复位 speaker : OUT STD_LOGIC;--蜂鸣器 hour_H : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--小时十位 hour_L : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--小时个位 minute_H : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--分钟十位 minute_L : OUT STD_LOGIC_VECTOR(3 DOWNTO 0)--分钟个位 ); END ring; ARCHITECTURE behave OF ring IS --控制模块 COMPONENT ring_ctrl IS PORT ( clk_1m : IN STD_LOGIC; reset_p : IN STD_LOGIC; clk : IN STD_LOGIC; speaker : OUT STD_LOGIC; hour_H : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); hour_L : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); minute_H : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); minute_L : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ); END COMPONENT; --分频模块 COMPONENT div_clk IS PORT ( clk : IN STD_LOGIC; clk_1m : OUT STD_LOGIC ); END COMPONENT; SIGNAL clk_1m : STD_LOGIC; BEGIN --分频模块 i_div_clk : div_clk PORT MAP ( clk => clk, clk_1m => clk_1m ); --控制模块 i_ring_ctrl : ring_ctrl PORT MAP ( clk_1m => clk_1m, reset_p => reset_p, clk => clk, speaker => speaker, hour_H => hour_H, hour_L => hour_L, minute_H => minute_H, minute_L => minute_L ); END behave;

源代码

扫描文章末尾的公众号二维码

本文详细描述了一个自动打铃控制系统的设计过程,采用VHDL编程在Quartus环境中实现,包括分频模块和控制模块的实现,以及如何根据学校作息时间间隔进行铃声控制。最终代码在实验箱上进行了验证和调试。

本文详细描述了一个自动打铃控制系统的设计过程,采用VHDL编程在Quartus环境中实现,包括分频模块和控制模块的实现,以及如何根据学校作息时间间隔进行铃声控制。最终代码在实验箱上进行了验证和调试。

4056

4056

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?