名称:抢答器设计Verilog代码VIVADO仿真(文末获取)

软件:VIVADO

语言:Verilog

代码功能:

抢答器

设计要求:三人参賽每人一个按钮,主持人一个按钮,按下就开始;

每人一个发光二极管,抢中者灯亮;有人抢答时,显示器显示其序号两秒;

答题时限为10秒钟,从有人抢答开始,用数码管倒计时间,10、9、8..1、0;倒计时到0的时候,然后显示四个0两秒。

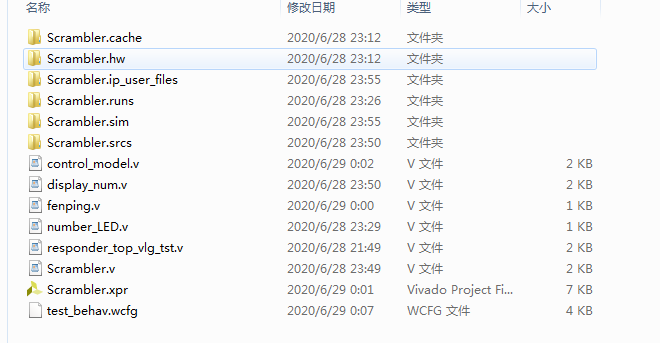

1. 工程文件

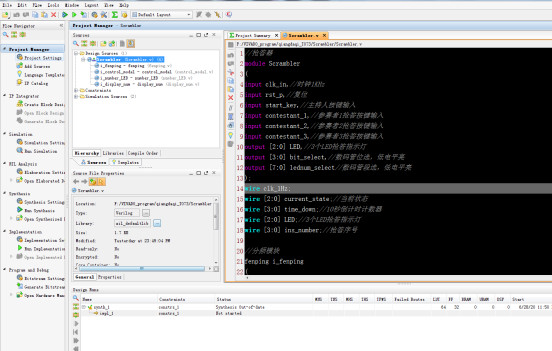

2. 程序文件

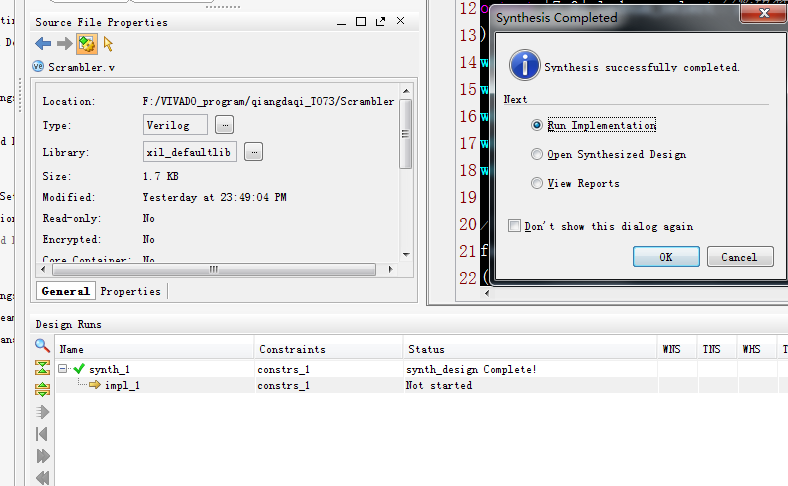

3. 程序编译

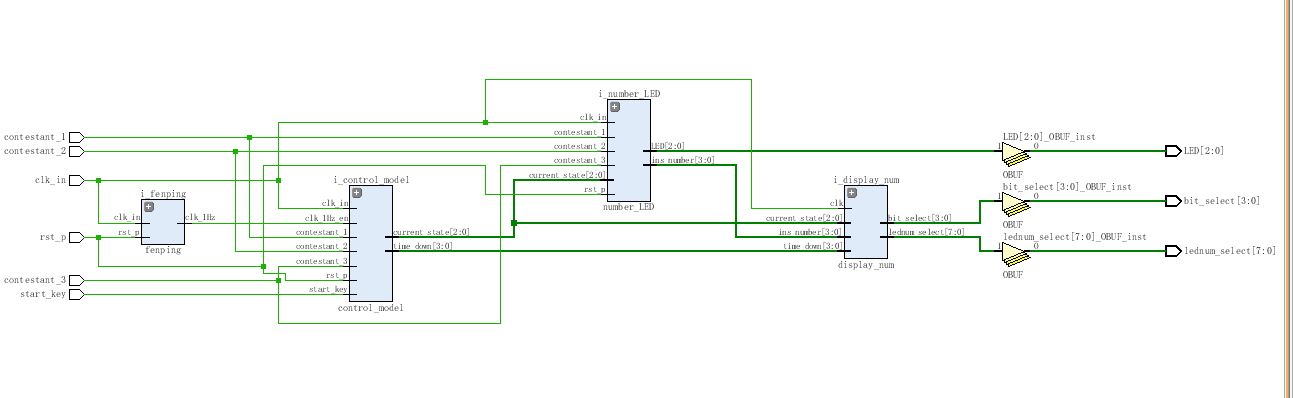

4. RTL图

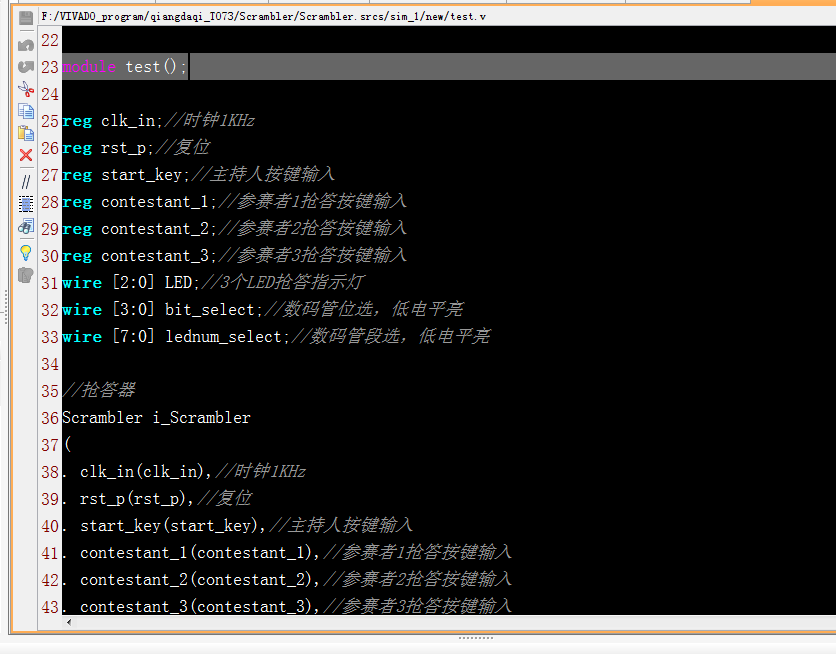

5. Testbench

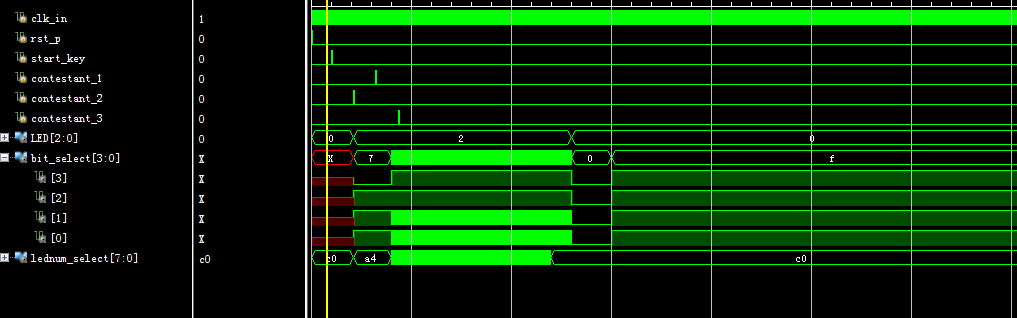

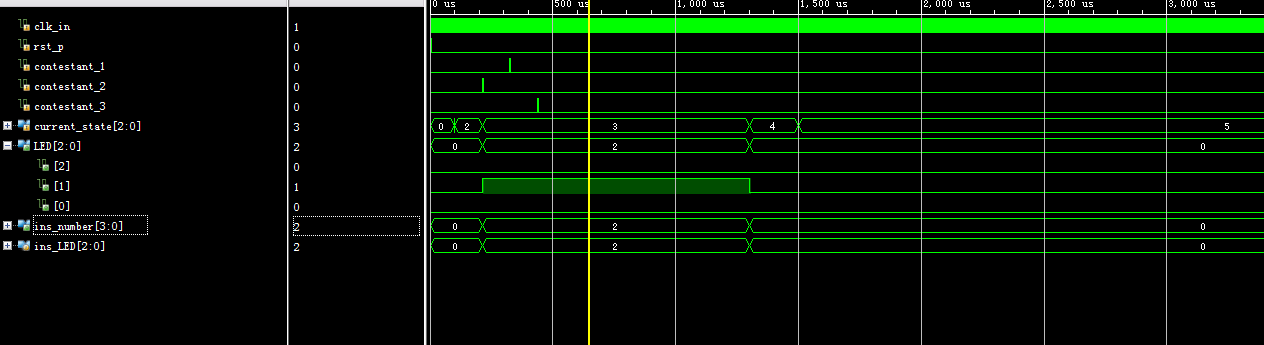

6. 仿真图

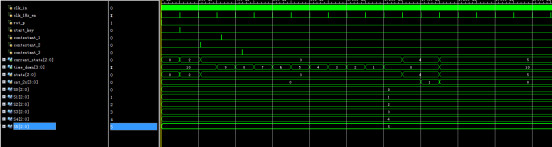

整体仿真图

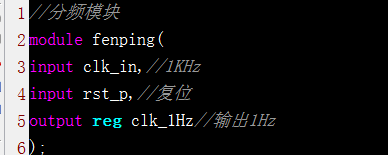

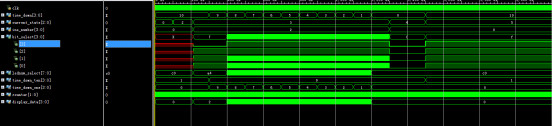

分频模块仿真

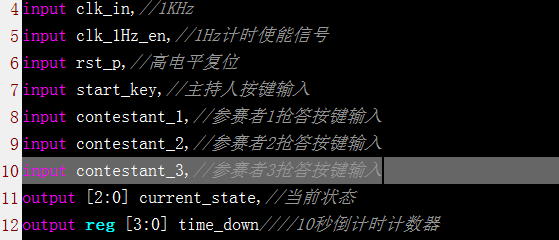

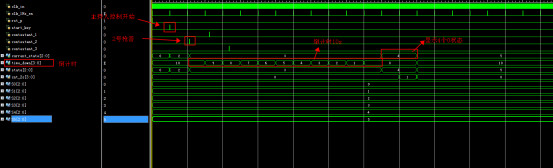

控制模块仿真

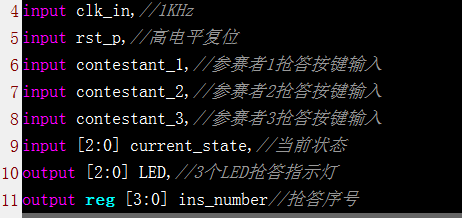

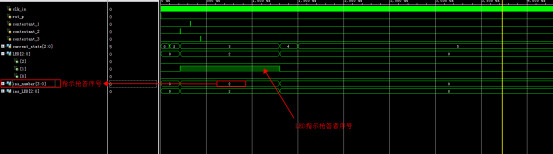

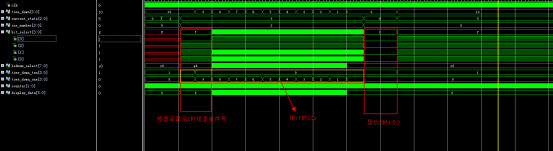

输出抢答者序号及LED显示模块

显示模块

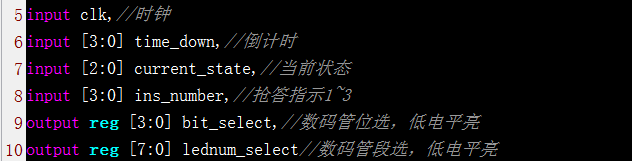

部分代码展示:

`timescale 1ns / 1ps //显示模块 module display_num( input clk,//时钟 input [3:0] time_down,//倒计时 input [2:0] current_state,//当前状态 input [3:0] ins_number,//抢答指示1~3 output reg [3:0] bit_select,//数码管位选,低电平亮 output reg [7:0] lednum_select//数码管段选,低电平亮 ); wire [3:0] time_down_ten; wire [3:0] time_down_one; assign time_down_ten=time_down/10;//倒计时十位 assign time_down_one=time_down%10;//倒计时个位 reg[1:0]counter='d0; always@(posedge clk) begin counter<=counter+2'd1;//计数 end reg [3:0] display_data=4'd0; always@(*) begin 显示抢答者号2秒 if(current_state==3'd3 && time_down>8)begin//倒计时状态(S3)且还没倒计时到8 display_data<=ins_number;//抢答指示1~3 bit_select<=4'b0111;//数码管位选,第一个数码管显示 end else if(current_state==3'd4)begin显示4个0,2秒 display_data<=4'd0;//抢答指示1~3 bit_select<=4'b0000;//数码管位选,4个1数码管显示 end else if(current_state==3'd5)begin//结束,不显示 display_data<=4'd0;//抢答指示1~3 bit_select<=4'b1111;//数码管位选,4个1数码管都不显示 end else if(current_state==3'd3)//倒计时状态 case(counter)// 2'd0:begin display_data<=4'd0;bit_select<=4'b1111;end//不显示 2'd1:begin display_data<=4'd0;bit_select<=4'b1111;end//不显示 2'd2:begin display_data<=time_down_ten;bit_select<=4'b1101;end//倒计时十位

源代码

扫描文章末尾的公众号二维码

1047

1047

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?