名称:基于FPGA的表决器和计数器Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

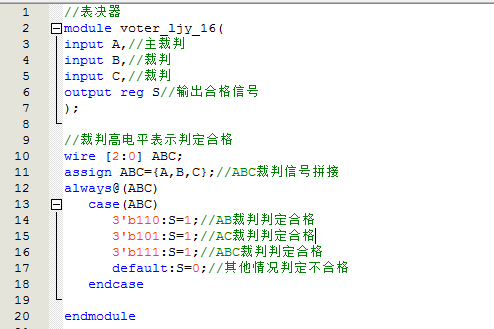

三人表决器

在举重比赛举中,有A,B,C三名裁判,A为主裁判,当两名以上裁判(必须包括A在内)

按动按钮判定运动员上举杠铃合格,才可发出裁决合格信号

X进制的计数器

现有一100HZ的矩形波,作为计数器的输入端,设计一个具有复位功能的X进制的计数器

(X=座号%10+5),该计数器每一秒钟加1。

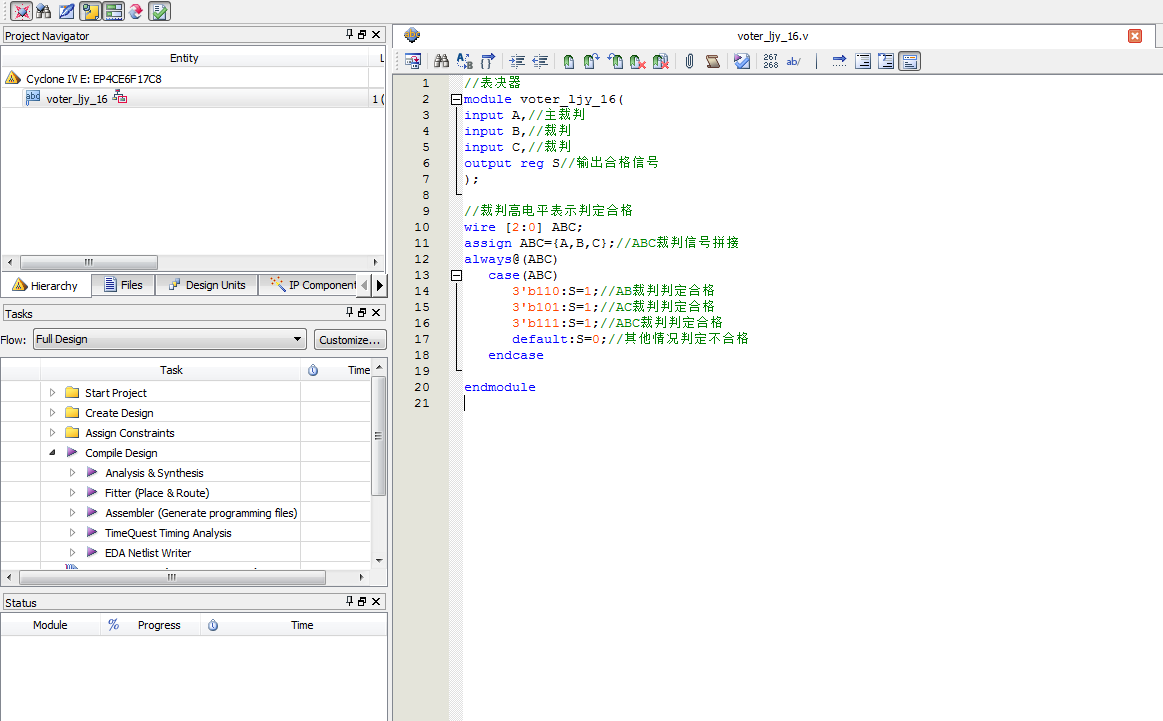

表决器

1. 设计文件(程序文件)

2. 工程文件

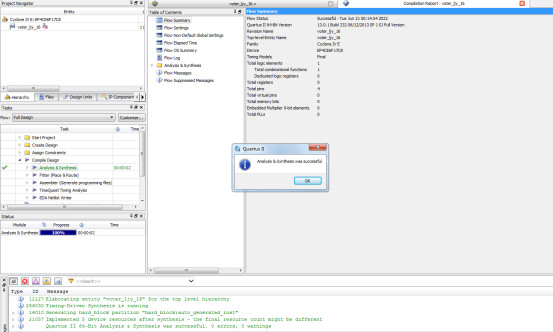

3. 程序编译

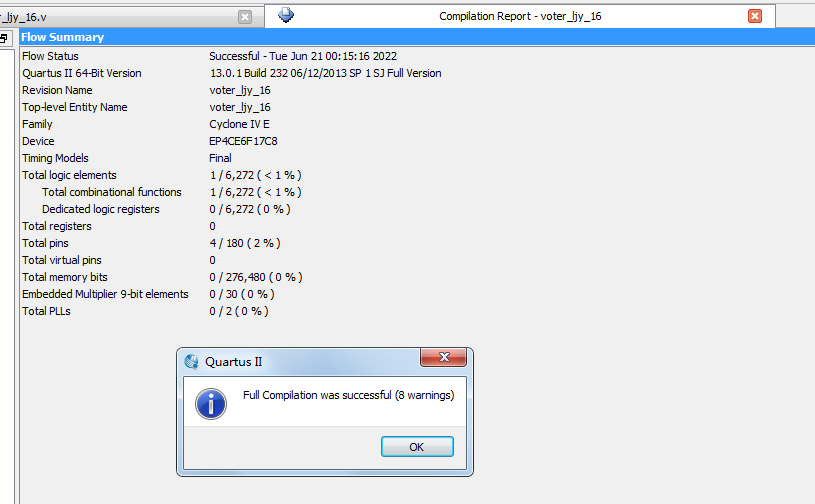

4. 综合报告

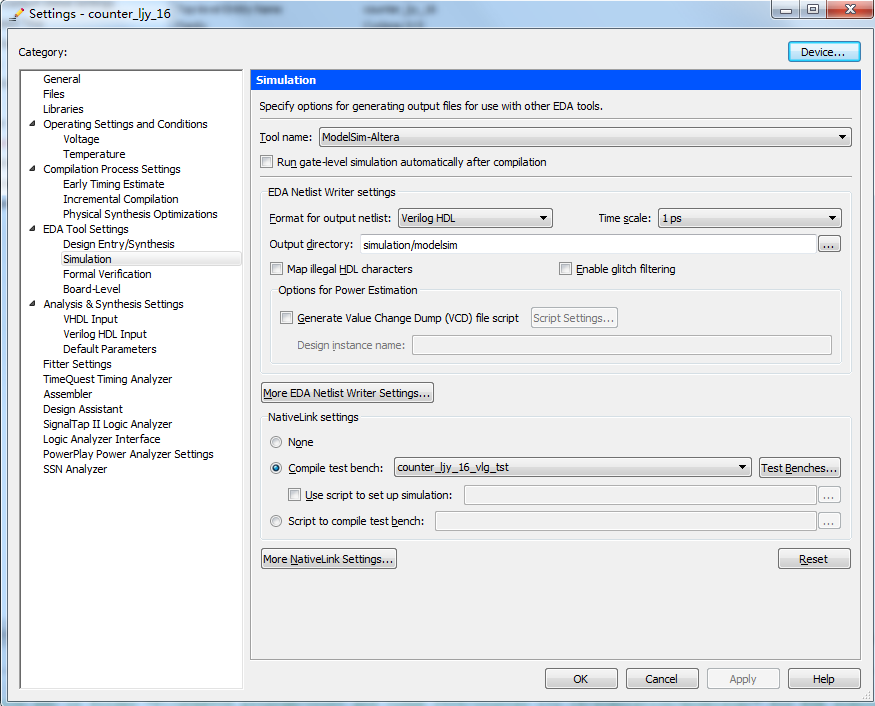

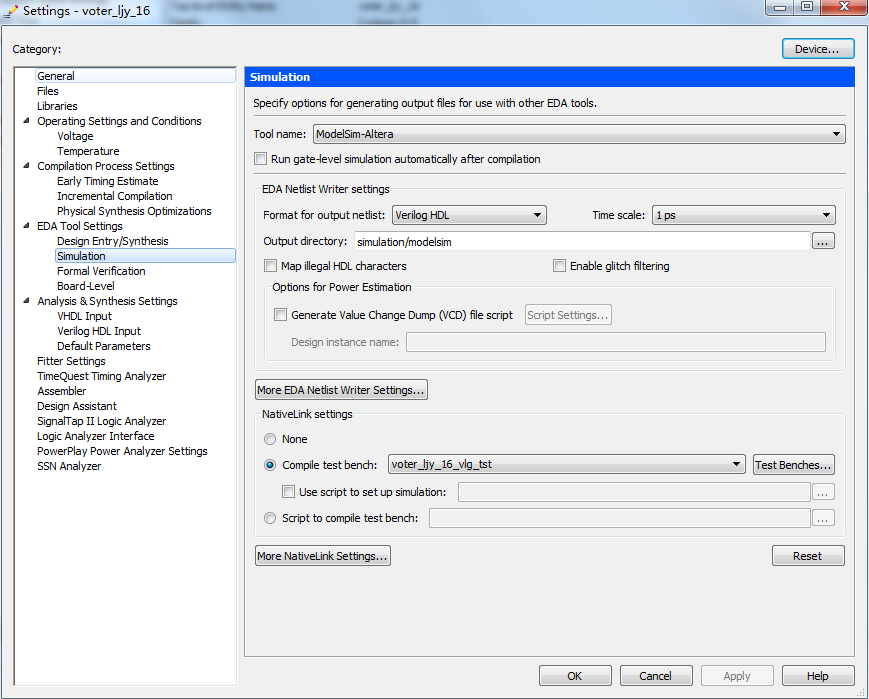

5. Quartus-modelsim联合仿真设置

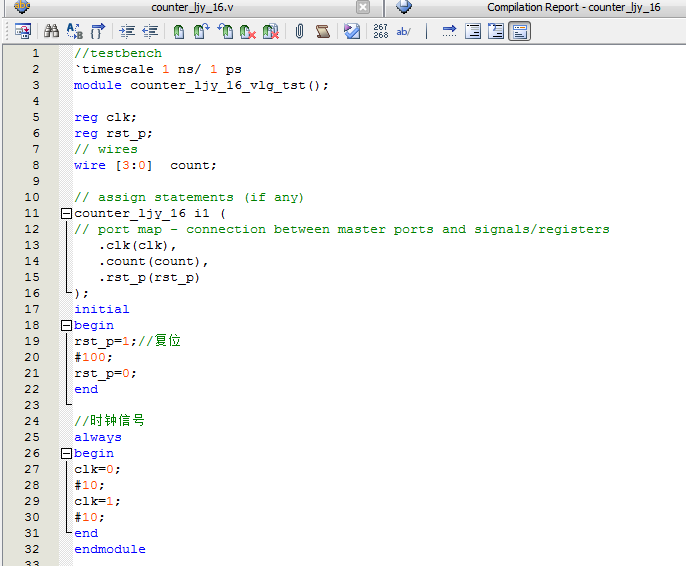

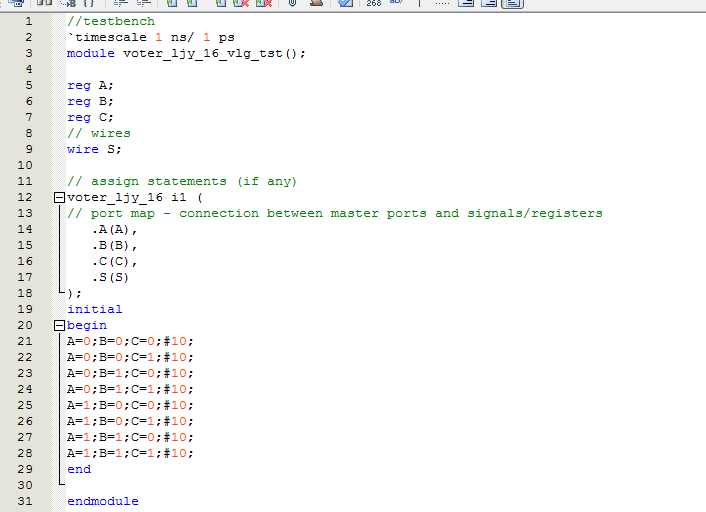

Testbench

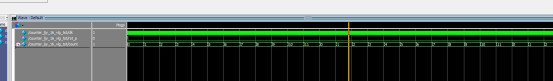

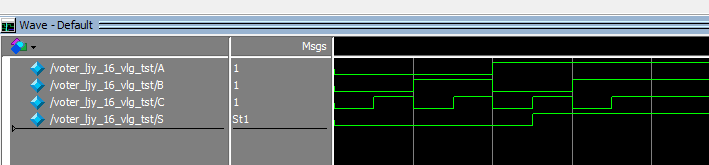

6. 仿真图

表决器

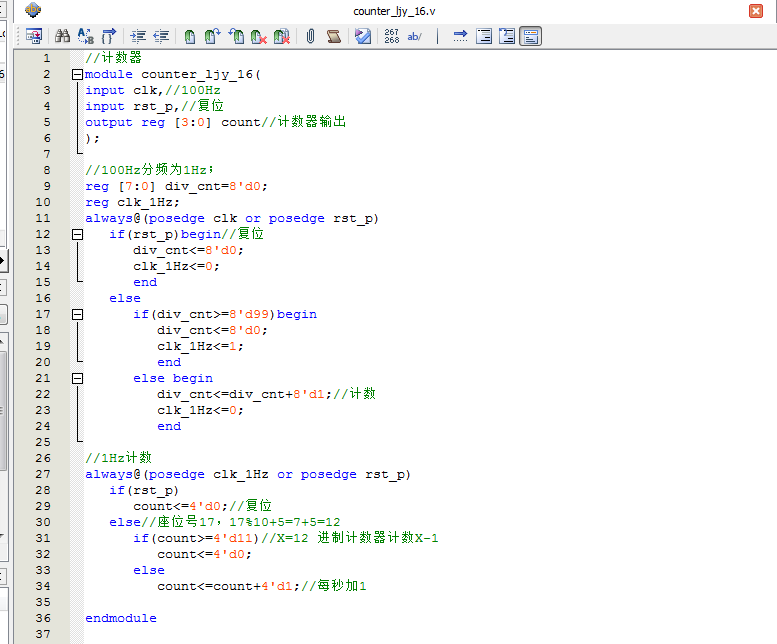

1. 设计文件(程序文件)

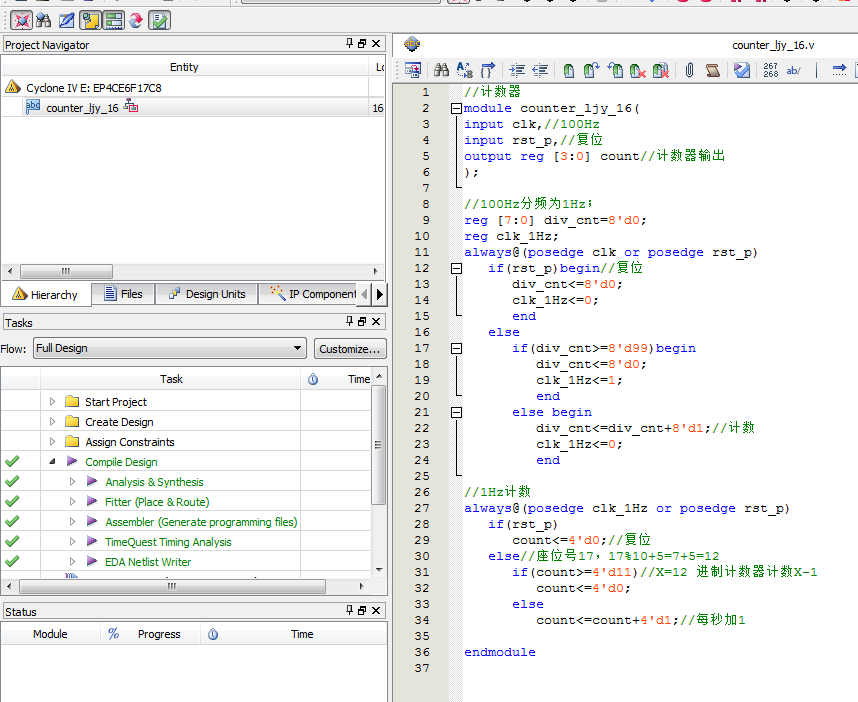

2. 工程文件

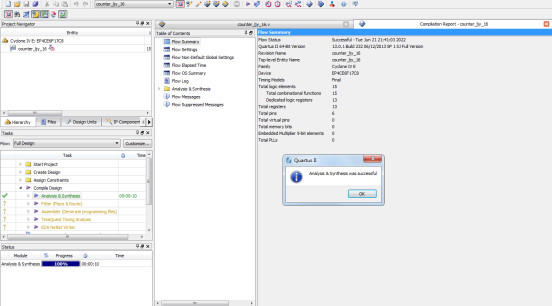

3. 程序编译

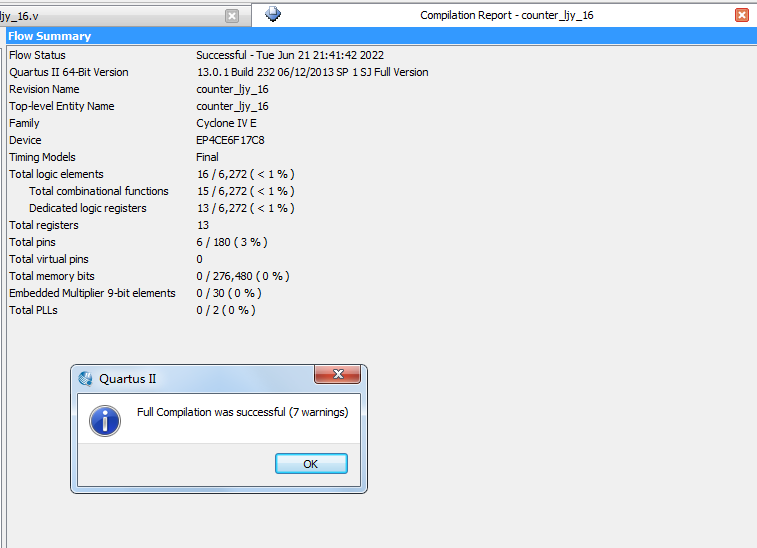

4. 综合报告

5. Quartus-modelsim联合仿真设置

Testbench

6. 仿真图

部分代码展示:

//计数器 module counter_ljy_16( input clk,//100Hz input rst_p,//复位 output reg [3:0] count//计数器输出 ); //100Hz分频为1Hz; reg [7:0] div_cnt=8'd0; reg clk_1Hz; always@(posedge clk or posedge rst_p) if(rst_p)begin//复位 div_cnt<=8'd0; clk_1Hz<=0; end else if(div_cnt>=8'd99)begin div_cnt<=8'd0; clk_1Hz<=1; end else begin div_cnt<=div_cnt+8'd1;//计数 clk_1Hz<=0; end

源代码

扫描文章末尾的公众号二维码

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?